电子说

S/R锁存器

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

使用两个NOR逻辑门进行S/R锁存。

两个输入S和R可用于设置和复位锁存器。设置锁存器相当于存储二进制锁存器。输出Q将变为高电平,反相输出Q将被拉低。重置具有相反的效果。当两个输入均为低电平时,保持当前状态。

此电路的简单性是有代价的:可能会发生一些会导致不确定行为的事情(电路的下一个状态将是未定义的) )或所谓的临界竞争,其中锁存器将永远保持设置和复位。

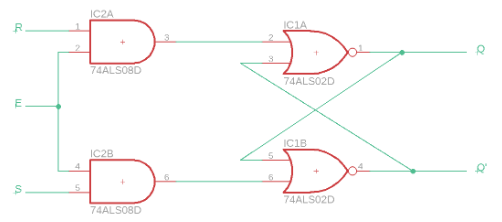

添加两个AND门将把简单锁存器转换为带有额外使能输入的门控锁存器。此方法可用于控制何时锁存数据。没有它,只要锁存器被置位或复位,数据就会(理论上)出现在输出端。

将两个AND门添加到一个简单的锁存器以形成一个门控锁存器。

D-Latch

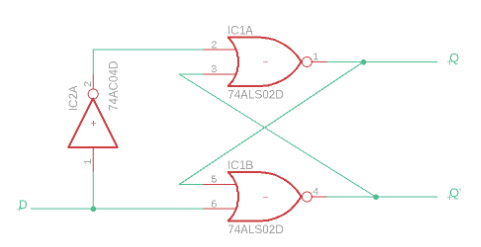

这种类型的锁存器使用R/S锁存器和为电路增加一个逆变器。这样做可以防止上面描述的关键竞争,使闩锁更容易使用。

使用两个NOR门和一个NOT门的D锁存电路。

如您所见,此锁存器只有一个输入。存在于D的数据将被锁存和存储。请注意,上图代表了锁存器的核心。这种设计在实际应用中是无用的,因为输入一改变就会改变输出。

实际上,锁存器具有启用它们的输入,并且数据仅在启用时被锁存。为简单起见,我省略了启用输入。

D触发器和S/R触发器

启用锁存器时,它们是透明的。这意味着输出将具有与输入相同的状态。但是,有些情况下,仅在信号的上升沿或下降沿使输出发生变化更为有用。例如,使用周期性时钟信号。

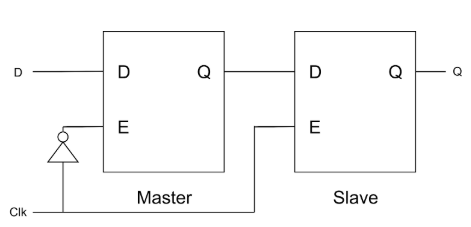

Flips-flops通过串联使用两个锁存器实现输出变化。第一阶段通常称为主(锁存器),第二阶段是从属:

这是一个正逻辑,正边沿触发D触发器。

可以通过用S/R锁存器替换D锁存器来构造S/R触发器。然而,当两个输入都被置位时,这样的触发器,就像上面的锁存器一样,可能进入未定义状态。解决这个问题的一种方法是使用JK触发器。

JK触发器

JK触发器与S/R触发器非常相似。它有一个J输入,其作用类似于S输入和K输入,用于复位电路。然而,当两者同时被置位(正逻辑高电平,负电平低电平)时,触发器不会进入未定义状态,而是切换其状态。

复查锁存器和触发器

锁存器是存储器的最小构建块。它们用于其他电路,如触发器和移位寄存器,只要它们被启用,它们就会将输入应用于它们的输出。触发器是边沿触发的,只有在启用和触发时才会改变它们的状态。有几种基本类型的锁存器和触发器,每种都适用于某些应用。

全部0条评论

快来发表一下你的评论吧 !