接口/总线/驱动

在分析某型飞机MILSTD1553B数据总线系统构成的基础上,结合其通信协议与其消息传输格式,建立了某型飞机总线系统通讯层次结构,并运用FPGA和DSP技术设计了此型飞机总线系统通讯软件。

目前,随着工艺和技术的进步,集成电路技术的发展已经使得在一个芯片上集成一个可编程系统(Programmable System ON a Chip,PSOC)成为可能。其中,现场可编程门阵列(Field Programmable Gate Array,FPGA)由于其设计灵活、速度快,在数学专用集成电路的设计中得到广泛的应用。数字信号处理(DSP)的理论与实现手段获得了快速发展,已成为当代发展最快的学科之一。由于其高速的处理速度和强大而又灵活的接口与通信能力,在很多领域已经得到了广泛的应用。

MILSTD1553B数据总线具有双向输出特性,实时性和可靠性高,广泛应用在当代的运输机和相当数量的民航客机以及军用飞机上。

1 、1553B数据总线系统构成

1553B总线系统主要由3部分组成:总线控制器BC;远程终端RT;数据总线D ata Bus。

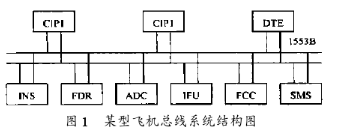

某飞机的总线系统构成如图1所示。

图中CIP1为BC,CIP2为CIP1备份,其他子系统都是RT,并且此总线系统是双余度的,两套总线互为备份。

CIP1为通信和信息处理系统;CIP2为通信和信息处理系统备份;DTE为数据传输设备;INS为惯性导航系统;FDR为飞行参数记录系统;ADC为大气数据计算机;IFU为接口组件;FCC为火控计算机;SMS为外挂管理系统;LRS为激光测距系统。

2、 1553B数据总线通信协议

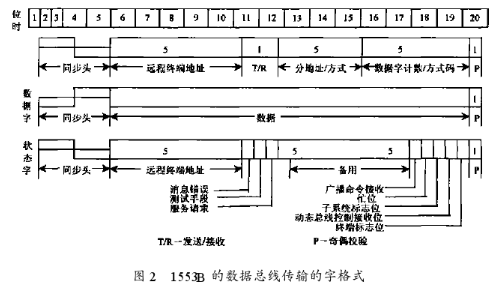

1553B总线的工作频率是1 Mb/s 。采用曼彻斯特II码,半双工工作方式。主要的硬件部分为总线控制器(BC)、远端终端(RT)和可选用的总线监控器(MT)。一般情况下,这3部分通过1个多路总线接口(MBI)来完成。可把MBI嵌在计算机内。该总线有10种消息格式。每个消息至少包含2个字,每个字有16个消息位,1个奇偶校验位和3个位长的同步头,所有的消息字都采用曼彻斯特II码构成。1553B的数据总线传输的字的格式如图2所示。

1553B数据总线用的是指令/响应型通信协议。他有3种类型的终端,分别为:

(1)总线控制器(BC)

他是在总线上惟一被安排为执行建立和启动数据传输任务的终端。

(2)远程终端(RT)

他是用户子系统到数据总线上的接口,他在BC的控制下提取数据或吸收数据。

(3)总线监控器(MT)

他“监控”总线上的信息传输,以完成对总线上的 数据源进行记录和分析,但他本身不参与总线的通信。

3 、1553B数据总线消息传输格式

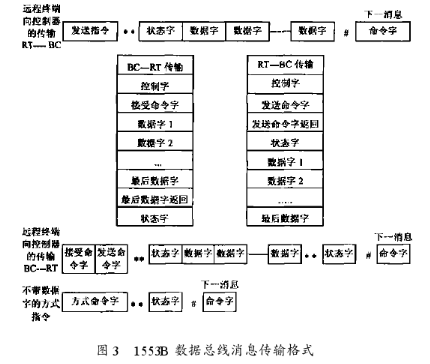

1553B总线上的信息的传递是以消息为单位的。所有的消息都是由数据字、指令字、状态字组成。下面是1553B协议允许的10种消息格式,如图3所示。

4 、某型飞机总线系统通讯层次结构

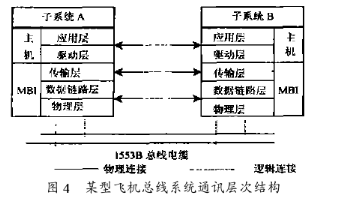

参考ISO的开放式互连系统七层模式,某型飞机机载系统分为5层:应用层、驱动层、传输层、数据链路层和物理层,如图4所示。

这5层之间功能划分明确,接口简单,从而为硬软 件的设计实现奠定良好的基础。应用层是通信系统的最高层次,他实现通信系统管理功能(如初始化、维护、重构等)和解释功能(如描述数据交换的含义、有效性、范围、格式等)。

驱动层是应用层与低层的软件接口。为实现应用层的管理功能,驱动层应能控制子系统内多 路传输总线接口(简称MBI)的初始化、启动、停止、连接、断开、启动其自测试,监控其工作状态,控制其和子系统主机的数据交换。

传输层控制多路传输总线上的数据传输,传输层的任务包括信息处理、通道切换、同步管理等。

数据链路层按照MILSTD1553B规定,控制总线上各条消息的传输序列。

物理层按照MILSTD1553B规定,处理1553B总线物理介质上的位流传输。

应用层、驱动层在各个子系统主机上实现,传输层、数据链路层、物理层在MBI上实现。

5 、总线系统通讯软件设计

在某型飞机航空总线系统的设计中,一个很重要的工作就是总线通讯软件的设计。航空总线通讯软件设计包括:驱动层和应用层的软件设计。其中驱动层直接驱动总线接口板主要完成各个寄存器的配置,实现数据的发送和接收;应用层是设计中的最高层,他管理整个系统的功能。作为一块接口板,设计的重点在于驱动层的软件的设计,他包括3个方面的内容:

(1)FPGA部分的软件。

(2)DSP部分的软件。

(3)上位机操作系统驱动软件。

5.1 FPGA程序控制功能

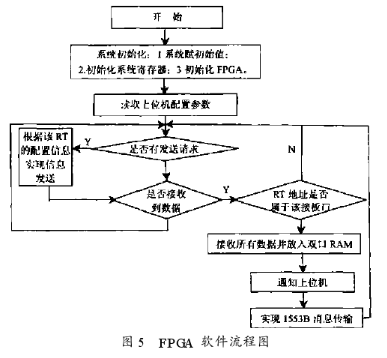

该部分采用VHDL语言编写,实现1553B总线数据的接收、发送、曼彻斯特II码、错误检出、奇偶检验、与DSP的接口和译码电路等功能。其中发送单元与接收单元是并行工作的,由逻辑门电路实现。这里从软件角度画出流程图如图5所示。

5.2 DSP程序控制功能

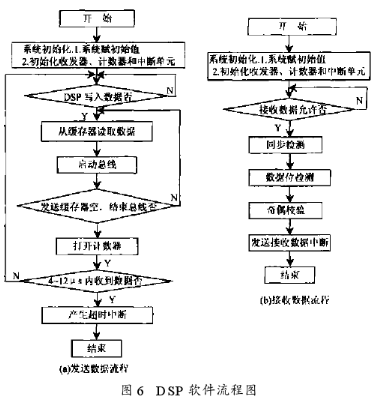

DSP控制部分程序实现的功能如下:

(1)对总线接口板的初始化(包括初始化DSP本身内部电路和寄存器FPGA及上位机通讯寄存器)。

(2)实现RT地址识别

由于是多RT总线接口板,所以收到数据后,应该判别该RT地址是否属于该接口板;

(3)与上位机消息传输控制功能

消息传输控制程序完成总线应传输的数据在总线接口 板和上位机之间的数据交换。包括数据的读写过程和自检测过程,所要完成的操作如下:

①向FPGA写入发送数据(到总线)。

②从FPGA内读出数据(该数据由DSP处理)。

③向双口RAM写入数据(到上位机)。

④自检测过程。自检测过程是在收到上位机的自检命令后,实现接口板的数据发送 和接收性能测试。

(4)中断控制程序

在DSP芯片TMS320F206接口的设计中,使用3个硬件中断,INT1,INT2由FPGA来产生,INT3 则由上位机来产生。INT1表明FPGA的接收单元已收到一个数据,通知F206读数,INT2表明FPGA的接收单元已收到一个错误数据,通知F206读取错误状态信息,INT3是上位机和接口板数据传输 控制的一种手段,通过INT3中断,上位机告诉接口板进行数据接收还是数据发送操作,发送多少数据,采用的消息格式以及总线控制等信息。

DSP部分的软件采用C++和汇编语言混合编程,关键路径如中断服务程序,数据发送和接收程序都采用汇编语言以达到最大的执行效率,主程序采用C++编写。

DSP部分软件的流程图,如图6所示。

5.3 上位机控制程序

主要实现上位机在特定的操作系统下对接口板的软件驱动、数据通讯和传输控制。主要使用C++在Windows环境下进行软件开发。

6、结语

本文介绍了一种基于FPGA和DSP对某型飞机总线系统通讯软件设计与实现的方法。在实际的运用中,较好的实现了总线系统通讯功能,对1553B总线研究具有一定的使用和参考价值。

责任编辑:gt

全部0条评论

快来发表一下你的评论吧 !