测量仪表

1、引言

在电路测试中。常常需要测试频率特性。电路的频率特性体现了放大器的放大性能与输入信号频率之间的关系。频率特性测试仪是显示被测电路幅频、相频特性曲线的测量仪器。在此,采用集成的直接数字合成器(DDS)AD985l,现场可编程门阵列(FPGA)及外围测量电路设计了一个频率特性测试仪。

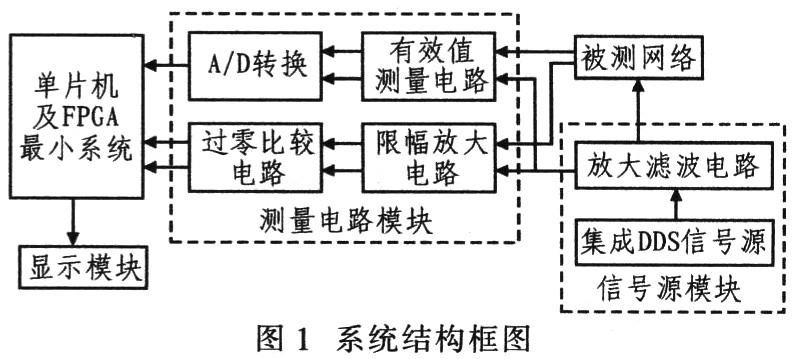

2、 系统总体设计方案

图1给出该测试仪的系统结构框图。它主要包括控制及运算模块、测量电路模块、显示模块、信号源模块等。考虑到该系统不仅需要运算,而且还需要必要的数字控制电路,因此控制及运算模块选用了单片机与FPGA相结合方式。由于DDS采用了相位累加合成技术,在数字域中实现频率合成.可以输出高精度与高纯度的频率信号,不仅频率范围大,精度高,控制性好,易于实现,而且避免采用单片函数发生器作为信号源时,外接电容电阻对频率的影响,其速度也比采用数字锁相环(PLL)频率合成技术快。因此,根据系统所需信号源的频带及频率分辨率等参数的要求,采用集成DDS器件作为信号源。AD985l是ADI公司推出的基于先进CMOS技术的高集成度DDS,在外接参考频率源时,它能产生频谱纯净、频率和相位都可控且高稳定度的正弦波,具有即时频率转换,控制灵活,体积小,成本低,功耗小等优点。AD985l的最高晶体振荡器为180 MHz,具有32位频率分辨率。

通过将相位量转换为数字脉冲量,再测量数字脉冲的占空比反映相位差的方法选择测量方式。该方法测量精度要比采用波形分析法高,比采用相位一电压转换法占用存储空间小,电路较简单,可使测量精度和占用空间得到平衡。在幅度测量时,所用测试信号源输出为标准正弦波,所以有效值与幅值之间存在简单的线性关系。利用该线性关系,可将测量的有效值转化为幅值。这种方法只需在有效值检波器件的外围添加适当的电阻、电容即可实现,且电路简单。检波器件采用AD637,当测量信号的峰值系数高达10时,附加误差仅为1%,且频带较宽。

3、 硬件电路设计

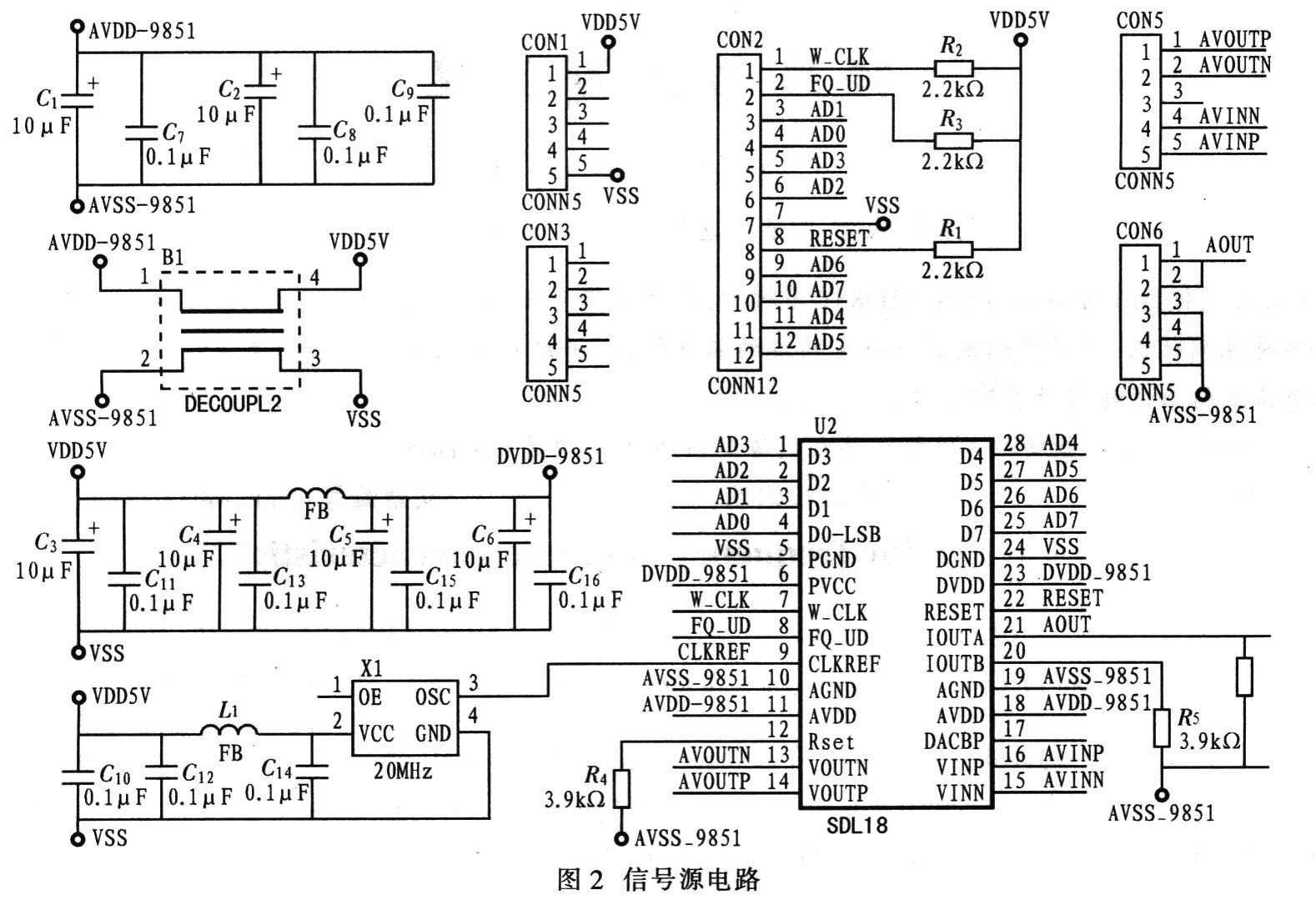

3.1 信号源电路设计

信号源电路是以集成的DDS器件AD9851为核心,并结合外围电路而构成的。为减少干扰,稳定输出频率,系统设计将AD9851及其外围电路集成在印制电路板上。图2给出其原理图。

3.2 相位差测量电路

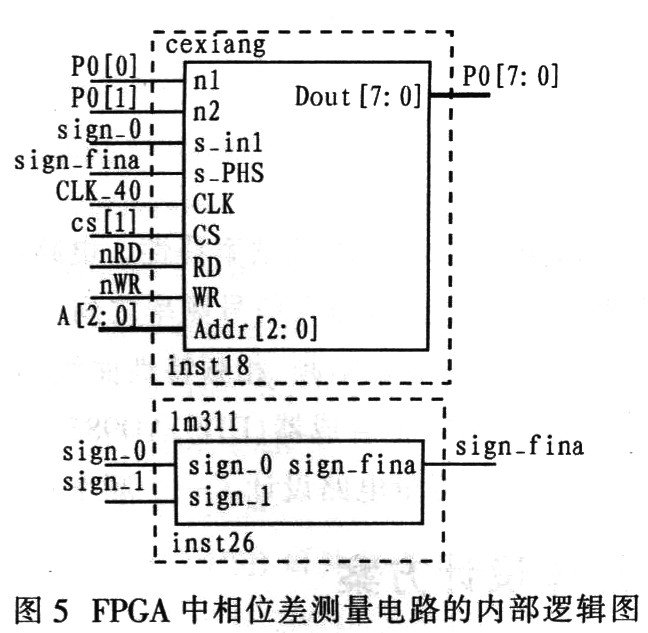

相位差测量电路由限幅放大电路及整形电路组成。限幅放大电路应选超高摆率,输出电流大,耐压高的运算放大器。同时,为使进入比较器的信号更稳定,应选取增益带宽积较大的运算放大器。因此可选取图3所示的LF356限幅放大电路。经限幅放大后的两路信号需经相同的整形电路才能进入FP—GA进行相位差测量,其具体的一路整形电路如图4所示。该整形电路以LM311作为过零比较器,采用迟滞回环比较接法,可有效避免在过零点时因信号干扰和抖动带来的跳变。图5给出FPGA中相位差测量电路的内部逻辑图。其工作原理是:首先将两路信号异或后,与其中任意的一路信号相与,得到与原信号频率相同,以及由占空比反映相位差大小的方波,再对该方波和原信号同时计数,判断极性后,即可得出相位差。

4 、系统软件设计

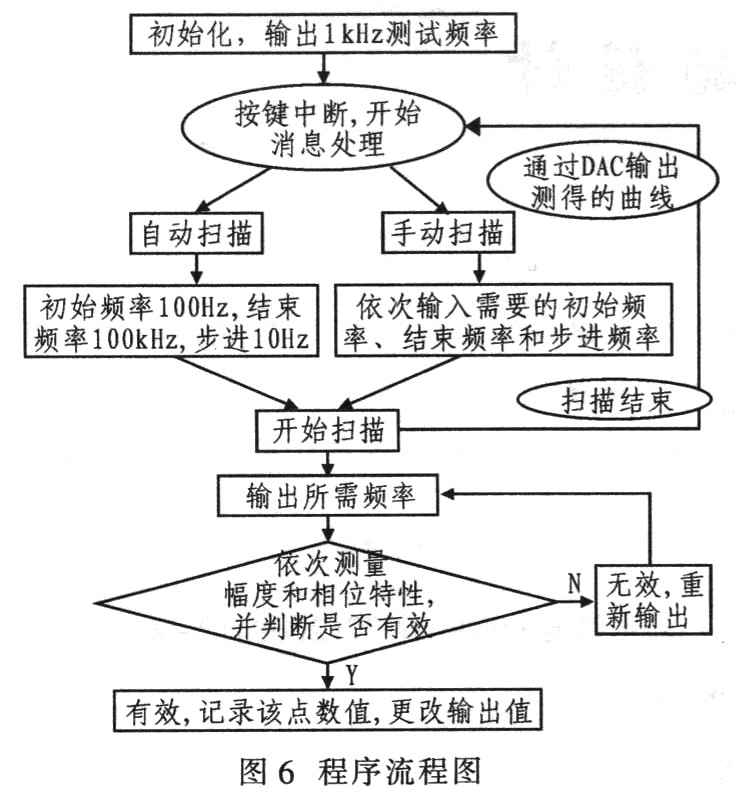

图6给出具体系统软件设计流程图。它主要包含初始化、键盘处理及扫频等。

4.1 AD9851初始化输出

AD9851的输出频率与控制字的关系为:控制字(32 bit)=频率(Hz)x时钟/232

在编写软件时.通过按键中断程序将自动和手动扫描分为两个子程序。主程序则在开始扫描时合并这两个子程序,实现频率特性的测量,这部分代码由循环结构和判断分支结构重复判断并输出。

该系统软件设计具有良好的消息处理机制,合理、有效判断采样,以及良好的外部控制。

5、 测试结果

6、 结语

该系统尚存在AD9851的输出频率不太稳定,显示时有时无等不足,但这些问题可用软件修正的办法予以克服。

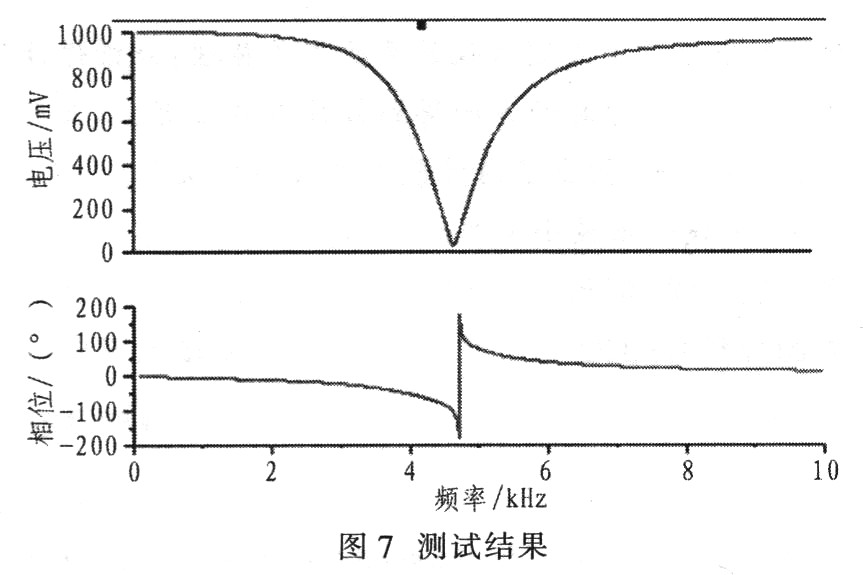

系统测试时选用双T网络(中心频率为5 kHz)作为被测网络。图7给出实测的幅频及相频曲线。由图可见,实测曲线中,该网络的中心频率在4.8 kHz附近。

责任编辑:gt

全部0条评论

快来发表一下你的评论吧 !