电子说

本文主要介绍以太网Drive Side接口(MAC和PHY之间的接口),也被称为MII(Media Independent Interface),支持从10M到100G的不同应用场合,主要包括MII、RMII、SMII(Cisco Systems Specification)、SSMII、S3MII、GMII、RGMII、SGMII、QSGMII(Cisco Systems Specification)、TBI、RTBI、XGMII、XAUI、RXAUI、XLGMII、XLAUI、CGMII、CAUI、HIGIG(Broadcom Specification)、Interlaken等接口,下面就针对10Mbps到100Gbps的不同接口进行介绍,最后介绍一下PHY芯片的控制接口MDIO BUS。

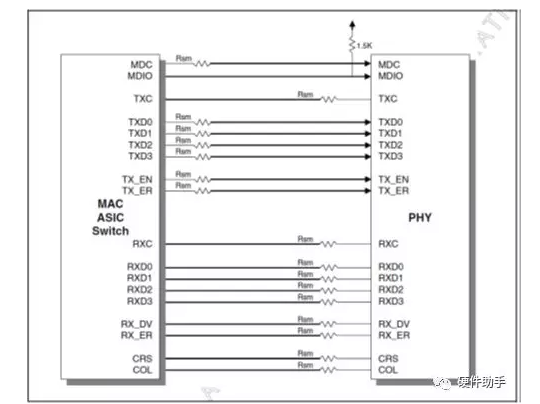

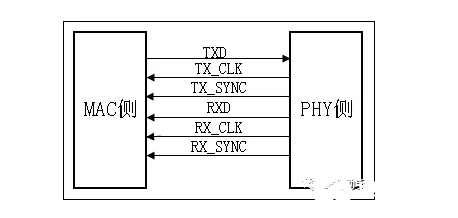

1、MII接口

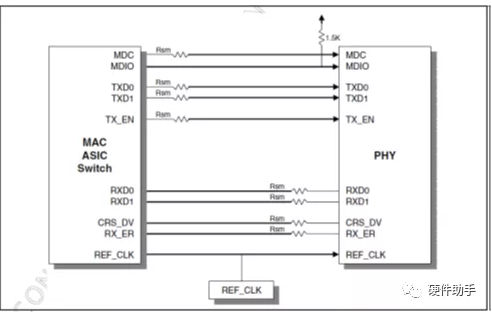

2、RMII接口

REF_CLK是由外部时钟源提供的50MHz参考时钟,与MII接口不同,MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

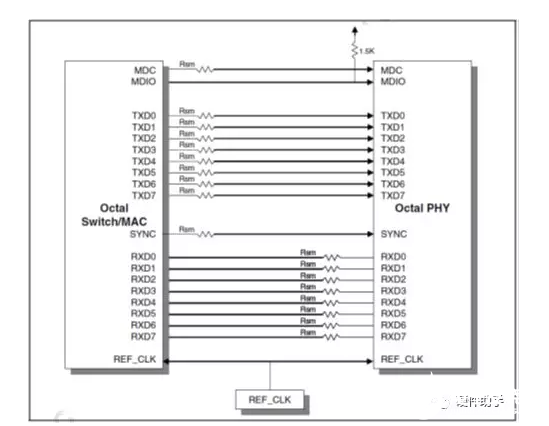

3、SMII(Cisco Systems Specification)接口

REF_CLK:所有端口共用的一个参考时钟,频率为125MHz,为什么100Mbps速率要用125MHz时钟呢?因为在每8位数据中会插入2位控制信号。

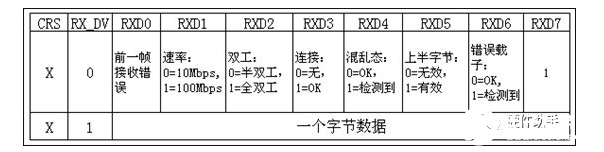

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:TXD[7:0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。当RX_DV为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。

当速率为10Mbps时,每一组数据要重复10次,MAC/PHY芯片每10个周期采样一次。MAC/PHY芯片在接收到数据后会进行串/并转换。

4、SSMII接口

5、S3MII接口

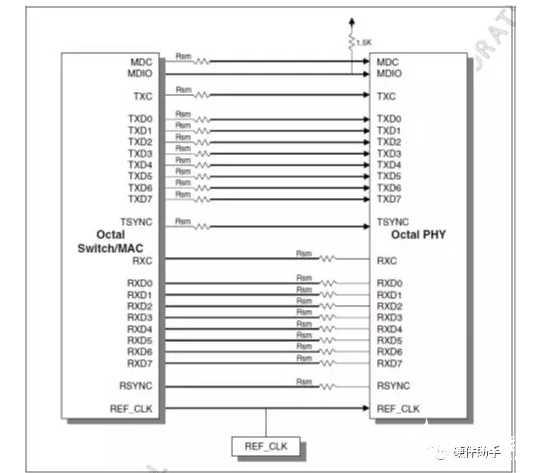

6、GMII接口

GMII的数据宽度为8位,GMII接口中的发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

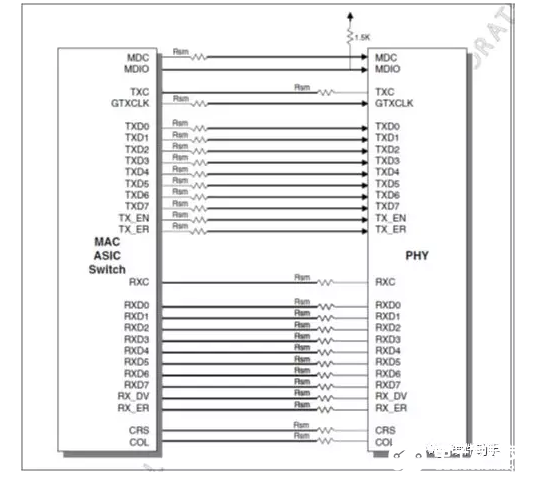

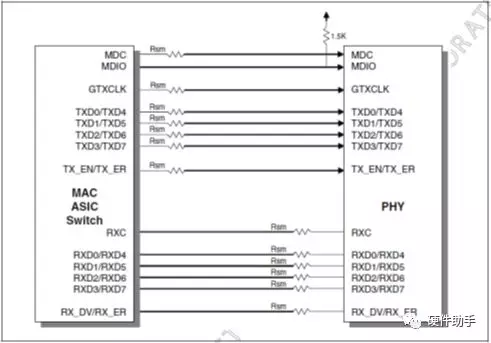

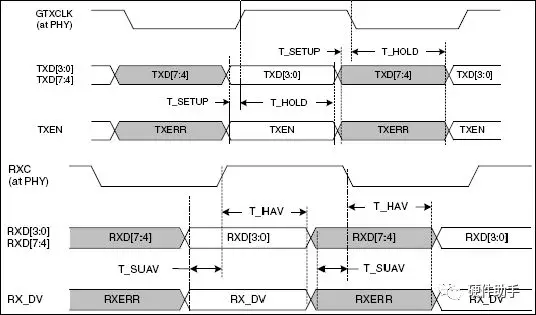

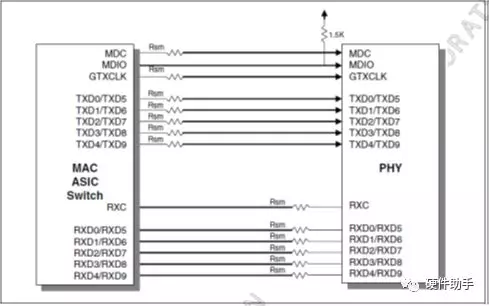

7、RGMII接口

RGMII的时钟频率为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。RGMII同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;同样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。

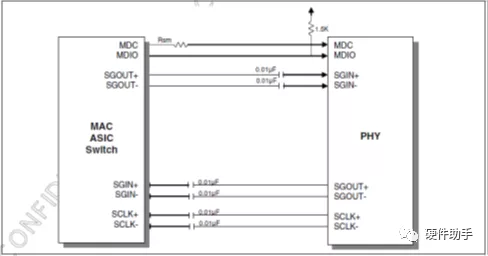

8、SGMII接口

SGMII收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样,参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用。收发都可以从数据中恢复出时钟。

在TXD发送的串行数据中,每8比特数据会插入TX_EN/TX_ER两比特控制信息,同样,在RXD接收数据中,每8比特数据会插入RX_DV/RX_ER两比特控制信息,所以总的数据速率为1.25Gbps=625Mbps*2。

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8b/10b变换,本来8b/10b变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8b/10b变换在MAC芯片中完成了。8b/10b变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取。

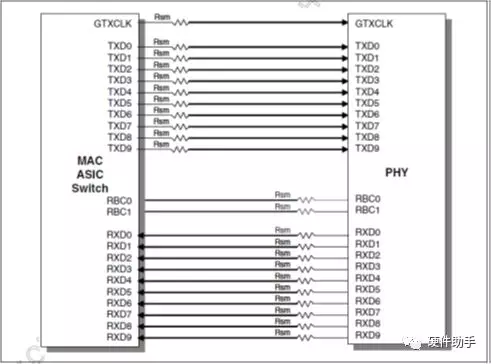

9、TBI接口

TBI即Ten BitInterface的意思,接口数据位宽由GMII接口的8位增加到10位,其实,TBI接口跟GMII接口的差别不是很大,多出来的2位数据主要是因为在TBI接口下,MAC芯片在将数据发给PHY芯片之前进行了8b/10b变换(8b/10b变换本是在PHY芯片中完成的,TBI在MAC中完成了,所以每传输一个字节需要传输10bit数据)。

RBC0和RBC1是从接收数据中恢复出来的半频时钟,频率为62.5MHz,RBC0和RBC1不是差分信号,而是两个独立的信号,两者之间有180度的相位差,在这两个时钟的上升沿都采样数据。RBC0和RBC1也叫伪差分信号。除掉上面说到的之外,剩下的信号都跟GMII接口中的相同。

大多数芯片的TBI接口和GMII接口兼容。在用作TBI接口时,CRS和COL一般不用。

10、RTBI接口

RTBI接口数据位宽为5bit,时钟频率为125MHz,在时钟的上升沿和下降沿都采样数据,同RGMII接口一样,TX_EN线上会传送TX_EN和TX_ER两种信息,在时钟的上升沿传TX_EN,下降沿传TX_ER;RX_DV线上传送RX_DV和RX_ER两种信息,在RX_CLK上升沿传RX_DV,下降沿传RX_ER。

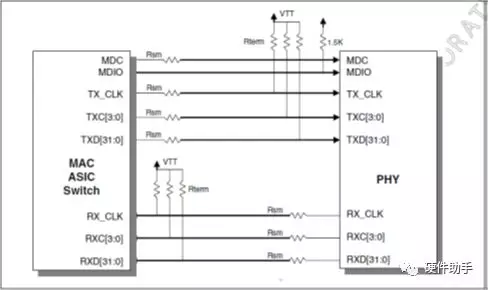

11、XGMII接口

XGMII接口的单端信号采用HSTL/SSTL_2逻辑,端口电压1.5V/2.5V,由于SSTL_2的端口电压高,功耗大,现在已很少使用。

TXC[3:0]:发送通道控制信号,TXC=0时,表示TXD上传输的是数据;TXC=1时,表示TXD上传输的是控制字符。TXC[3:0]分别对应TXD[31:24],TXD[23:16],TXD[15:8],TXD[7:0]。

RXC[3:0]:接收通道控制信号,RXC=0时,表示RXD上传输的是数据;RXC=1时,表示RXD上传输的是控制字符。RXC[3:0]分别对应RXD[31:24],RXD[23:16],RXD[15:8],RXD[7:0]。

TX_CLK:TXD和TXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

RX_CLK:RXD和RXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。156.25MHz*2*32=10Gbps。

XGMII接口还有XLGMII(40Gb)、CGMII(100Gb)等变种。其基本已经被XAUI/XLAUI/CAUI接口取代了。

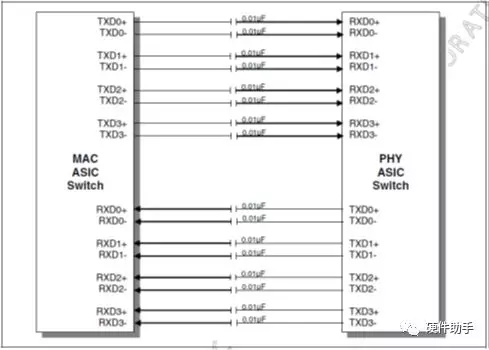

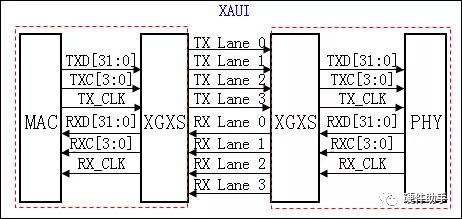

12、XAUI接口

XAUI接口有如下一系列的变种:RXAUI、XLAUI(40Gb)、CAUI(100Gb)等。

由于受电气特性的影响,XGMII接口的PCB走线最大传输距离仅有7cm,并且XGMII接口的连线数量太多,给实际应用带来不便。因此,在实际应用中,XGMII接口通常被XAUI接口代替,XAUI即10Gigabit Attachment Unit Interface,XAUI在XGMII的基础上实现了XGMII接口的物理距离扩展,将PCB走线的传输距离增加到50cm,使背板走线成为可能。

源端XGMII把收发32位宽度数据流分为4个独立的lane通道,每个lane通道对应一个字节,经XGXS(XGMII ExtenderSublayer)完成8b/10b编码后,将4个lane分别对应XAUI的4个独立通道,XAUI端口速率为:2.5Gbps*1.25*4=12.5Gbps。

在发送端的XGXS模块中,将TXD[31:0]/RXD[31:0],TXC[3:0]/RXC[3:0],TX_CLK/RX_CLK转换成串行数据从TX Lane[3:0]/RX Lane[3:0]中发出去,在接收端的XGXS模块中,串行数据被转换成并行,并且进行时钟恢复和补偿,完成时钟去抖,经过5b/4b解码后,重新聚合成XGMII。

XAUI接口采用差分线,收发各四对,CML逻辑,AC耦合方式,耦合电容在10nF~100nF之间。

XAUI接口可以直接接光模块,如XENPAK/X2等。也可以转换成一路10G信号XFI,接XFP/SFP+等。

有些芯片不支持XAUI接口,只支持XGMII接口,这时可以用专门的芯片进行XGMII→XAUI接口转换,如BCM8011等。

XAUI/XLAUI/CAUI是四通道串行总线,采用的差分信号,CML逻辑传输,并且进行了扰码,大大增强了信号的抗扰性能,使得信号的有效传输距离增加到50cm。

XAUI/XLAUI/CAUI在物理结构上是一样的,收发通道独立,各四对差分信号线。

对于XAUI总线,每对差分线上的数据速率为3.125Gbps,总数据带宽为12.5Gbps,有效带宽为12.5Gbps*0.8=10Gbps(因为XAUI总线数据在传输前进行了8b/10b变换,编码效率为80%)。

对于XLAUI总线,每对差分线上的数据速率为10.3125Gbps,总数据带宽为41.25Gbps,有效带宽为41.25Gbps*(64/66)=40Gbps(因为XLAUI总线数据在传输前进行了64b/66B变换,编码效率为96.97%)。

对于CAUI总线,每对差分线上的数据速率为25.78125Gbps,总数据带宽为103.125Gbps,有效带宽为103.125Gbps*(64/66)=100Gbps(因为CAUI总线数据在传输前进行了64B/66B变换,编码效率为96.97%)。

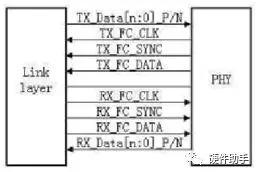

13、Interlaken

Interlaken是Cisco和Cortina公司共同推出的一种高速通道化的C2C(芯片间)接口协议。主要用于10Gbps端口的MAC、OC-768SONET Framer、下一代100Gbps以太网集成电路、100Gbps Swich Fabric与包处理器。主要有以下特征:

TX_Ddta[n:0]p/n:数据发送通道,CML差分电平,每对差分线速率为1~6.25Gbps;

TX_FC_CLK:数据发送通道带外流控参考时钟,LVCMOS电平;

TX_FC_SYNC:数据发送通道带外流控同步信号,LVCMOS电平;

TX_FC_DATA:数据发送通道带外流控数据信号,LVCMOS电平;

RX_Ddta[n:0]p/n:数据接收通道,CML差分电平,每对差分线速率为1~6.25Gbps;

RX_FC_CLK:数据接收通道带外流控参考时钟,LVCMOS电平;

RX_FC_SYNC:数据接收通道带外流控同步信号,LVCMOS电平;

RX_FC_DATA:数据接收通道带外流控数据信号,LVCMOS电平;

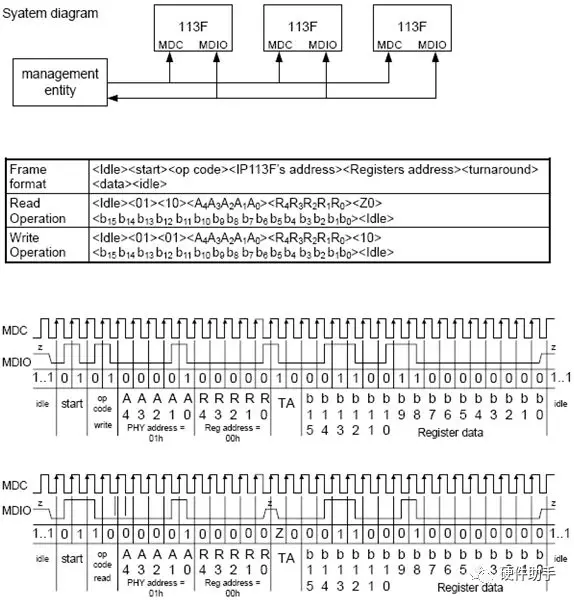

14、MDIO BUS(SMI(Serial Management Interface))

MDIO是一个以太网控制器的传输协议,广泛用于以太网控制器和PHY之间的数据通讯。

MDIO(Management Data Input/Output),管理数据输入输出总线。它是由IEEE802.3定义的以太网行业标准,它承载着MAC层和物理层通信的重任。MDIO接口包括两根信号线:时钟线MDC,数据线MDIO(双向),MAC层芯片(或其他控制芯片)可以通过它们访问物理层芯片的寄存器,并通过这些寄存器来对物理芯片进行控制和管理。

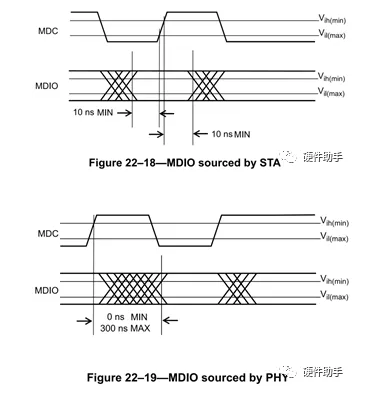

MDC(Management Data Clock):管理接口的时钟,是一个非周期信号,信号的最小周期为400ns(最快2.5MHz),最小正电平时间和负电平时间为160ns,最大正负电平时间无限制。

MDIO(Management Data Input/Output):是双向的数据线,用来传送MAC层的控制信息和物理层的状态信息。它与MDC时钟同步,在MDC上升沿有效。

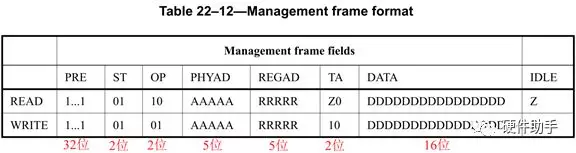

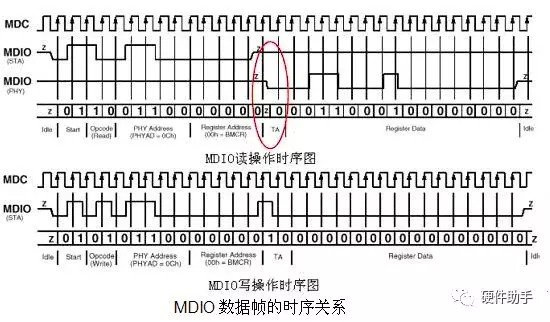

14.1、MDIO帧格式

PRE:帧前缀域,为32个连续“1”比特,这帧前缀域不是必需的,某些物理层芯片的MDIO操作就没有这个域。

ST:帧开始标识码,为“01”。

OP:帧操作码(读写操作),比特“10”表示此帧为一读操作帧,比特“01”表示此帧为一写操作帧。

PHYAD:PHY芯片的地址,5个比特,每个芯片都把自己的地址与这5个比特进行比较,若匹配则响应后面的操作,若不匹配,则忽略掉后面的操作。一个系统最多联31个PHY(地址0为保留)。

REGAD:用来选择物理层芯片的32个寄存器中的某个寄存器的地址。一个PHY上最多32个寄存器地址(可以使用shadow value技术,访问更多的寄存器)。

TA:状态转换域,若为读操作,则第一比特时MDIO为高阻态,第二比特时由物理层芯片使MDIO置“0”。若为写操作,则MDIO仍由MAC层芯片控制,其连续输出“10”两个比特。

DATA:帧的寄存器的数据域,16比特,若为读操作,则为物理层送到MAC层的数据,若为写操作,则为MAC层送到物理层的数据。

IDLE:帧结束后的空闲状态,此时MDIO无源驱动,处于高阻状态,但一般用上拉电阻使其处在高电平,即MDIO引脚需要上拉电阻。

14.2、MDIO操作时序

MDIO工作流程如下:

本文主要介绍了以太网MAC和PHY之间的接口,支持10Mbps到100Gbps的不同速率等级,同时介绍了PHY芯片的控制接口MDIO总线。

全部0条评论

快来发表一下你的评论吧 !