本篇主要介绍常用的单端逻辑电平,包括TTL、CMOS、SSTL、HSTL、POD12等。

1、TTL电平

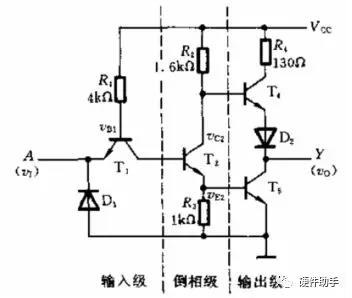

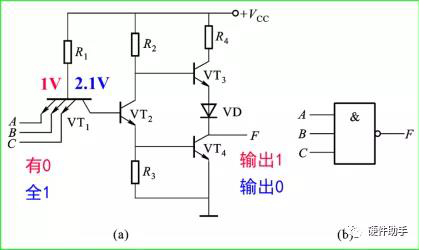

下面以一个三输入的TTL与非门介绍TTL电平的原理。

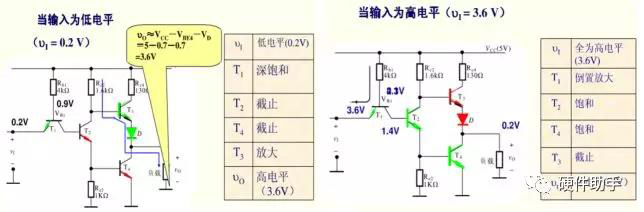

当输入全1时,uI=3.6V,VT1处于倒置工作状态(集电结正偏,发射结反偏),uB1=0.7V×3=2.1V(后级电路决定的),VT2和VT4饱和,输出为低电平uO=0.3V。

当输入有0时,uI=0.3V,VT1发射结导通,uB1=0.3V+0.7V=1V,VT2和VT4均截止,VT3和VD导通。输出高电平uO=VCC-UBE3-UD≈5V-0.7V-0.7V=3.6V。

TTL电平一般过冲都会比较严重,可以在始端串22欧或33欧电阻(因为TTL电路的输出阻抗大约为17Ω左右,从阻抗匹配的角度解释);TTL电平输入脚悬空时内部认为是高电平。

常见的TTL电平有5V TTL,3.3V LVTTL,2.5V LVTTL,1.8V LVTTL等。

2、CMOS电平

常见的CMOS电平有5V CMOS,3.3V LVCMOS,2.5V LVCMOS,1.8V LVCMOS,1.5V LVCMOS,1.2V LVCMOS,0.8V LVCMOS等。

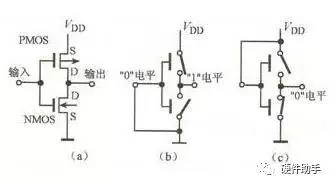

CMOS电路输出高电平是通过导通PMOS实现的,输出低电平是通过导通NMOS实现的,PMOS的载流子为空穴,NMOS的载流子为电子,空穴的电导率低于电子,所以PMOS的导通电阻比NMOS的导通电阻大(且相同额定值的PMOS比NMOS贵!!!),也就是输出高电平时其RC(C为传输线等效电容,寄生电容等)时间常数大,上升沿更缓,CMOS电路的上升时间比下降时间长。

CMOS器件是电压控制器件,而未被连接的输入端有靠近CMOS门槛电压输入的趋势,使得芯片内部的三极管作不必要的开关动作,这既增加了噪声干扰,又耗费了系统功率。MOS管输入阻抗很大(栅极源极之间有一层氧化层),输入阻抗大,对微弱信号的捕捉能力就很强(简单地把干扰源等效为一个理想电压源和一个内阻的串联,根据分压原理可知输入电阻越大输入的分压越大),所以悬空时很容易受周围信号的干扰。一般,使用上拉电阻或下拉电阻,把未被连接的输入引脚与电源或接地点连接,使它们有一个确定的电压值。CMOS输入引脚的最大输入电流非常小,只有1μA左右(最多几μA),因此选用1MΩ作为上拉电阻或下拉电阻就可以。

在许多嵌入式系统中,输入引脚的有效电压一般是5V以上或为负值(对地),在这种情况下,使用几个电阻就可以防止输入引脚过压。CMOS集成块内部的两个二极管可以把电压钳位在CMOS器件输入电压值,这两个二极管是高速CMOS器件(74HC系列)静电保护措施的一部分。

TTL集成电路内部都是用双极型三极管构成的,这种电路的输入电阻一般都不高(7400和74LS00这些门电路的输入电流一般都在几百μA以上,74LS系列的稍小一些),对外界各种杂波不是很敏感,故不用的输入端悬空即可(悬空相当于高电平!),亦可以直接接高电平或地(视具体情况而定)。

3、GTL(Gunning Transceiver Logic)电平

GTL输入电路是一个电压比较器,输入电压同一个外部连接的参考电压进行比较,输入门限设计为精确的窗口电压,可以提高最大的抗噪性能。输出电路是一个漏极开路N通道器件,当电路关闭时输出电压被上拉到末端匹配电压VTT,当输出电路打开时,器件可以吸收40mA的电流,可以产生最大的输出电压0.4V。输出电阻为25欧姆,输入输出被设计为与VCC的电压独立,器件可以工作在5V、3.3V,甚至是2.5V的VCC电压。

GTL和GTL+信号的参考电平Vref为信号上拉电平的2/3,这是同GTL电平的特点相关的,GTL信号的低电平一般为上拉电平的1/3左右,当GTL信号的参考电平设置为上拉电平的2/3时信号的高低电平有最大的抗噪冗余量,可以得到最佳的传输效果。现在很多厂家提供的GTL芯片的Vref都是可以通过外部进行调整,提供最佳的信号传输要求。同时因为GTL的输入阈值电平都很小,可以提供大的噪声容限,而小的输出电平提供的信号变化也很小。这些对信号的完整性有利。GTL+的信号的电平更高,有更大的驱动能力,一般对于重负载情况下使用GTL+的效果会更好一些。

4、SSTL电平

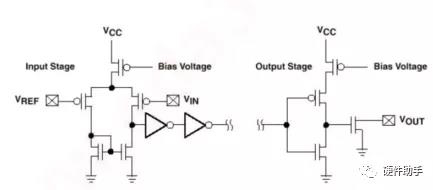

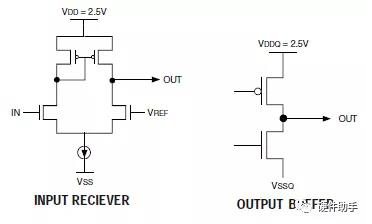

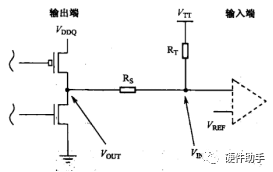

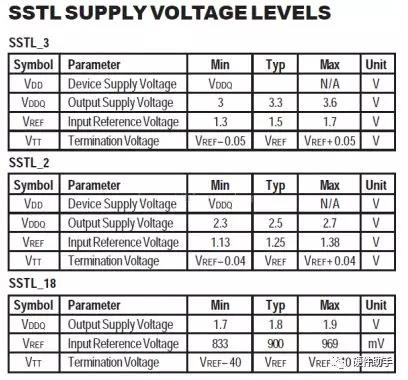

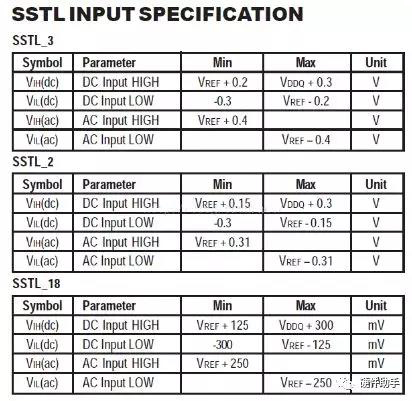

SSTL即Stub Series Termination Logic,分为SSTL_3(3.3V)、SSTL_2(2.5V)、SSTL_18(1.8V)、SSTL_15(1.5V)(对应的VREF=VTT分别为1.5V、1.25V、0.9V、0.75V),对应不同的供电电压,SSTL是传输线终端匹配的,因此SSTL具有输出阻抗和匹配方法的要求,这使其在高速信号传输时降低了EMI,改善了建立时间。SSTL的输入是一个差分比较电路,一端为输入,另一端为参考电压VREF。DDR使用的就是SSTL电平标准。

SSTL与LVTTL驱动器没有太多的不同,但是输入缓冲却非常不同。SSTL输入是差分对,因此输入级提供较好的电压增益以及较稳定的阈值电压,这使得对小的输入电压摆幅具有比较高的可靠性。

STL对于不同类型的驱动器有不同的参数。SSTL_3和SSTL_2定义了2类驱动器,以区别不同的终端匹配方案。SSTL_18没有明确的类型定义,但是,取决于终端环境,驱动器必须能够在输入缓冲处产生相应的电压摆幅。

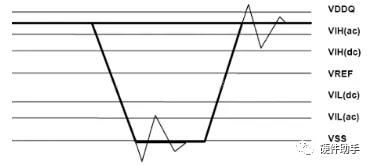

AC参数指的是一个阈值电压,当信号跨越这个阈值电压时,接收器状态一定会发生改变。只要输入保持在定义的DC阈值之上,接收器将维持逻辑状态不变。这有利于系统设计者对整个系统性能进行优化。

5、HSTL电平

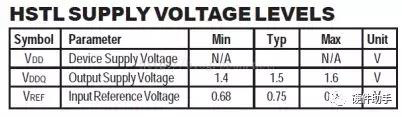

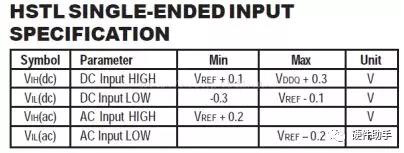

HSTL即High Speed Transceiver Logic,其最主要用于高速存储器读写,传统的慢速存储器阻碍了高速处理器的运算操作。在中频区域(100~180MHz),可供选择的单端信号IO结构有:HSTL、GTL/GTL+、SSTL、LVTTL;在180MHz以上,HSTL是唯一可用的单端IO接口。QDR使用的就是HSTL电平标准

JEDEC定义了四种驱动模式:Class I~IV,其区别仅在于输出电流的不同:

• Class I:IOH≥8mA,IOL≥-8mA;并行终端负载

• Class II:IOH≥16mA,IOL≥-16mA;串行终端负载

• Class III:IOH≥8mA,IOL≥-24mA;并行终端负载

• Class IV:IOH≥8mA,IOL≥-48mA;并行终端负载

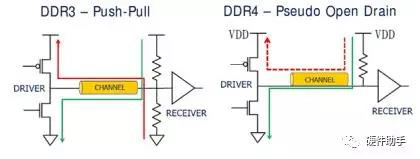

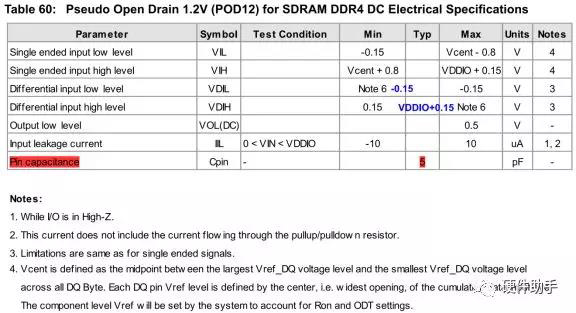

6、POD12电平

POD和SSTL的最大区别在于接收端的终端电压(POD为VDDQ,SSTL为VDDQ/2)。POD可以降低寄生引脚电容和I/O终端功耗,并且即使在VDD电压降低的情况下也能稳定工作。

当驱动端的上拉电路导通,电路处于高电平时,回路上没有电流流过,这样的设计较少了功耗。

除了上述一些常见的单端电平之外,还有BTL、ETL、HSUL等等。详细可参见相关标准。

编辑:hfy

全部0条评论

快来发表一下你的评论吧 !