电子说

引言

耦合电感常用于多相电源拓扑,充分利用其相间磁耦合电流纹波相抵消的技术优势。使用普通分立式电感时,一般只在多相降压转换器输出抵消电流纹波。当这些电感通过磁耦合时,电流纹波抵消作用到所有电路元件:MOSFET、电感线圈、PCB走线[1-6] 。所以,所有相开关操作仅影响到单相,从而减小电流纹波幅值、频率倍增。减小电流波形的RMS有助于提高电源转换效率,或减小磁元件、获得较快的瞬态响应,并进而减小输出电容需求。

耦合电感与传统电感设计的对比

传统非耦合降压转换器的峰-峰电流纹波可表示为式1,其中VIN为输入电压,VO为输出电压,L为电感,D为占空比(对于降压转换器,D = VO/VIN),Fs为开关频率。

(式1)

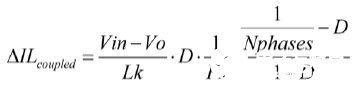

对于带有耦合电感的降压转换器,当D IN = 12V转换为核电压(0.5V至2.5V)。通过式2,很容易看到电路和磁元件参数对电流纹波抵消的影响。

(式2)

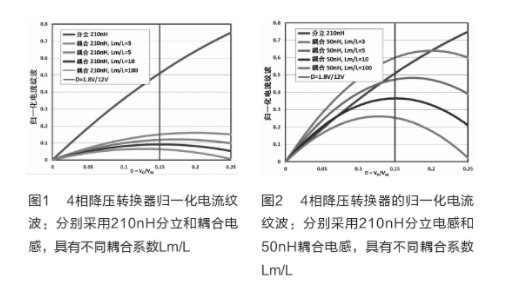

与式1相比,式2中的附加乘数取决于应用条件,随占空比、耦合系数以及耦合相数变化。图1所示为分别采用210nH分立或耦合电感的4相降压转换器的归一化电流纹波。用 电流纹波对电流纹波进行归一化,即D = 0.5时分立电感的纹波(所以D = 0.5时,分立电感的归一化电流纹波为1)。如曲线所示,对于12V转换为1.8V的典型应用,D = 0.15。

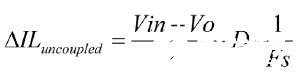

从图1可以看出,所有电源电路中由于采用耦合电感使得纹波电流大幅抵消。注意,在有些占空比下,电流纹波抵消明显大于D = 0.15的情况。耦合电感的几条曲线说明了耦合系数Lm/L的影响:Lm/L = 3 - 7范围内的耦合比较实用,有些Lm/L值比较理想化、不太现实,例如10和100。如果采用分立电感的初始设计比较合理,电流纹波可以接受,那么采用耦合电感可以减小电感值并达到D = 0.15下同等的电流纹波。这种条件下,50nH/相的耦合电感可提供与210nH分立电感同等的电流纹波,如图2所示。

相同的峰-峰电流纹波对应同等的电流波形RMS,使得所有支路的导通损耗和开关损耗相近,效率也相近。带来的优势是:50nH电感的瞬态性能比210nH提高4倍以上,而且,您可以彻底脱离大数值、不可靠、价格昂贵且体积较大的输出电容,只是留下本已存在的高性能陶瓷电容。

注意,对于具有快速瞬态响应的设计,陶瓷电容总是必需的。因为只有低ESR和ESL的电容能够满足负载快速变化时的瞬态要求。通常增加大电容来解决分立电感的低电流摆率和相关的能量储存问题。如果是采用耦合电感,仅仅陶瓷电容就足以满足多数要求。

耦合电感的优势不止于此。耦合电感设计为负耦合,当各相电流相等时,来自所有线圈的互感磁通彼此抵消。后一种情况通常出现在多相应用,尤其是采用电流模式控制的架构。只有漏磁通将能量储存在耦合电感中,所以图2所示例子的能量储存对应于50nH/相(而非210nH/相)。这意味着,与分立式电感相比,耦合电感小得多,并且/或者具有较高的额定饱和电流。

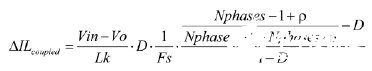

针对将12V转1V、为微处理器供电的典型4相方案,对两种磁元件配置进行比较:商用的高效分立电感FP1308R3-R21-R与 50nH耦合电感CL1108-4-50TR-R,网上提供相应的数据资料[7-8]。假设分立电感在PCB的 距离为0.5mm,分立电感所占电路板面积大约为722mm2;耦合电感则只需大约396mm,已经能够提供好得多的性能,如图3所示。同时,分立电感在室温+25℃时Is = 80A (无疑在较高温度下更差),而耦合电感在+105℃时的饱和电流高于110A/相。可实现占位面积减小1.8倍以上,饱和电流提高1.5倍以上。

为了更好地体会耦合电感的尺寸优势,可考虑在该4相方案中使用分立电感(物理尺寸更窄),但这样的电感会降低额定饱和电流,或者电感值比210nH小。后一种情况将进而增大电流纹波、降低效率。

假设为理想耦合(即Lm/Lk极大),可简化式2用来降低磁耦合电流纹波的乘数,将式2简化为式3[3]。可以明显看出这种耦合方案的优势与Nphases的关系,当然在很大程度上也与占空比相关。更确切地说,针对不同应用,可以从占空比D = 0或D = 1区域获取更大优势。

(式3)

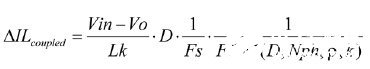

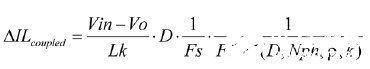

现在介绍利用耦合电感优势的方法。耦合电感电流纹波抵消的式2可归纳为式4。

(式4)

使用较熟悉、较方便的参数,可根据参考文献得出式4的品质因数(FOM)9。

(式5)

式5表示FOM适用于特定的占空比D范围:

,其中系数k在

范围内变化。

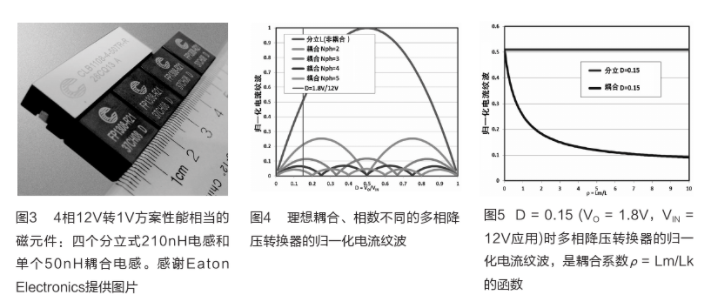

图4所示为整个占空比范围内,不同相数下电流纹波的减小。绘制电流纹波曲线时,假设为理想耦合,L值相同。很明显,增加耦合相数比较有利。

注意,对于采用分立元件的一般方案,针对给定输出电流正确增加相数是一种在成本、尺寸方面都很有优势的方法。对于在单芯片集成多个开关相的商用化集成方案,也非常具有吸引力。

图4也标记了一个特殊的占空比:D = 0.15,对应于实际例子VO = 1.8V,VIN = 12V。该条件绘制成图5所示曲线,表明耦合系数ρ = Lm/Lk对抵消电流纹波的影响。观察图4,D = 0.15时,分立电感的归一化电流纹波大约为0.5,如图5红色曲线所示。相同条件下,如果耦合系数非常低,4相耦合电感具有相同的电流纹波;随着耦合系数增大,电流纹波大幅减小,见图5。注意,电流纹波在开始下降非常快,在耦合系数较大时达到平坦,建议耦合系数大约为3至5。利用这种方法,可实现 的电流纹波抵消。

设计要点

假设我们从采用分立电感的多相降压转换器开始设计,目标是利用耦合电感提高系统性能。如果当前的分立电感设计具有合理的电流纹波,转换器效率也满足客户要求。对于耦合系数相对实用的4相降压转换器,从式5得到的预期FOM曲线如图6所示。

观察图6,D确定在大约0.15,可将FOM = 4作为设计目标。图7所示为得到的电流纹波:红色曲线表示分立电感L的初始电流纹波;两条曲线表示不同耦合系数下L的电流纹波; 两条曲线表示L/4时的电流纹波。与预期一样,D大约为0.15时,分立电感L和耦合电感L/FOM = L/4的电流纹波相当。

注意,根据应用的不同,目标占空比范围可能不同,所选FOM可能高于D≈0.15时的数值。对于典型设计,选择FOM = 4,其中利用50nH耦合电感代替210nH高效分立电感,如图3所示。正如预期,小得多的电感值必须满足饱和电流指标要求,所以耦合电感尺寸比传统方案小得多。选项FOM = 4也使瞬态条件下的电流摆率提高4倍,所以输出电容可减小大约4倍。

上述设计过程可应用到任意相数。注意,所选FOM不一定单单为了改善瞬态性能。根据应用条件和客户要求优先级的不同,可折中选择FOM,例如直接减小电流纹波,进而降低电路各处的传导损耗。例如,选择FOM = 4时,可以只将电感值降低2.6倍(同时也减小了提高的瞬态性能),使电流纹波减小、效率提高1.5倍。

随着耦合电感进入不同的电源应用领域,毫无疑问将有许多不同客户从该专有技术中受益。

责任编辑 LK

全部0条评论

快来发表一下你的评论吧 !