电子说

该篇将分析对象限定为一个DAC,其中的输出缓冲器在正常模式下被加电:零量程或中量程。文章将分析一下DAC输出在高阻抗模式中被加电的情况。同时提出一个针对加电毛刺脉冲的数学模型,随后给出一个尽可能减少此毛刺脉冲的电路板级解决方案。

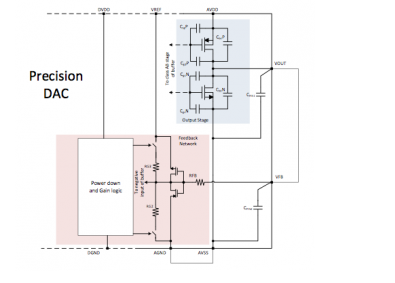

图1:DAC8760高精度DAC输出级

这个分析与没有加电毛刺脉冲减少 (POGR) 电路的DAC有关。第一部分列出了影响加电毛刺脉冲的因素。当DAC在电源斜升期间加电至高阻抗模式时,这个加电毛刺脉冲也可被视为一个在DAC的电压输出 ( ) 引脚上逐步累积形成的瞬态电荷。这个电荷积聚是由电源引脚,通过芯片内部和外部的寄生电容,到

) 引脚上逐步累积形成的瞬态电荷。这个电荷积聚是由电源引脚,通过芯片内部和外部的寄生电容,到 引脚的电容耦合造成的。需要注意的是,与加电毛刺脉冲相比(第一部分),这个毛刺脉冲本质上说是AC毛刺脉冲。因此,它的幅度取决于电源斜升时间。在大多数多电源芯片中,数字电源和基准引脚有一个到

引脚的电容耦合造成的。需要注意的是,与加电毛刺脉冲相比(第一部分),这个毛刺脉冲本质上说是AC毛刺脉冲。因此,它的幅度取决于电源斜升时间。在大多数多电源芯片中,数字电源和基准引脚有一个到 引脚比较弱的寄生路径。因此,这些引脚不是造成加电/断电毛刺脉冲的主导原因。

引脚比较弱的寄生路径。因此,这些引脚不是造成加电/断电毛刺脉冲的主导原因。

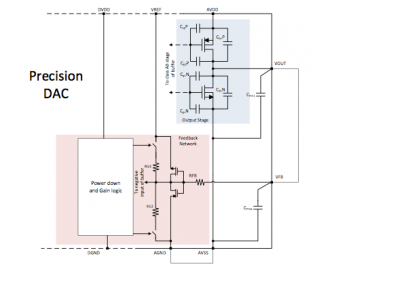

图2:高精度DAC输出级模型

DAC输出级中的NFET/PFET晶体管的尺寸要远远大于其它开关,这是因为这个输出级被设计用于特定的负载驱动。因此,这些FET的寄生电容要远高于其它片上组件的寄生电容。图1显示的是一个典型高精度DAC输出级 (DAC8760) 的简化图。在这个图中,假定输出级和芯片的数字内核分别具有单独的电源。反馈节点上放置的二极管用来保护增益/断电网络中的晶体管。

如图所见,进入 引脚的主要寄生电容是VOUT 结合线、引线和输出FET的寄生电容的组合值。在这个假设下,DAC输出引脚可被建模为一个简单的电容分压器。图2中的经简化模型在反馈节点和VREF/AGND之间使用2个二极管。由于这些二极管代表了一个FET(图1),在以后的分析中,这些二极管上的压降可被忽略不计。

引脚的主要寄生电容是VOUT 结合线、引线和输出FET的寄生电容的组合值。在这个假设下,DAC输出引脚可被建模为一个简单的电容分压器。图2中的经简化模型在反馈节点和VREF/AGND之间使用2个二极管。由于这些二极管代表了一个FET(图1),在以后的分析中,这些二极管上的压降可被忽略不计。

被放置在反馈节点与VREF/GND之间的反馈电阻器 (RFB) 和FET限制了毛刺脉冲数量级的上限和下限。在这个条件下,可被观察到的最大加电/断电毛刺脉冲被限制在VREF和GND之间。

尽可能减少加电/断电毛刺脉冲

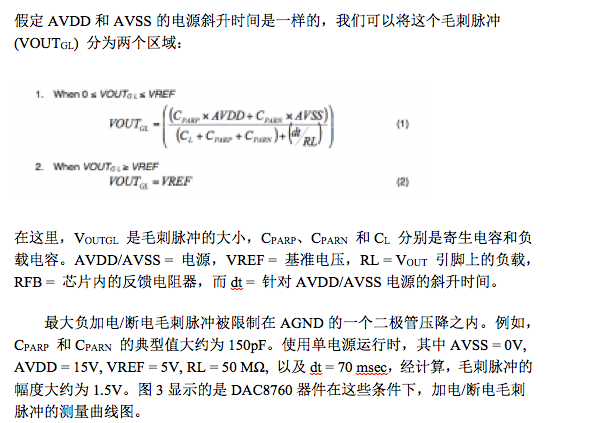

图3:DAC8760 VOUT加电毛刺脉冲,无负载。

让我们来深入研究一下尽可能减少加电/断电毛刺脉冲的一些方法。在方程式 (1) 和 (2) 中,我们看到这些方程式中的某些项是常量。例如,寄生电容是器件寄生效应的函数。电源电压由应用需求决定。斜升时间由电源设计确定。剩下的数据项只有相对于电源的负载阻抗和VREF的排序。这就形成了减少加电/断电毛刺脉冲的2个主要方法:电源排序与负载。

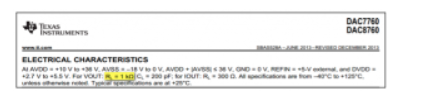

图4:数据表技术规格示例

电源排序是指以特定的顺序,用不同的电源为芯片加电/断电。对于DAC8760来说,由于加电/断电毛刺脉冲直接与VREF成比例,在AVDD/AVSS之后为VREF加电可以极大地减少这个毛刺脉冲。这个解决方案可以在对电源和基准电压进行单独控制时使用。

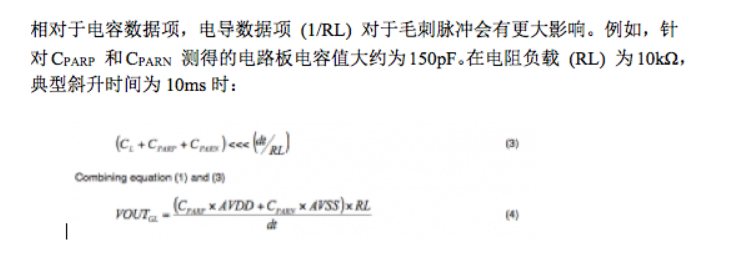

方程式 (1) 中的分母由一个电容数据项 (CPARP + CPARN + CL) 和一个电导数据项 (1/RL) 组成。这就形成了几个尽可能减少毛刺脉冲的方法:增加电容负载 (CL)、或者减少阻性负载 (RL)。增加电容负载会对整个系统的带宽产生不利影响。它还会影响输出放大器的稳定性。因此,不建议使用这个方法来实现毛刺脉冲最小化。

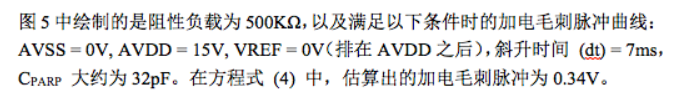

在选择使用一个小值阻性负载时,方程式 (4) 可以将加电/断电毛刺脉冲数量级减少到mV以下级别。这会导致大电流流经输出缓冲器,从而使 精度技术规格降级,比如说偏移、增益、线性等。因此,要根据数据表技术规格来选择

精度技术规格降级,比如说偏移、增益、线性等。因此,要根据数据表技术规格来选择 引脚上的阻性负载。例如,DAC8760数据表规定了负载为1kΩ时的精度参数(图4)。

引脚上的阻性负载。例如,DAC8760数据表规定了负载为1kΩ时的精度参数(图4)。

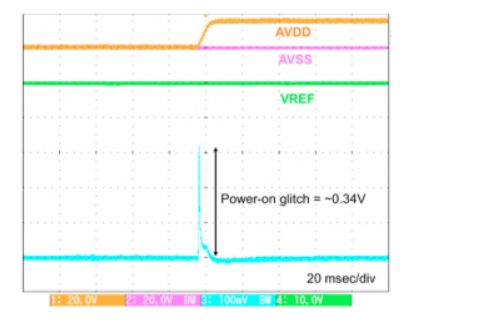

图5:DAC8760  加电毛刺脉冲 – RL = 500KΩ

加电毛刺脉冲 – RL = 500KΩ

结论

加电/断电毛刺脉冲对系统十分有害。它们的影响只有在系统设计好、进行测试时才会显现出来。因此,有一点很关键,那就是通过仔细检查组件,并使用这篇文中给出的技巧来设计系统,以尽可能减少这些毛刺脉冲。我们已经讨论了形成这些毛刺脉冲的根本原因,并且提出了一个尽可能减少这些毛刺脉冲的板级解决方案。

编辑:hfy

全部0条评论

快来发表一下你的评论吧 !