本课程是 DMA 课程的基础,读者务必认真先阅读和学习。本课程设计一个最基本的 DMA 环路,实现 DMA 的环路测试。 PS 端 ARM 将数据发送给 DDR。 PS 控制 DMA,使 DMA 通过数据通道读取 DDR 中的数据;DMA 将读取到的数据传给 FIFO。 FIFO 将数据传输给 DMA;PS 控制 DMA,使 DMA 通过数据通道将数据写入 DDR 中。 传输校验,对比接收数据与发送数据是否一致。本课程会详细介绍创建工程的每个步骤,后面的课程将不再详细介绍创建工程的步骤。

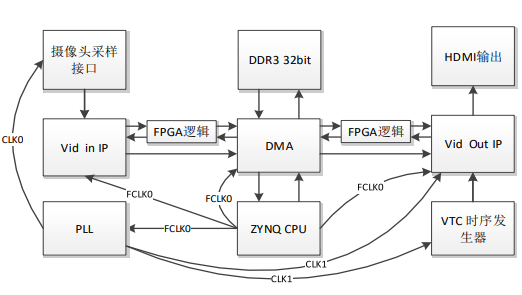

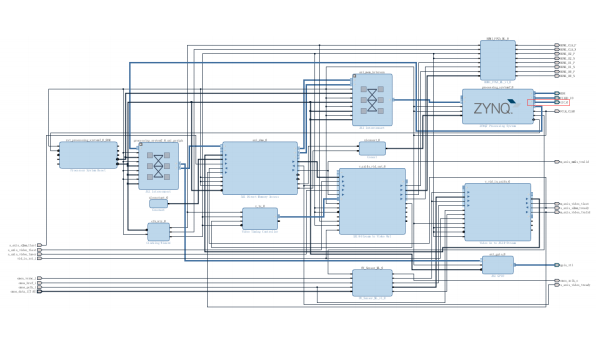

摄像头接口采集的摄像头数据,进过 vid in 视频输入 IP 后,还需要通过用户 FPGA 逻辑编程,和 DMA IP 之间实现握手协议,实现把数据通过 DMA 写入到 DDR。每次写入一副图像的数据后,产生一次接收中断,接收中断函数,会把数据三缓存后,在通过 DMA 发出去,DMA 发送完成后产生中断,在中断中,把缓存好的图像发送出去。DMA 发送的数据需要发送到 vid out 视频输出 IP。同理,DMA 和 vid out IP 之间也许需要增加 FPGA 用户代码实现接口的握手协议。数据进入 vid out 后,会随同 vtc IP 输出符合 VGA 时序的图像信号。HDMI 驱动 IP 会将 vid out 的VGA输出信号转换为HDMI信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !