电子说

在最近关于运算放大器频率补偿的文章中,我们讨论了频率补偿的概念是什么以及如何评估示例电路的稳定性。我们通过解决极点补偿的概念以及如何修改开环增益以允许由单极点主导的轮廓。本文将展示一种实现此目的的方法,称为并联电容。并联电容补偿有意地将电容与电路节点的现有电容并联。

并联电容器补偿

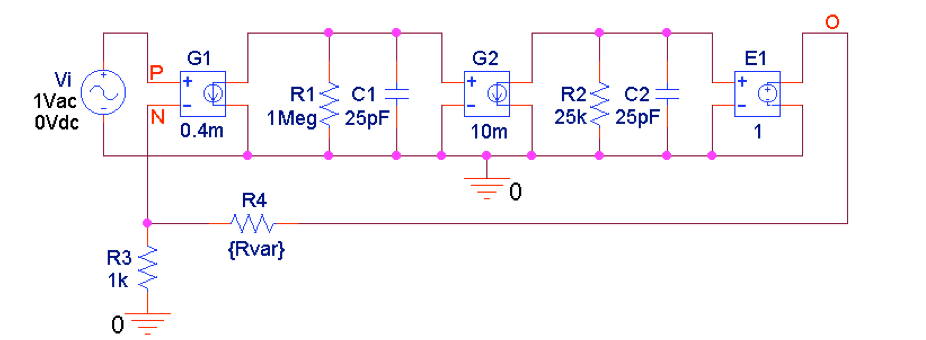

使极点占主导地位得以种方法是将电容添加到负责最低极点频率的节点。上一篇文章介绍了下面图1的两极运算放大器模型,其中f1是最低极点频率。

图1.运算放大器的近似AC模型。

然后使用图2的PSpice电路生成图3的曲线。

图2.用于绘制由R4确定的20dB步进的闭环增益的PSpice电路。

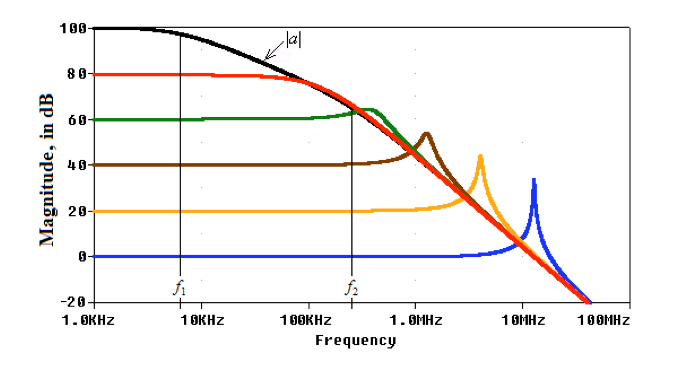

图3.针对不同反馈量的图2电路的闭环增益。

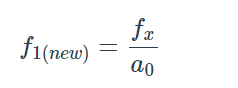

这些曲线表明运算放大器需要进行频率补偿,以防止增益达到峰值,特别是在较低的闭环增益时。一旦我们决定在何处定位用于单位增益操作的交叉频率ƒX,我们通过利用补偿增益的增益带宽积的恒定性或一个a0׃1(new)=1׃X找到ƒ1的新值,从而使

公式1

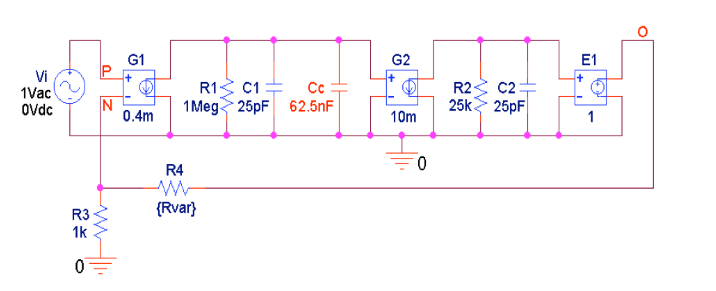

一个好的起点是施加ƒX=ƒ2,因为它很容易几何可视化。对于图2的电路中,得到ƒ1(new)=ƒ2/a0=2.546Hz,在给出Cc=62.51nF情况下,发现所述补偿电容的要求Cc(与C1并联)值为1/[2πR1(C1+Cc^)]=ƒ1(new)。重新运行图2的电路,但如图4(下图)中添加了Cc,得到了图5的曲线图。除了单位增益情况外,所有曲线现在都免除峰值,因为每个曲线都具有90°相位裕度。

图4.用于在并联电容补偿后以20dB步进绘制闭环增益的PSpice电路。

责任编辑人:CC

全部0条评论

快来发表一下你的评论吧 !