Clock shew是数字集成电路设计中一个重要的因素。本文比较了在同步电路设计中0clock shew和非0clock shew时钟分布对电路性能的影响,分析了通过调整时钟树中CLOCK SKEW来改善电路性能的方法,从而说明非0clock shew时钟分布是如何提高同步电路运行的最大时钟频率的。

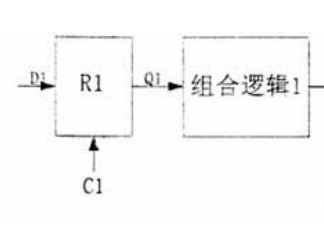

在当前的数字集成电路设计中,同步电路占了很大部分。所谓同步电路,也就是电路中的数据锁存是由一个或多个分布在全电路中的时钟信号来控制的。同步电路中包含三种主要结构:组合电路、时序电路和时钟分布网络。组合电路用来实现各种逻辑计算;时序电路作为存储单元,用来存储由时序电路计算得到的逻辑值;时钟分布网络的作用是向整个电路中的时序逻辑提供正确的时钟信号,以达到使整个电路正确运行的目的。同步电路中这三种结构之间的关系可用图1来表示。

可以看出,时钟网络在同步系统中的作用非常重要,正确的时钟网络可以避免在同步电路中出现竞争冒险及逻辑错误。只有保证到达各个时序单元(包括寄存器、锁存器)的时钟信号的时序是正确的,才能保证时序单元在每个时钟周期锁存得到正确的逻辑值,从而保证整个电路功能的正确。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !