为解决机载高分辨率图像的实时压缩问题,提出了一个基于FPGA+PowerPC的高分辨率图像实时压缩系统的设计方案。本系统主控采用PowerPC处理器,压缩芯片采用ADV202,用FPGA实现图像数据流程中各个环节控制,最终输出数据为高性能的静止图像压缩标准JPEG2000格式。

随着多媒体技术的快速发展对数字图像的分辨率和处理速度提出了越来越高的要求。本文基于FPGA+P0werPC架构,设计出一种机载高分辨率图像实时压缩系统,可以实现对输入的高分辨率(4 008×5 344)图像的实时压缩,适合在各种复杂环境下工作,可应用于各种航拍、监控和侦察系统。

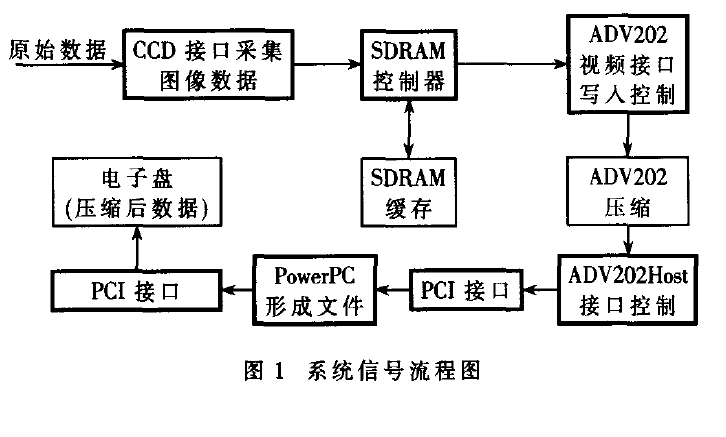

1系统组成及工作原理

本系统是航空数码相机压缩存储系统的子系统,大系统主要由图像预处理模块、压缩模块和存储模块构成,本文主要针对压缩模块进行了设计。由于系统CCD输入图像分辨率较高,一幅完整图像数据的大小为4 008×5 344×12 bit,约33 MB,这样庞大的数据量对压缩系统的缓存和处理速度提出了很高的要求。根据系统任务要求,压缩系统属于机载系统,对CCD输入的图像完成2种功能。一种是每隔3幅图像抽取一幅进行有损压缩并通过载机传送回地面实时显示;另一种是对图像进行无损压缩并直接存入电子盘中。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !