电子说

摘 要: 针对伺服电机控制系统中的脉冲发送需求问题,提出了一种利用DDS技术,以单片机和CPLD为硬件基础的脉冲输出频率、个数可控的脉冲发生器设计方案。利用Quartus II软件进行了波形仿真并分析了结果。研究结果表明,采用该方案实现的脉冲发生器具有体积小、成本低和可靠性高等特点,而且该脉冲发生器控制简单,输出脉冲频率控制精度高,满足了伺服电机控制系统中的脉冲发送需求。

随着工业自动化的发展,伺服电机的应用越来越广泛。伺服电机主要靠脉冲来定位,其基本的工作原理是伺服电机接收到1个脉冲,旋转1个脉冲对应的角度来实现位移,而脉冲的频率会影响电机旋转速度[1]。同时,自动化过程中,常常需要多个伺服电机的联合运动。因此,研究能够输出多路频率、脉冲数可控的脉冲发生器就很有必要。由于复杂可编程逻辑器件(CPLD)具有I/O口多、设计灵活、集成度高和稳定性好的优点[2],因此,本设计以CPLD为硬件平台,实现了一种脉冲频率、脉冲个数都可控的脉冲发生器。

1 脉冲发生器整体系统框图

根据要求所需,设计了图1所示的脉冲发生器系统。上位机发送脉冲频率、个数等命令,通过RS485通信给单片机,单片机再将命令通过数据总线传递给CPLD,CPLD的I/O输出多路可控脉冲信号。本设计中,CPLD为整个脉冲发生器系统的核心所在。

2 脉冲发生器的设计原理

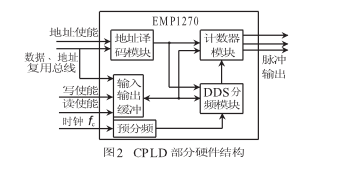

CPLD部分的硬件结构如图2所示。设计所用的CPLD芯片为Altera公司的EPM1270T144,采用VHDL语言,外部晶振时钟频率为25 MHz。CPLD内部有预分频、地址译码模块、输入缓冲、DDS分频模块及计数器模块,数据、地址复用总线位宽8位。

2.1 地址译码模块

CPLD中设计了三路脉冲输出,这就使得计数模块、分频模块需要多组寄存器来存储相应的数据。因此,设计了地址译码模块方便单片机与之数据通信。14、24、34(十六进制)分别对应计数器模块内三个脉冲个数寄存器的地址,可读写寄存器的值;10、20、30(十六进制)分别是DDS分频模块内三个频率控制字M的寄存器地址,可写入寄存器的值;地址96(十六进制)对应的寄存器低三位控制三路脉冲输出使能。

2.2 输入输出缓冲

为构成芯片内部的总线系统,使数据的写入读出都能正确,输入输出缓冲采用双向端口的总线电路。设计程序如下:

entity bustri is

port

datain:in std_logic_vector(7 downto 0);

rd_en:in std_logic;

wr_en:in std_logic;

tridata:inout std_logic_vector(7 downto 0);

dataout:out std_logic_vector(7 downto 0));

end bustri;

architecture one of bustri is

begin

process(wr_en,tridata)

begin

if wr_en=′0′ then

dataout《=tridata;

else dataout《=“ZZZZZZZZ”;

end if;

end process;

process(rd_en,datain)

begin

if(rd_en=′0′)then

tridata《=datain;

else tridata《=“ZZZZZZZZ”;

end if;

end process;

单片机先通过数据、地址复用总线给CPLD输入地址,地址译码模块将地址译码,使对应的寄存器输入使能;再通过输入输出缓冲写频率、脉冲个数数据给对应的寄存器;然后将脉冲输出使能,即可使脉冲输出。

2.3 DDS分频模块

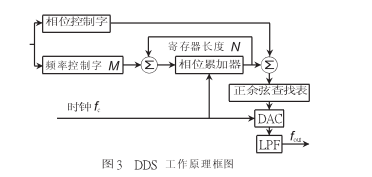

DDS分频模块用来控制输出脉冲的频率。DDS技术是一种从相位概念出发直接合成所需波形的频率合成技术[3]。DDS分频模块由相位累加器、正余弦波形查找表ROM存储器、D/A转换器和低通滤波器构成,其基本原理框图如图3所示。相位累加器在系统时钟控制下产生正余弦波形查找表ROM的地址,相位溢出频率即正余弦波输出频率。

通过改变频率控制字的大小就可以改变输出信号的频率。记频率控制字为M,正余弦波相位寄存器为N位,系统时钟为fc,则输出信号的频率fout可表示为fout=M·fc/2N。它的频率精度是由相位累加器或者是调整字的比特数决定的,即输入的参考频率除以2N,就决定了DDS所能够实现的频率精度[4],因此其频率分辨率为fmin=fc/2N。同时,通过给相位累加器额外加一个相位控制字K,可以控制输出信号的初始相位。

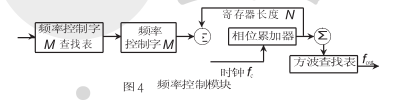

图3中,外部晶振fc为25 MHz,通过预分频模块进行四分频,变为6.25 MHz,作为DDS分频模块的输入时钟fc。频率控制字M为15位,相位寄存器21位。查找表内存放方波数据。因此,可根据上述公式计算得出输出脉冲频率的精度为3 Hz,变化范围约为3 Hz~100 kHz。DDS模块内有三个相同的频率控制模块,每个模块设计框图如图4所示。

图4中,设计的频率控制字查找表是256×15的ROM存储器,存放了在3 Hz~100 kHz范围内均匀采样256个离散点的频率,所对应的频率控制字M的值。其地址范围为00~FF(十六进制),低地址对应小的M值,M值随地址的增大而增大。M字的位宽为15位,数据总线8位,如正常写数据需要写两次,利用频率控制字查找表可以更加方便地设置频率控制字,写一次数据就可以改变M字的值。方波查找表内存放的是256×1的方波数据。单片机写入地址10、20、30(十六进制)后,通过8位的数据线写00~FF(十六进制)值给频率控制字查找表,查找表将对应的M字传给频率控制字M的寄存器。经过相位累加器累加,累加器的高8位作为地址送入方波查找表,查找表就可以输出频率不同的脉冲信号给计数器模块。

2.4 计数器模块

计数器模块用来控制输出脉冲的个数。计数器模块内有三组8位的脉冲个数寄存器。脉冲个数寄存器需要被赋予目标脉冲个数;待其他寄存器设置好后,单片机发送使能脉冲输出;DDS分频模块发送频率不同的脉冲送入计数器模块;计数器模块内部计数变量会根据输出的脉冲个数进行累加,当计数变量累加到目标脉冲数后,计数变量停止累加,并且脉冲输出也会被停止。

3 脉冲发生器总体仿真结果分析

本设计利用Quartus II软件进行波形仿真,仿真结果如图5所示。

图5中,XOSC为外部晶振时钟25 MHz;ale为地址使能,下降沿有效;rd为读使能,低电平有效;wr为写使能信号,低电平有效;AD为数据总线,显示方式为十六进制;MYA为三路脉冲输出;地址14对应的脉冲个数寄存器及地址10对应的频率控制字M的寄存器,控制MYA(0)的脉冲输出,地址24、20对应的寄存器控制MYA(1)输出,地址34、30对应的寄存器控制MYA(2)的脉冲输出。

由图5可以看出,地址14对应的脉冲个数寄存器写入的值是10,转换成十进制为16,MYA(0)输出脉冲个数即为16;地址24对应的脉冲个数寄存器写入的值是05,转换成十进制为5,MYA(1)输出脉冲个数即为5;地址10对应的频率控制字M的寄存器写入的值是FF,对应的M值最大,即输出频率应为100 kHz,而图5中,时间长度从230 ?滋s~270 ?滋s间,MYA(0)输出完整脉冲4个,计算出MYA(0)输出脉冲的周期约为10 ?滋s,对应频率即为100 kHz;地址20对应的频率控制字M的寄存器写入的值是7F,对应的M值为最大的一半,即输出频率应为50 kHz,由图5可以看出,MYA(1)输出的脉冲波形频率为MYA(0)的一半,对应即为50 kHz。使能脉冲输出后,通过写地址30改写MYA(2)的频率控制字M的值由47变为21,MYA(2)的脉冲输出频率正确改变。由上述分析可得,脉冲发生器产生的脉冲个数、频率均能随着指令的改变而正确改变。仿真结果验证了该方案的可行性。

本文介绍了一种利用DDS技术,通过单片机和CPLD来实现的脉冲输出频率、个数可控的脉冲发生器设计方案,且通过软件仿真验证了该方案的可行性。该方案在伺服电机的控制中也得到了实际应用,效果良好。采用该方案实现的脉冲发生器不仅具有CPLD的体积小、成本低、功耗低、集成度高、系统稳定性和可靠性高等特点,而且结合了DDS技术的特点及优势,控制简单,输出脉冲频率控制精度高,满足了伺服电机控制系统中的脉冲发送需求。

参考文献

[1] 刘树聃,王琳。基于MCU和CPLD的脉冲发生器[J]。微计算机信息,2012,28(9):121-122.

[2] 宋万杰,罗丰,吴顺君.CPLD技术及其应用[M]。西安:电子科技大学出版社,1999.

[3] 张楠,张根栋。基于DDS技术的全数字QPSK调制器的设计[J]。工矿自动化,2009(7):105-107.

[4] 李涛,高德远.DDS直接数字合成研究及其CPLD实现[J]。计算机工程与应用,2000,36(12):72-73

[5] 王强,陈阳。可调多脉冲时序发生电路的数字化设计[J]。电子测量技术,2009,32(8):28-31.

[6] 耶晓东。基于单片机的简易机械手的设计[J]。微计算机信息,2009,25(5-2):230-231.

[7] Altera Corpration. MAX 7000 Programmable Logic Device Family[Z]。 USA:Altera Corpration,2003.

[8] 金西.VHDL与复杂数字系统设计[M].西安:西安电子科技大学出版社,2003.

[9] 游志宇,董秀成,杜杨,等.单片机与FPGA/CPLD总线接口逻辑设计[J].微计算机信息,2008(29):121-123.

[10] 梁中华,肖丹,杨霞。一种基于CPLD的SPWM控制波形生成方法[J]。沈阳工业大学学报,2005,27(2):187-191.

[11] 秦继荣,沈安俊。现代直流伺服控制技术及其系统设计[M]。北京:机械工业出版社,1993.

[12] 赵正新,高超。脉冲信号源的CPLD实现方法[J]。电子科技,2009,22(2):47-50.

编辑:jq

全部0条评论

快来发表一下你的评论吧 !