电子说

MIPI全称移动产业处理器接口(Mobile Industry Processor Interface)属于非盈利性组织,关注于开发软硬件标准以满足移动终端的特殊需求。MIPI的目标是通过推动处理器与外设接口的一致性达到简化软硬件的设计与应用的目的,提高移动设备的可重用性与可兼容性。MIPI 为移动设备内的标准硬件和软件接口提供了规范,改善了不同厂商生产的元器件之间的互操作能力,减少了集成工作,加快了移动终端的产品开发周期。

MIPI 技术发展趋势

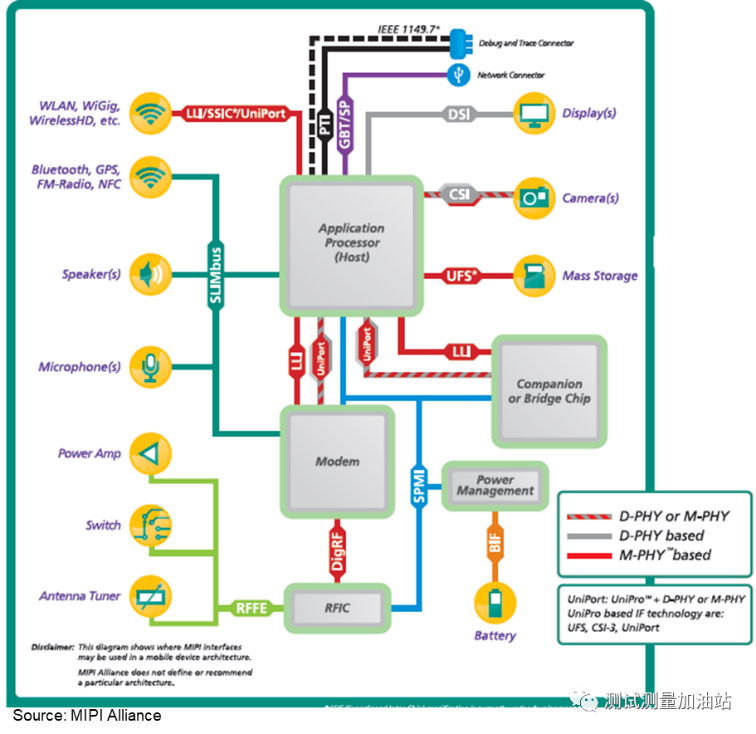

MIPI致力于打造移动产品和汽车电子中的信号互联,在移动产品中深耕多年,尤其是视频流数据传输方面, 应用非常广泛。MIPI联盟标准中有四种物理层标准,分别是D-PHY、C-PHY、M-PHY和A-PHY。

D-PHY是MIPI开发的第一个标准,D-PHY主要用于显示接口DSI和摄像头接口CSI的视频流数据传输。D-PHY是当今智能手机中应用最广泛的视频流接口,也是最广为人知的MIPI标准。M-PHY是家族的第二个成员,M-PHY主要用于数据传输,目前最常用的应用场景是UFS。C-PHY是D-PHY的改良版,其应用场景和D-PHY完全相同,C-PHY在编码方面更加精巧,数据传输效率更高。A-PHY是MIPI 联盟最近宣布采用最新版本的汽车串行器-解串器 (SerDes) 物理层接口,是为车载应用定制的高速标准。在这之前MIPI已经有了整套的通信协议在Camera和Display 领域中大量使用D-PHY、C-PHY、M-PHY进行大数据量的物理传输,但是这个几个物理层协议都无法进行较长距离的传输,A-PHY的设计是为了能跨过整个车辆距离提供数据传输物理层支持。其最大传输距离能够达到15米,而最大传输速度未来能达到甚至超过48Gbps远远超过LVDS的1.5Gbps。A-PHY将帮助汽车行业加速高级驾驶员辅助系统(ADAS)、自动驾驶系统和汽车环视系统的性能。

MIPI D-PHY 基础

D-PHY总线包含了显示与摄像头的DSI与CSI总线。D-PHY 不同于许多现有的移动接口,可以在差分模式( 高速) 和单端模式( 低功率) 之间实时切换,具体视需要传送大量的数据,还是需要节约功率。D-PHY 接口能够以单工或双工配置操作,支持一条数据通路或多条数据通路,可以灵活地提供所需链路。D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

D-PHY Tx 物理层信号实测视频详解

物理层标准:Camera CSI接口和显示屏DSI接口的规范。

两种传输模式:高速(HS)和 低功耗(LP),HS模式下采用低压差分信号,功耗较大,但可以传输很高的数据速率,可支持100mV至300mV的电压范围;LP模式下采用单端信号,数据速率很低,功耗低,支持0V至1.2V信号电平。两种模式的结合保证了MIPI总线既可在需要传输大量数据时高速传输,也可在不需要大数据量传输时处于低速模式能够减少功耗。

传输模式在实际应用中混合交替:信号不断在LP和HS之间切换。

最高数据率:High Speed 模式,80Mbps to 4.5Gbps;Low Power 模式,Up to 10Mbps。

总线端接:50欧姆,高速HS模式;Hi-Z高阻,低速LP模式。

MIPI D-PHY 时序

1. 工作时,LP和HS模式交替出现;LP和HS电平不同,端接电阻不同,data rate不同;

2. LP主要作用是节能,空闲时D-PHY会稳定处于LP11,恒压状态下功耗极低;HS的主要作用是数据传输,使用差分低电压的方式传输信号,使用Double Data Rate的方式(Data: Clock=2:1);

3. LP状态下Data+和Data-可以是相同的逻辑状态,比如从LP到HS,会经历LP11 -> LP01 -> LP00 这三种状态,LP11时Data+和Data-都处于高电平,LP00时都处于低电平;

4. Clock有两种不同的配置: Continuous和Normal,前者设计更简单,后者更节能。

什么是 C-PHY?

C-PHY发送端有High、Mid、Low三种信号电压高度,接收端计算AB、BC、CA间的差值做解码,同时恢复时钟,C-PHY有5种状态转移的可能。与D-PHY以0、1的电平表示编码不同,C-PHY用状态的跳转表示编码,每个符号可编码的数据为log25= 2.3219bit/sym,理论上的带宽是D-PHY的2.3219倍,编码效率大大提升。

MIPI D-PHY 和C-PHY 时序比较

D-PHY是源同步系统,有同步时钟通道,C-PHY没有同步时钟,时钟是嵌入数据当中。D-PHY和C-PHY的物理层结构是不同的,从线路上看,C-PHY是A、B、C三线系统。由于MIPI C-PHY不传输时钟,需要CDR先恢复时钟,然后再用恢复的时钟去采样数据并寻找同步头。

MIPI D-PHY 测试挑战

MIPI D-PHY总线工作于LP与HS两种工作状态:LP(Low Power)状态,工作速率最高不超过10Mbps,信号摆幅1.2V,端接阻抗为高阻;HS(High Speed)状态,工作速率从80Mbps到4.5Gbps,信号摆幅200mV,端接阻抗为50欧姆。由于信号摆幅的差异,使得D-PHY信号测试所需的动态范围较高,并且其对噪声的容限较低,在实际的测试中信号质量可能不会太理想,见下图。

MIPI信号测试难点

1. CTS 测量项繁多: 64 for D-PHY, 41 for C-PHY

2. HS和LP两种完全不同的工作模式下的信号完整性和相应时序

3. 使用探头焊接的方式测量

4. 测量精度:使用可靠的算法筛选出特定波形并进行精确测量

5. 被测波形有时候很差

6. 自动检测跳变沿,测量项目

7. 最小化探头的负载效应

8. 板子密度越来越高,测试点很难焊接

9.自动测试设置,适应HS和LP模式

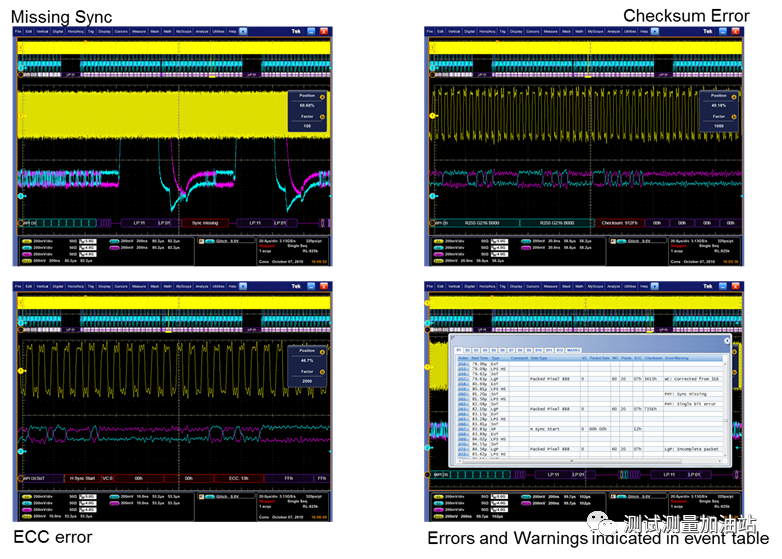

MIPI D-PHY 解码

在实际调试工程中,工程师通常需要找到设备不正常工作的原因,不仅需要D-PHY物理层信号的一致性测试,还需要对D-PHY信号的串行触发与解码功能,下面是D-PHY信号的解码、同步与错误告警以及协议事件列表导出功能,为D-PHY信号的开发与调试提供了极大的便利。

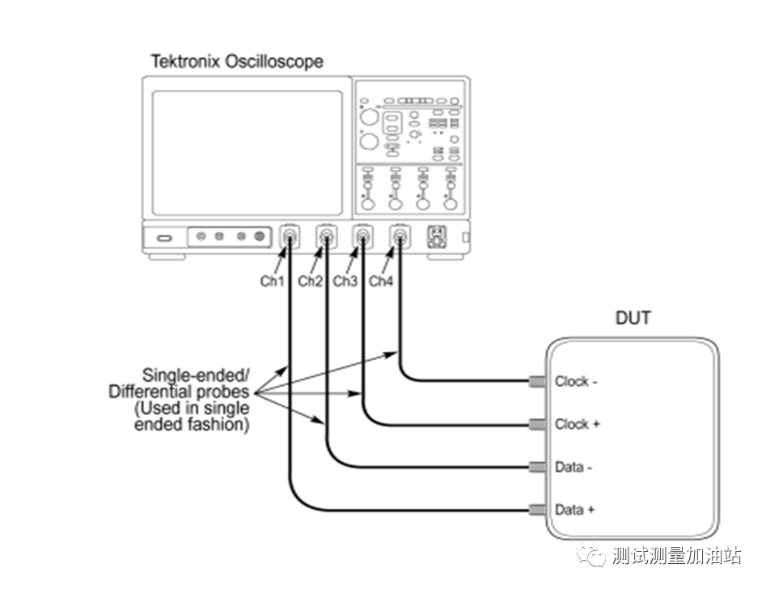

D-PHY Tx 信号测试和连接图

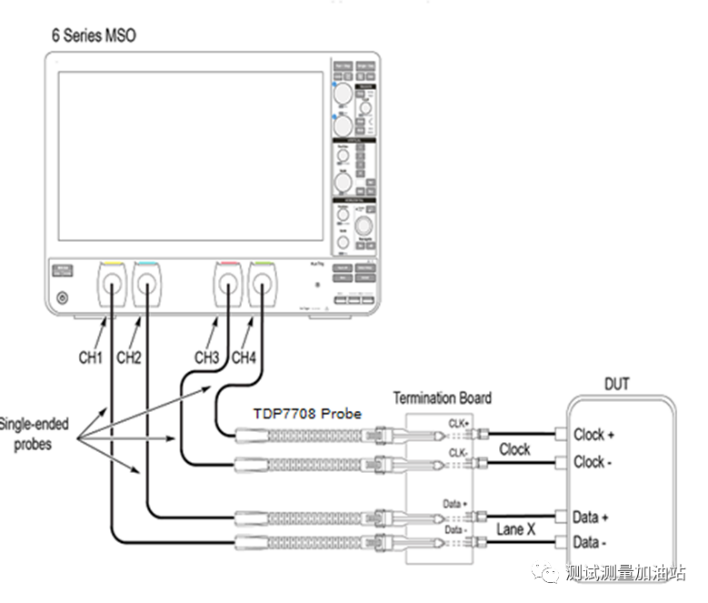

针对MIPI D-PHY多条差分总线的测试,需要利用三根或四根探头完成对数据和时钟信号的探测,如果时钟是连续时钟,至少需要三根探头完成探测,如果时钟是Normal非连续时钟,需要四根探头完成测试;然后利用 D-PHY Tx物理层一致性测试软件完成全自动化测试。

大多数情况采用左下图的连接方式。待测物是一个完整的系统,里面包含D-PHY的Controller和Device,探头在不破坏系统工作状态的情况下,连接待测物并测量信号质量;如果被测的芯片,可能采用右下图的连接方式,芯片通过评估板来测量信号质量,只有一个D-PHY controller 芯片和一些外围电路,通过评估板上的SMA接头将信号引出。需要在评估板外接一块终端板(Termination Board)来提供D-PHY的动态端接,探头连接在端接板上的测试点进行信号观测。

D-PHY 实测眼图

C-PHY 实测眼图

D-PHY Tx 物理层测试参考配置

小结

MIPI D-PHY Tx物理层信号一致性测试需要利用三根或四根探头完成对数据和时钟信号的探测,然后利用实时示波器和 D-PHY Tx物理层一致性测试软件完成全自动化测试,提高了测试效率, 从而帮助工程师快速验证产品,加速产品市场化的过程。

全部0条评论

快来发表一下你的评论吧 !