挑战:

在设计ATE Load Board的时候我们经常会遇到大电流的电源设计,这些大电流能够达到数百安培级别,这给我们的电源完整性(PI)设计带来了极大的挑战。一个理想的测试系统电源应该具有无电流限制,没有纹波,没有延时的特点。但实际测试系统中,特别是PCB上的电源路径存在很多阻抗,容抗,感抗,会极大的影响电流电压的响应能力,特别是在快速大电流变换的时候。

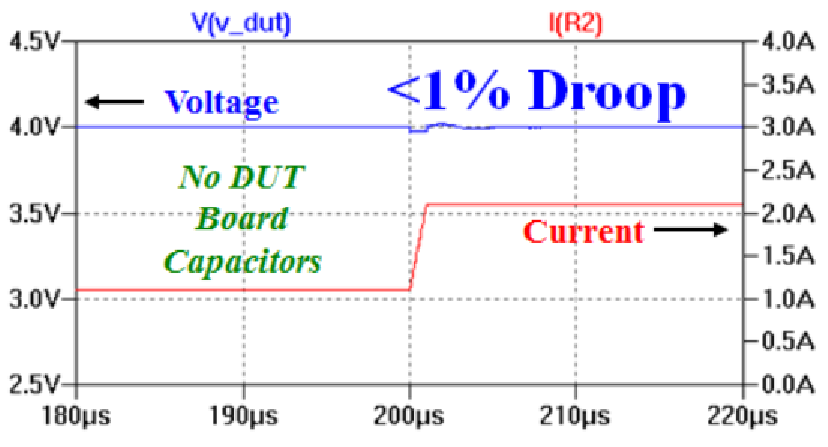

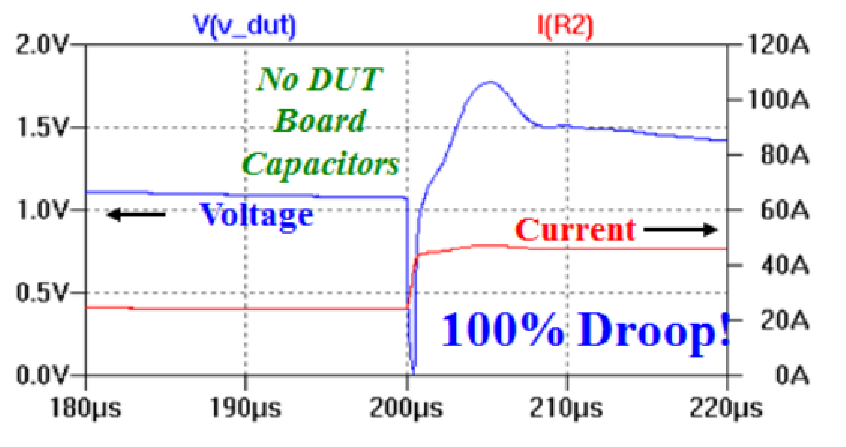

下图显示了小电流和大电流的两种情形:

1小电流:电流变换是无明显电压drop

2大电流:电流变换时出现明显电压drop。ATE测试时,电压drop会引起芯片复位,造成测试状态丢失

季丰拥有丰富的大电流Load board设计经验,下面我们从原理图设计和layout设计两方面来讲述如何应对ATE Load board大电流设计的问题。

在原理图设计方面需要注意以下几个方面:

确定大电流电源需要使用的DPS种类后分配足够的通道数;

根据对应DPS总类和通道数计算好电容总量;

根据对应电源的的Spec分配好电容种类与数量,使用更多的低值电容,而不是更少的高值电容。

在layout设计方面需要注意以下几个方面:

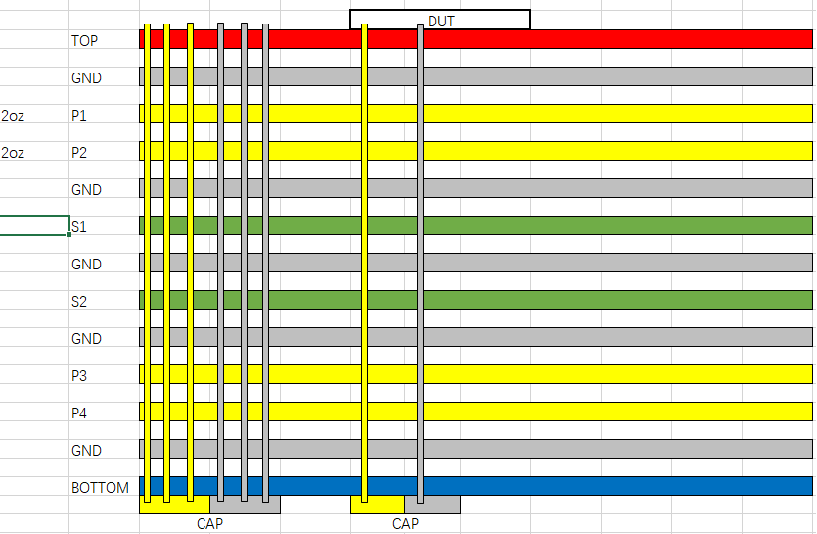

根据待测芯片的封装类型在DUT设置尽量大的过孔类型;

根据电容封装类型设置上数量多和尺寸大的过孔;

DUT每个电源pin上需要放上对应的小容值电容;

其他电容根据电容容值大小依次放置在对应的电源路径上;

叠层方面让电源和地平面成为相邻的平面层,平面之间的介质要尽量薄,形成电容效应;让电源平面更靠近DUT侧;

电源平面设置多层且2oz以上铜厚。

通过仿真确定电源完整性(PI)

除了以上通用的需要注意的地方,还有许多case by case的设计细节,硬件设计工程师会针对不用DUT及电源配置做设计优化。

原文标题:ATE Load Board大电流设计

文章出处:【微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !