电子说

ADAS的技术使驾乘体验更舒适、更安全、更智能。TI Jacinto TDA4VM&DRA829处理器是TI最新一代的处理器,以先进的高集成度和多核异构的高性能处理能力,展现了其灵活的处理能力和极具竞争力的成本,为ADAS技术实现提供了极具竞争力的平台。 在ADAS的应用中,摄像头作为感知模块,越来越多地摄像头被部署在应用中,感知能力的大小对应用来说至关重要,因此,本文将介绍Jacinto7处理器摄像头接入和ISP的处理能力。

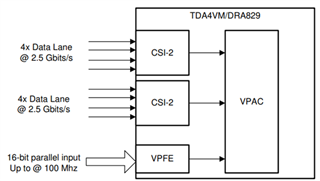

Jacinto7 TDA4VM/DRA829摄像头接入子系统包含了2x MIPI CSI-2接口 和video processing front end(VPFE),可以支持多个摄像头的接入。

图1 : TI Jacinto7摄像头接入子系统

对于MIPI-CSI2接口支持情况如下:

– Protocol stack for MIPI CSI2

– Supports all MIPI supported formats

– Companied or linear

– Real-time priority on I/F port traffic

VPFE输入接口模块用于接收原始图像、视频数据、YUV等数字图像数据。VPFE支持的功能如下:

– Generates HD/VD timing signals and field ID to an external timing generator or can synchronize to the external timing generator

– Support for progressive (non-interlaced) and interlaced sensors

– Support for up to 110-MHz sensor clock.

– Support for REC656/CCIR-656 standard (YCbCr 422 format, either 8- or 16-bit).

– Support for YCbCr 422 format, either 8- or 16-bit with discrete HSYNC and VSYNC signals.

– Support for up to 16-bit input.

因此,从图像接入来说,TDA4VM/DRA829 MIPI-CSI2的每个接口有10Gbps 的带宽,两个MIPI-CSI2有20Gbps的带宽,每个CSI2接口支持16个Virtual Channels,因此两个CSI2接口可以支持多达32路摄像头。EVM可以方便展示多达8路2M摄像头的接入。

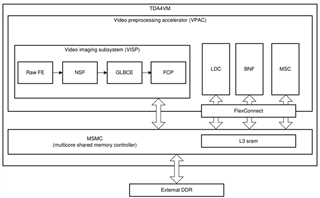

Jacinto7集成了视觉预处理加速器Vision Pre-processing Accelerator(VPAC), 提供了常用的图像处理功能,比如颜色处理和增强、噪声过滤、宽动态(WDR)、镜头畸变矫正、图像金字塔、图像缩放等。基于TI 超过20年在数百万种产品中部署的多个Soc系统,TI发布了最新一代的成像系统,即德州仪器第七代ISP,并被集成在了Jacinto7 TDA4VM和DRA829处理器。

如图2 VPAC系统框图所示,由以下主要模块组成:

图2 : TI Jacinto7 VPAC 系统框图

VISS(Video Imaging Subsystem)模块主要处理RAW数据并输出RGB或YUV图像。其包含RAW FE(Raw Front End)、NFS(Noise Filter)、GLBCE(Global and Local Brightness Contrast Enhancement)、FCP(Flex Color Processing)等模块。

LDC(Lens Distortion Correction)主要对图像进行畸变矫正。

MSC(Multi-Scalar)主要功能是对图像进行缩放。

BNF(Bilateral Noise Filtering)双边滤波去除噪声。

TDA4VM的VPAC的处理能力是720MP/s,因此理论上可以对24M RAW摄像头的数据进行处理。

Jacinto7 的用户经常会问TDA4VM/DRA829能够接几个摄像头,有几个ISP,ISP能够处理几路摄像头的问题。 通常我们经常使用MIPI-CSI2接收图像,使用VPAC里面VISS对RAW图像进行处理。TDA4VM/DRA829处理器有两个CSI-2接口,一个ISP, ISP可以分时处理多路图像, 其吞吐量如下表所示:

|

IP |

Max Throughput |

|

CSI-2*2 |

10Gbits*2 |

|

VPAC |

720 MP/s |

当前的SDK中已经支持摄像头查看Release Notes(https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/latest/exports/docs/imaging/imaging_release_notes.html#ImageSensor_Support)

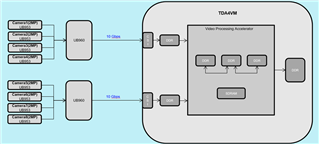

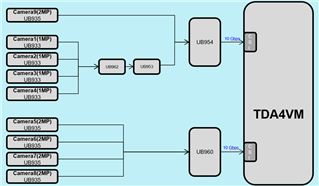

Jacinto7 SDK支持Multi Camera Use Case,其系统框图如图3所示,该Demo同时可以接入8个2MP@30FPS摄像头,摄像头先通过FPD LINK串化器UB953,然后通过同轴接入FPD LINK解串器UB960,最后通过TDA4VM MIPI-CSI2接口接入TDA4VM进行图像处理。

该Demo可以在EVM快速搭建,需要TDA4VM EVM、Fusion Board(摄像头接口板)和8个AR0233或IMAX390摄像头。

图3 : TDA4VM Multi Camera Use Case 1

该Use Case的利用率如下8*2MP@30FPS(RAW12):

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

2.88 Gbits |

28.80% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

480MP/x |

66.66% |

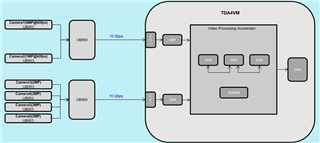

当前的ADAS应用中,有4个2MP@30FPS摄像头实现全景,1个8MP@30FPS实现前视,另外一个摄像头完成DMS或后视功能。一个前视摄像头其系统框图如图4所示:

图4 : TDA4VM Multi Camera Use Case 2

该Use Case的利用率如下:

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

3.6 Gbits |

36% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

540MP/x |

75% |

在Jacinto7里面如果超过8个摄像头应该怎么接呢?假如依旧使用TDA4VM CSI2的两个接口,如果是9个或9个以上的摄像头,需要如何接呢?FPD LINK有Cascading的功能,如下方案采用FPD LINK Cascading的功能,其系统框图如图6所示:

图6 : TDA4VM Multi Camera Use Case 3-2

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

2.16 Gbits |

21.6% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

420MP/x |

60% |

摄像头的接入和处理能力对用户方案至关重要,因此,本文对Jacinto7 TDA4VM/DRA829处理的摄像头接入和处理能力进行了概述,并使用实际的Use Case 介绍了摄像头的接入和处理方案,用户可以根据实际应用需求对文中的方案进行修改。对于其它的Jacinto7的处理器,比如TDA4VL、TDA4AL、TDA4VMECO、TDA4VH、TDA4AH等处理器,本文也同样适用,需要注意的是不同处理器的CSI和VPAC带宽的不同,性能有所差异,因此需要根据带宽进行换算。

全部0条评论

快来发表一下你的评论吧 !