PCB设计

一直以来,想写点关于PCB走线相关的基础知识。信号完整性的工作,很大一部分基于PCB走线规则的设定以及走线优化。仿真工作或者说后仿的工作都是基于PCB设计已经定型的情况下进行的,也就是说链路的相关风险已经固定了。所以,设定规则来管控风险比出现风险解决来得更重要。预防管控的能力是未来信号完整性工程师的必备基础技能。

预防管控PCB走线的风险,最最基础的知识就是熟知常用走线规则。

线长匹配

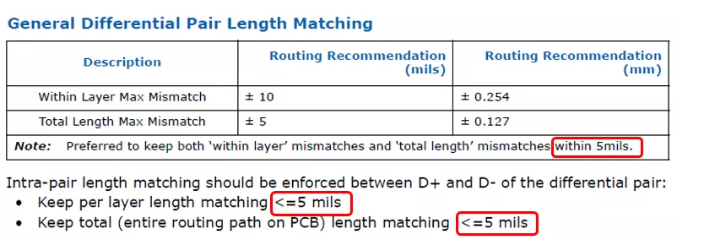

总长线长匹配&分层线长匹配

总长线长匹配的5 mils已经在很多产品设计中有应用,这也是很多设计准则里提到的。

分层线长匹配的概念好像没有那么普遍,差分线的走法,BGA区域打过孔到内层,内层走线打过孔到终端,内层阻抗相对容易管控和差分线走线对称性缘故,一般情况下,表层两段距离相对比较短,所以长度的匹配一般在内层进行,也就是间接实行了分层线长匹配。很多时候,这种分层线长匹配的概念在很多产品的设计中被忽略了。

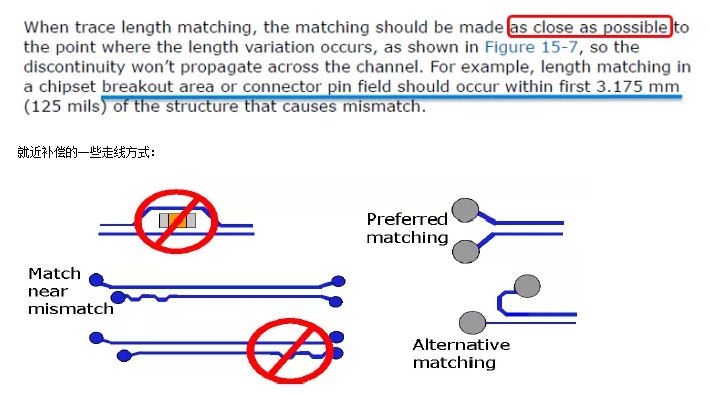

就近补偿

当长度不匹配发生时,推荐就近补偿,防止不连续的传播。如何就近长度匹配,产品的分类不同,要求也不同,消费类产品没有给出相关建议,只是对BREAKOUT区域以及连接器的PIN区域,给出了相关建议的数值。

匹配样式

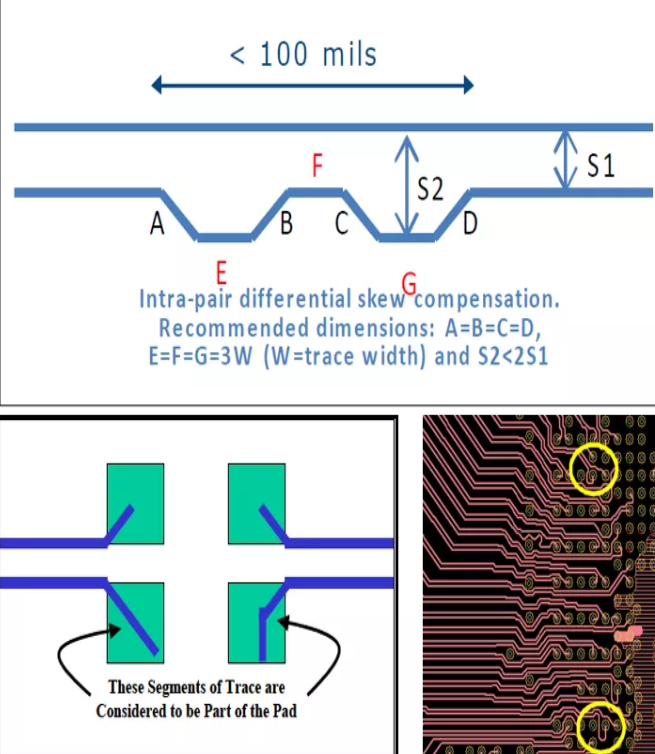

常见的匹配样式有蛇形线,PAD区域内走线等,蛇形线中3W2S原则是很多产品设计中常用的绕线方法,通过这样的操作,来达到线长匹配。

3W2S有些相互关系的,建议还是搞清楚点。相对于3W2S故意绕线来达到线长匹配,PAD区域走线匹配的方式对匹配所带来的影响更小。

需要注意的是:线长匹配最终目的是等时。

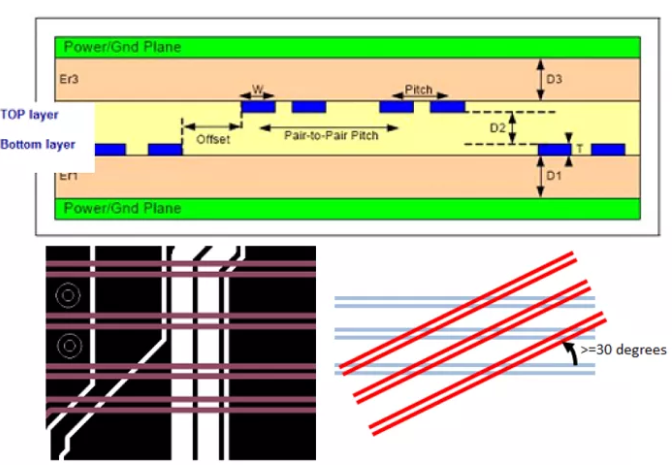

双带线

高速产品的轻薄化,PCB厚度限制了走线层数,就有了高速线走在相邻两层上,为了减少相互的串扰,走线的方法有间距管控(DDR部分实现难度比较大),垂直走线(这种方法实现难度比较大),30度角走线。

双带线是未来产品设计的一大趋势,细节性的东西很多,比如双带线相互平行重复度及长度等。

差分转换过孔

差分转换过孔 Differential Transitional Via

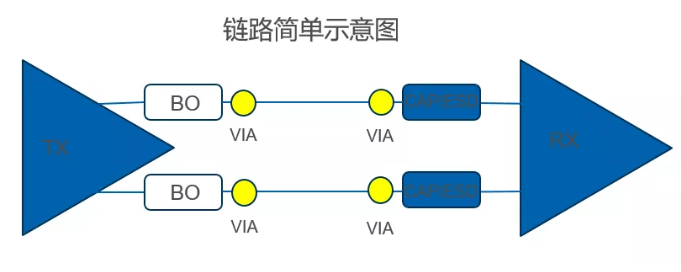

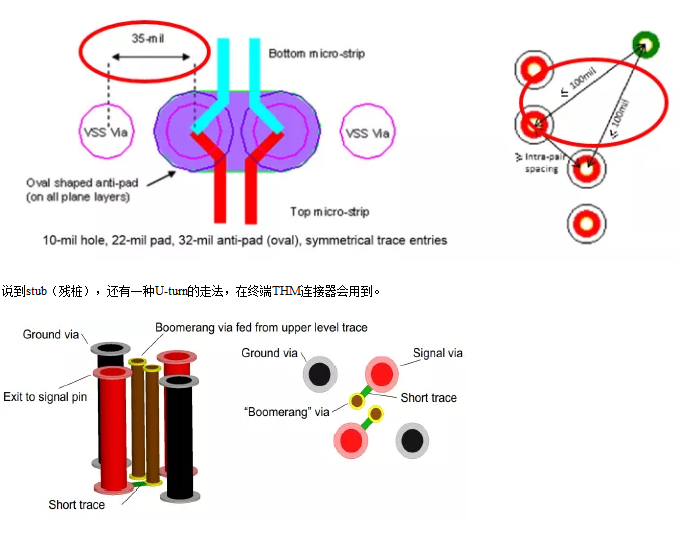

PCB走线,过孔是不可缺少的部分,这里不讲盲埋孔之类,只讲差分过孔处理方式。

不同产品有不同的设计细则,但大体是相通的:

1.如果差分过孔stub(残桩)较长,信号的速率比较高(比如PCIe4.0),要做Backdrill(背钻);

2.差分过孔如果转换参考层,要打回流地孔,地孔到VIA的距离要大于本身的差分过孔距离,同时地孔要在100 mils以内。

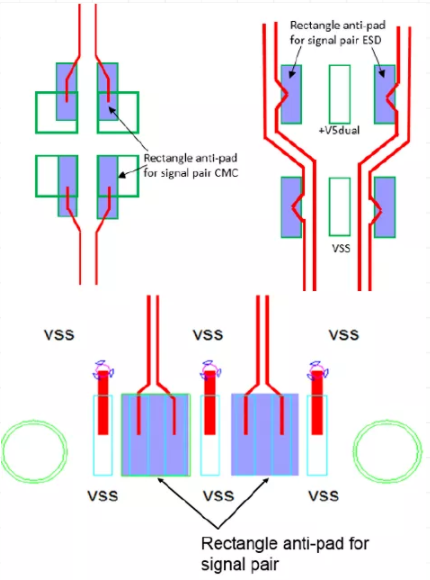

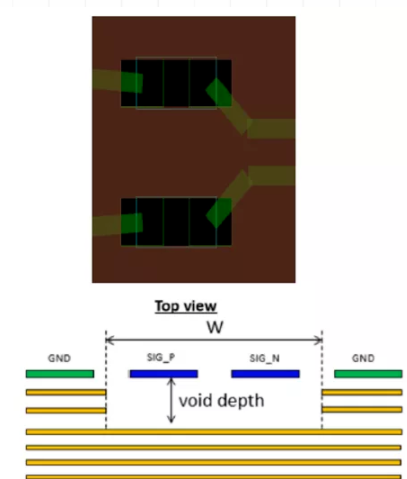

器件封装平面挖空

这里说的器件不仅仅是USB中要用的Electrostatic Diode (ESD) 和Common-mode choke(CMC),也包括高速链路中的匹配电阻,还有耦合电容,还有SMT连接器等。对其进行优化,是减少阻抗的突变。

优化处理的方式就是相邻平面层进行挖空。

总结

以上便是以一条简单的高速链路路径举例,列举PCB走线相关常用规则。当然针对不同产品会有不同细则,殊途同归,所有的规则都是为了减小串扰,反射,损耗等,来保证信号完整性。如果遇到一些规则相互矛盾,这个时候就需要信号完整性工程师做出取舍,给出合理方案。

全部0条评论

快来发表一下你的评论吧 !