VHDL和Verilog数组的定义、初始化、赋值的方法不只一种,以下是本人常用的方法,可能不是最方便的,但是比较好理解,文中包含了源代码和modelsim仿真,供大家参考学习。

1. VHDL数组定义、初始化、赋值

1)VHDL数组定义方法:通过TYPE定义个matri_index的数组,数组包含50个数据,数据位数为16;申明了receive_data和send_data两个matri_index的数据。

--define a 16 bit array

constant

matrix_num:

integer := 49; TYPE

matrix_index is array (matrix_num downto 0) of std_logic_vector(15 downto 0);signal

receive_data, send_data:

matrix_index;signal

send_cnt:

STD_LOGIC_VECTOR(7 downto 0);

2)VHDL数组初始方法:实际应用里,通常需要在上电复位过程中对变量进行初始化,如果数组个数少时,直接赋初始值即可,但是数组个数多时,可以用循环实现赋值,通常的循环语句有FOR LOOP和WHILE LOOP。

(注意变量i申明的位置,需要在process内部,注意变量的赋值方式)

process(clk,reset_n)

--循环变量定义并初始化

variable i: integer := 0;

begin

if (reset_n = ‘0’)then

i := 0;

--利用while loop循环赋值

while(i《=matrix_num) loop

receive_data(i) 《=X“0000”;

i := i+1;

end loop;

elsif (rising_edge(clk)) then

--CONV_std_logic_vector(A,位宽)

将无符号的无符号整数转换为std_logic_vector

--CONV_INTEGER(A)

将std_logic_vector转换为整数

--直接赋值方式

send_cnt《= X“02”;

send_data(0) 《= X“0000”;

send_data(1) 《= X“0000”;

send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

end if;end process;

3)VHDL数组赋值

赋值语句分信号赋值语句和变量赋值语句两种。每一种都有下面三个基本组成部分:赋值目标:是所赋值的受体,它的基本元素只能是信号或变量。

赋值符号:是赋值符号只有两种。一种是信号赋值符号”《=”;另一种是变量赋值符号”:=”。赋值源:赋值源是赋值的主体,它可以是一个数值,也可以是一个逻辑或运算表达式。

可以直接赋值,如果变量为矢量时,需要将矢量转为整型。(不管三七二十一,建议程序中增加以下包,否则类型转换用不了)

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;USE ieee.std_logic_unsigned.all;--CONV_std_logic_vector(A,位宽)

将无符号的无符号整数转换为std_logic_vector--CONV_INTEGER(A)

将std_logic_vector转换为整数 --直接赋值方式

send_cnt《= X“02”;send_data(0) 《= X“0000”;send_data(1) 《= X“0000”; send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

4)VHDL数组test代码

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;USE ieee.std_logic_unsigned.all; --this is commentENTITY array_test IS PORT( reset_n

: IN STD_LOGIC;

clk

: IN STD_LOGIC );

END array_test; ARCHITECTURE behavioural OF array_test IS--define a 16 bit array

constant

matrix_num:

integer := 49; TYPE

matrix_index is array (matrix_num downto 0) of std_logic_vector(15 downto 0);signal

receive_data, send_data:

matrix_index;signal

send_cnt:

STD_LOGIC_VECTOR(7 downto 0);BEGIN process(clk,reset_n)

--循环变量定义并初始化

variable i: integer := 0;

begin

if (reset_n = ‘0’)then

i := 0;

--利用while loop循环赋值

while(i《=matrix_num) loop

receive_data(i) 《=X“0000”;

i := i+1;

end loop;

elsif (rising_edge(clk)) then

--CONV_std_logic_vector(A,位宽)

将无符号的无符号整数转换为std_logic_vector

--CONV_INTEGER(A)

将std_logic_vector转换为整数

--直接赋值方式

send_cnt《= X“02”;

send_data(0) 《= X“0000”;

send_data(1) 《= X“0000”;

send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

end if;end process; END behavioural;

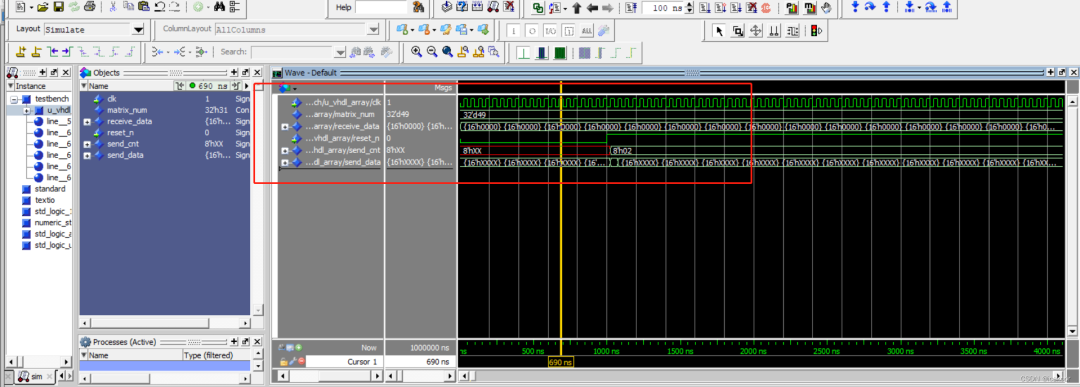

5)modesim 仿真结果

2. Verilog数组定义、初始化、赋值

1)Verilog数组定义方法:reg[n-1 : 0]

定义了存储器中每个寄存器单元的大小,即存储单元是一个n位的寄存器;存储器后面的[m-1 : 0]则定义了该存储器中有多少个这样的寄存器。

reg[n-1 : 0] 存储器名 [m-1 : 0];或者 reg[n : 1] 存储器名 [m : 1];

//define a 16 bit array parameter wordsize = 16, memsize = 49;reg [wordsize-1 : 0] send_data[memsize-1 : 0], receive_data[memsize-1 : 0];integer i = 0;reg [7:0] send_cnt

;2)Verilog数组初始方法:实际应用里,通常需要在上电复位过程中对变量进行初始化,如果数组个数少时,直接赋初始值即可,但是数组个数多时,可以用循环实现赋值,通常的循环语句有FOR和WHILE。

(注意变量的赋值方式)

always@(posedge clk, reset_n)beginif(!reset_n) beginwhile(i 《=memsize)beginreceive_data[i] 《= 16‘h0000;i = i+1;

//阻塞赋值endendelse begin

//直接赋值方式send_cnt 《= 8’h02;send_data[0] 《= 16‘h0000;send_data[1] 《= 16’h0000;send_data[send_cnt] 《=16‘h0000;

//不需要类型转换endend

3)Verilog数组赋值不像VHDL那样,可以直接赋值。

//直接赋值方式send_cnt 《= 8’h02;send_data[0] 《= 16‘h0000;send_data[1] 《= 16’h0000;send_data[send_cnt] 《=16‘h0000;

//不需要类型转换

4)Verilog数组test代码

module verilog_test(clk,reset_n);inputclk;inputreset_n; // /////define a 16 bit array parameter wordsize = 16,

memsize = 49;reg [wordsize-1 : 0] send_data[memsize-1 : 0],

receive_data[memsize-1 : 0];integer i = 0;reg [7:0] send_cnt; always@(posedge clk, reset_n)beginif(!reset_n) beginwhile(i 《=memsize)beginreceive_data[i] 《= 16’h0000;i = i+1;

//非阻塞赋值endendelse begin

//直接赋值方式send_cnt 《= 8‘h02;send_data[0] 《= 16’h0000;send_data[1] 《= 16‘h0000;send_data[send_cnt] 《=16’h0000;

//不需要类型转换endendendmodule

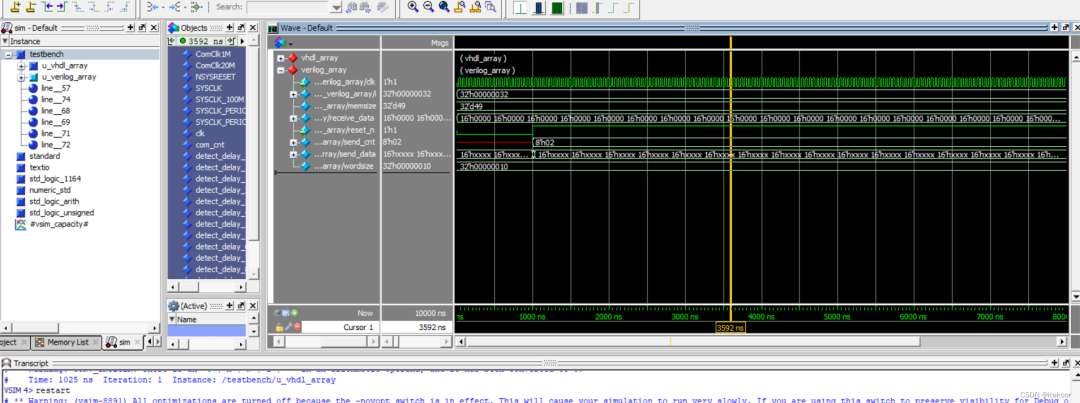

5)modelsim仿真结果

审核编辑 :李倩

全部0条评论

快来发表一下你的评论吧 !