为啥又看反相器呢,因为想做PLL,锁相环里有PD,PD里面有锁存器,锁存器里有NAND,而NAND里又是基于反相器。所以喽。

反相器,是数字电路中的基本器件。

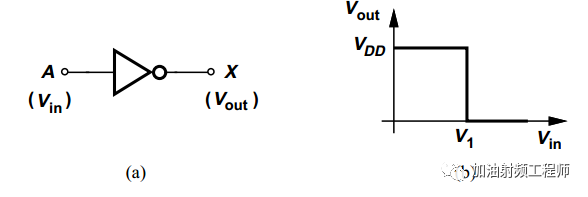

上图是理想的反相器。

当Vin=0时,Vout=VDD;

当Vin=VDD时,Vout=0;

Vout在VDD和0之间跳变。

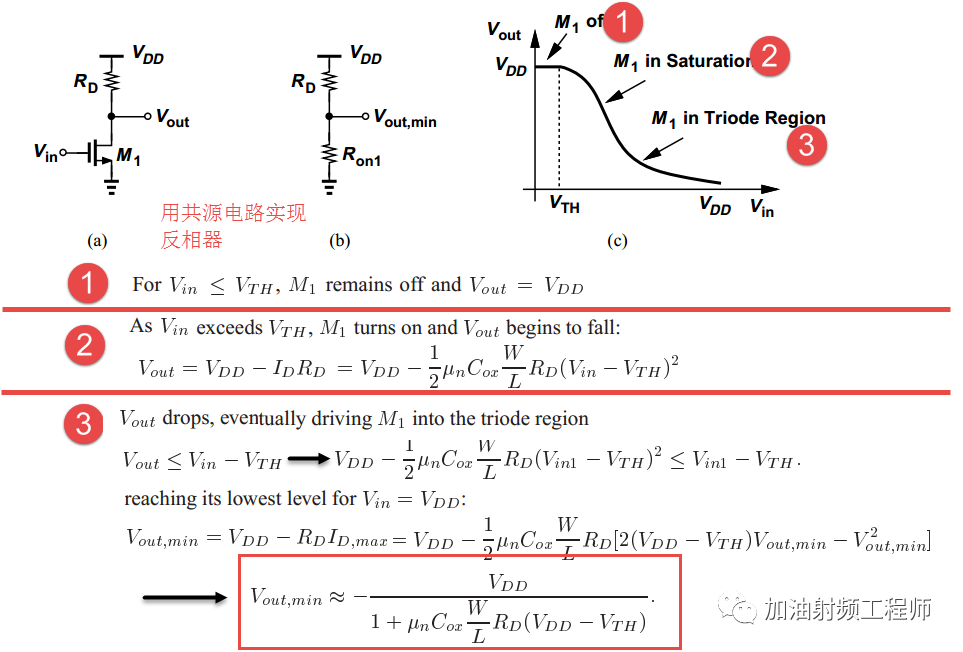

但实际中,不可能实现跳变,即Vin在V1附件一个非常微小的变化,使得Vout从VDD变为0,则表示电路的电压增益在此时是无限大的;但实际上,电路增益一直是个有限的值,所以实际电路中,Vout只会从VDD渐变至低,至于低电平是多少电压,则取决于设计。

可以看到,输出的低电压与W/L和RD相关,因为分母中的式子不可能为无穷大,所以输出的低电平只能接近于0,但是到不了0。

虽然用共源电路可以实现反相器的基本性能,但是它确不常用,为什么呢?

因为它具有三个致命的缺陷:

(1) RD的值,必须远大于晶体管所呈现出来的电阻Ron. 因为当想要输出低电平时,Vout=Ron*VDD/(RD+Ron),所以为了使得低电平足够低,则要求RD>>Ron

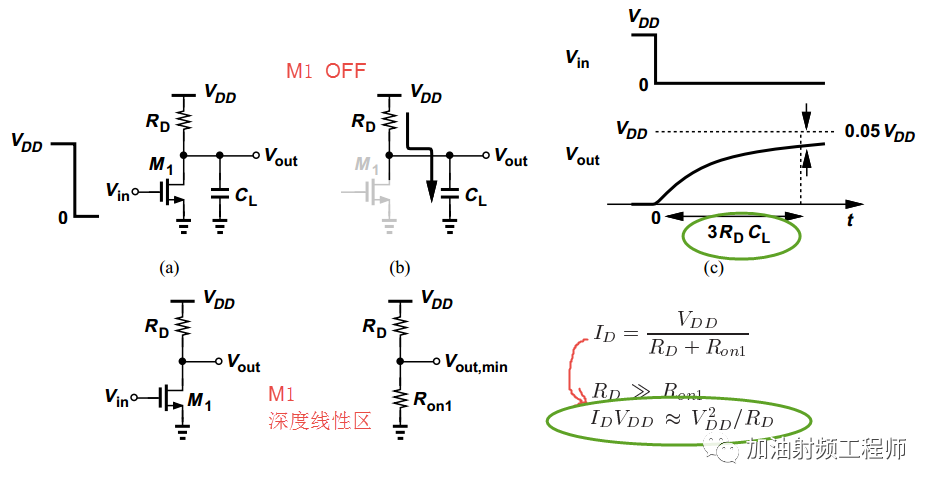

(2) 因为RD的存在,使得反相器的速度和功耗不能兼得。如下图,可以看到,当想提高速度时,则需要降低RD,但是此时功耗又上升。

(3) 如果反相器输出为低电平时,反相器的功耗为 VDD*VDD/RD

这三点中,最要命的是第三点。

在大型数字电路中,有一个静态功耗,就是指电路不动作时的功耗,而NMOS反相器(共源电路实现的反相器)的静态功耗为VDD*VDD/RD。

比如说,一个大型数字芯片,有1百万个门电路,其中有一般是处于低电平输出状态,假设VDD=1.8V,RD=10kohm,则静态功耗高达 162W,这个显然不能接受。

而这三点缺点,则主要是与上拉电阻RD有关。

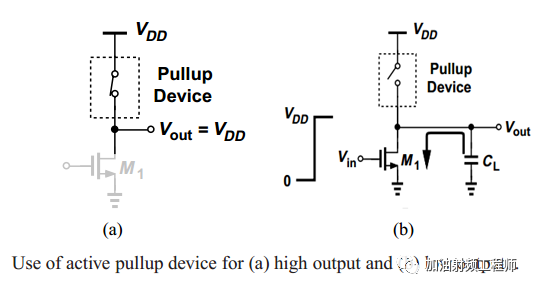

所以,如果能找到这样一个器件,当M1关断时,该器件将输出与VDD相连,最好该器件的电阻很低;而当M1打开时,该器件关断,这样就没有电流从VDD流向地。即如下图所示。

那什么器件能担当此重任呢?

那就是PMOS。

把PMOS和CMOS合体,形成的反相器,称之为CMOS反相器。

CMOS反相器的输出低电平基本为0,因为当Vin=VDD时,M2关断。而NMOS的低电平永远都不可能为0。

CMOS在高电平输出和低电平输出的状态下,静态功耗都为0,;而NMOS在低电平输出状态下,有静态功耗。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !