传感器

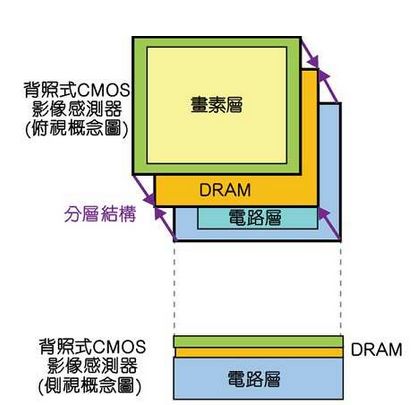

为了加速影像数据处理, 业界研发了在互补金属氧化物半导体(CMOS)影像传感器中配备嵌入式动态随机存取存储器(DRAM),推出了配备DRAM的三层堆叠式CMOS影像传感器,SONY是最早发布这一产品的厂家,这款型号为IMX400的三层堆叠式感光元件(Exmor RS)是专为智能手机而打造的。

SONY的堆叠式CMOS传感器元件

Sony的Xperia XZ Premium和Xperia XZ两款旗舰级智能手机搭载了具有960fps画面更新率的Motion Eye相机模组。

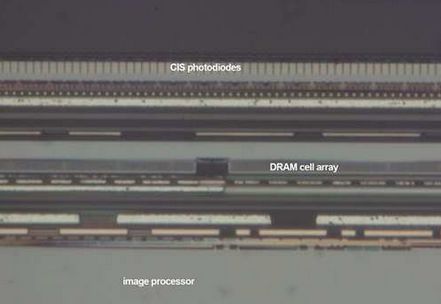

这款三层堆叠的CMOS影像传感器(CIS)被面对背地安装在DRAM上,使得DRAM与影像讯号处理器(ISP)面对面接在一起。

Sony三层堆叠式CMOS影像传感器的芯片横截面

Sony在其较早的19Mp影像传感器中使用双模拟/数位转换器(ADC),为画素资料进行数字化。而今,该公司使用4层ADC的结构提高读取速度,同时也改善了处理能力。

DRAM则用于暂时储存高速数据,然后再以传感器介面的最佳速率输出。

该设计使其能以1/120秒读取1,930万画素的静态影像,而在影片模式下可达到1,000fps的画面更新率,较以往产品的静态影像与动态影片分别提高了4倍和8倍的速度。Sony可说是再次将手机相机的功能推至极限。

Sony新开发配备DRAM的三层堆叠式CMOS影像传感器

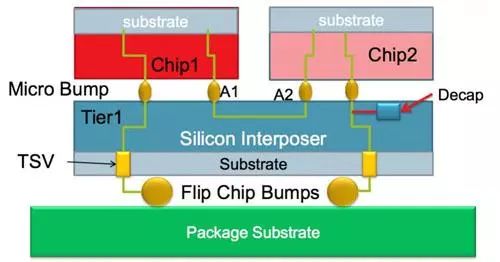

3D堆叠技术

3D 堆叠技术是把不同功能的芯片或结构, 通过堆叠技术和过孔互连等微机械加工技术, 使其在 Z轴方向上形成立体集成和信号连通以及圆片级、芯片级、硅帽封装等封装和可靠性技术为目标的三维立体堆叠加工技术, 用于微系统集成, 是继片上系统( SOC) 、多芯片模块( MCM ) 之后发展起来的系统级封装( SiP/ SoP) 的先进制造新技术。

微电子的模块已经实现 3D 圆片级封装( WLP)的 系统级封 装 ( SiP ) 技术, 例如, CIS RF 模块、M EM S 封装、标准器件封装, 已有量产, 2009 年开始 3D TSV 堆叠时代( 3D TSV Stack Era ) 的到来,模块化芯片、闪存及 DRAM , 通过堆叠以获得增强的内存容量。

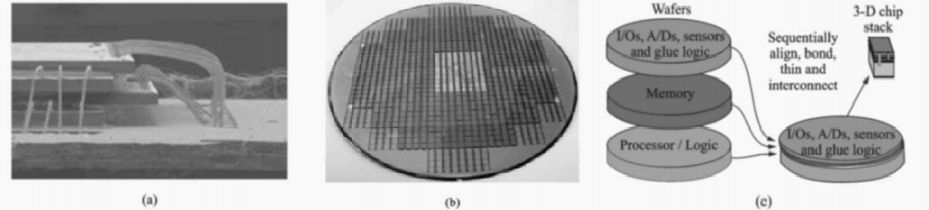

3D 堆叠的主要形式和分类

目前有多种基于 3D 堆叠方法, 主要包括: 芯片与芯片的堆叠( D2D) 、芯片与圆片的堆叠( D2W ) 以及圆片与圆片的堆叠( W2W) 。

D2D 堆叠方式是当前系统级封装( SiP) 方式的主要互联方式, 该堆叠方法主要利用引线键合的方式, 实现3D 方向芯片间的互联, 如图( a) 所示。D2D 方式虽然可以实现3D 堆叠, 提高系统集成度, 但由于主要使用引线键合方式互联, 限制了系统集成度进一步提高, 并由于引线会引入寄生效应, 降低了 3D 系统的性能;

D2W 堆叠方式利用芯片分别与圆片相应功能位置实现3D 堆叠,如图( b) 所示, 该种方式主要利用 flip-chip( 倒装)方式和bump( 置球) 键合方式, 实现芯片与圆片电极的互联, 该方式与 D2D 方式相比, 具有更高的互联密度和性能, 并且与高性能的 flip-chip 键合机配合,可以获得较高的生产效率;

W2W 堆叠方式利用圆片与圆片键合, 实现3D 堆叠, 在圆片键合过程中, 利用 TSV 实现信号的互联, 如图( c) 所示, 该种方式具有互联密度高、成本低并且可同时实现圆片级封装( WLP) 的优点, 可以实现 AD、I/ O、传感器等多功能器件的混合集成。

对于 D2W 和 W2W 堆叠方式,从生产效率的角度, W 2W 方式效率最高, 但从成品率角度考虑, 由于 D2W 方式可以通过筛选, 实现合格芯片( Know good die, KGD) 之间的堆叠, 因此成品率较高; 而 W2W 方式, 无法通过实现事先筛选,

会严重影响堆叠的成品率。

对于 W2W 堆叠方式, 必须严格控制芯片及 3D 堆叠工艺的成品率, 否则, 随着堆叠层数的增加, 成品率将大幅下降。对于一个需要 3 层的堆叠工艺来说, 必须将圆片成品率及层叠成品率均控制在 98%以上, 才可能获得 90%以上的 3D 堆叠成品率。

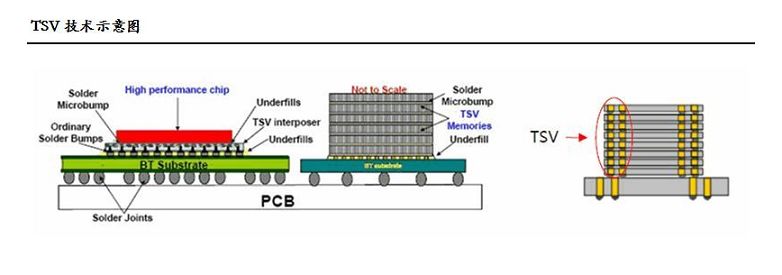

层间互联技术——TSV

从微电子技术的发展趋势看, 基于 TSV 技术的3D 堆叠技术, 将是微电子技术发展的必然趋势, 但也面临许多技术挑战, 如 TSV 技术、超薄片加工技术( 临时键合、减薄等) 、异质键合技术、层间对准技术等等, 其中, TSV 技术最为关键。

穿透硅通孔( TSV) 将在先进的三维集成电路( 3D IC) 设计中提供多层芯片之间的互连功能, 是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通, 实现芯片之间互连的最新技术。

与以往的IC 封装键合和使用凸点的叠加技术不同, TSV 能够使芯片在三维方向堆叠的密度最大、外形尺寸最小, 并且大大改善芯片速度和降低功耗的性能。

采用硅通孔技术( TSVs) 的堆叠器件

TSV 与目前应用于多层互连的通孔有所不同,一方面 TSV 通孔的直径通常仅为为 1~100 μm , 深度 10~400 μm, 为集成电路或者其他多功能器件的高密度混合集成提供可能; 另一方面, 它们不仅需要穿透组成叠层电路的各种材料, 还需要穿透很厚的硅衬底, 因此对通孔的刻蚀技术具有较高的要求。

目前制造商们正在考虑的多种三维集成方案, 也需要多种尺寸的T SV 与之配合。等离子刻蚀技术已经广泛应用于存储器和 MEM S 生产的深硅刻蚀工艺, 同样也非常适合于制造 TSV。

利用3D 堆叠技术实现微系统, 是未来发展的必然趋势, 是突破摩尔定律发展的必然选择。其中利用MEMS 技术实现 TSV 互连, 是该技术的核心技术,必须重点解决与突破。

审核编辑:刘清

全部0条评论

快来发表一下你的评论吧 !