HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

从今天开始新的一章-时序电路,包括触发器、计数器、移位寄存器、状态机等。

今天更新触发器和锁存器,这也是FPGA部分需要了解的基础部分。

《触发器全知道》

《FPGA的设计中为什么避免使用锁存器》

《SystemVerilog-程序块 (procedural blocks)》

D 触发器是一个电路,存储 1bit 数据,并定期地根据触发器的输入(d)更新这 1 bit 数据,更新通常发生在时钟上升沿(clk)。存储的数据会通过输出管脚(q)输出。

本题要求利用always程序块创建一个D触发器。

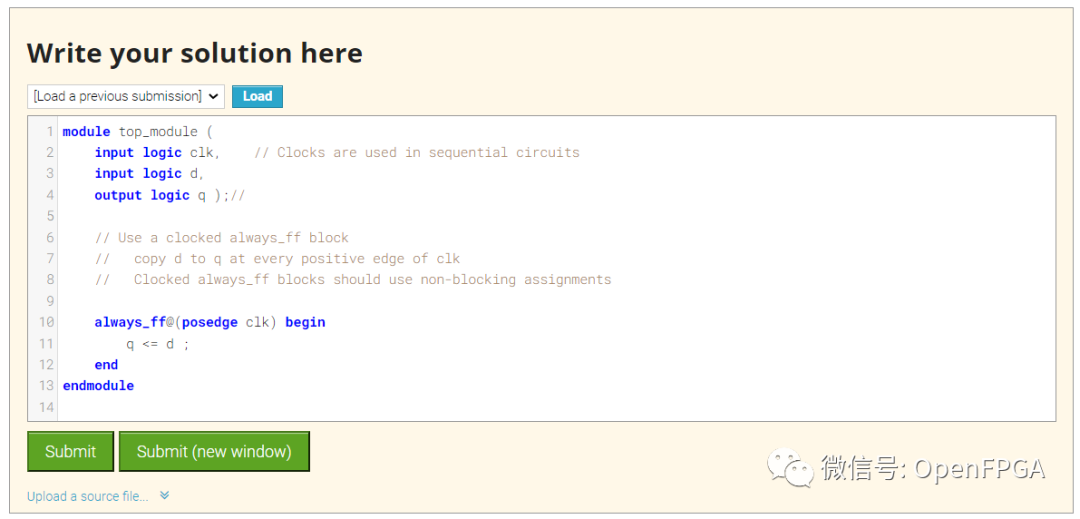

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );

module top_module (

input logic clk, // Clocks are used in sequential circuits

input logic d,

output logic q );//

// Use a clocked always_ff block

// copy d to q at every positive edge of clk

// Clocked always_ff blocks should use non-blocking assignments

always_ff@(posedge clk) begin

q <= d ;

end

endmodule

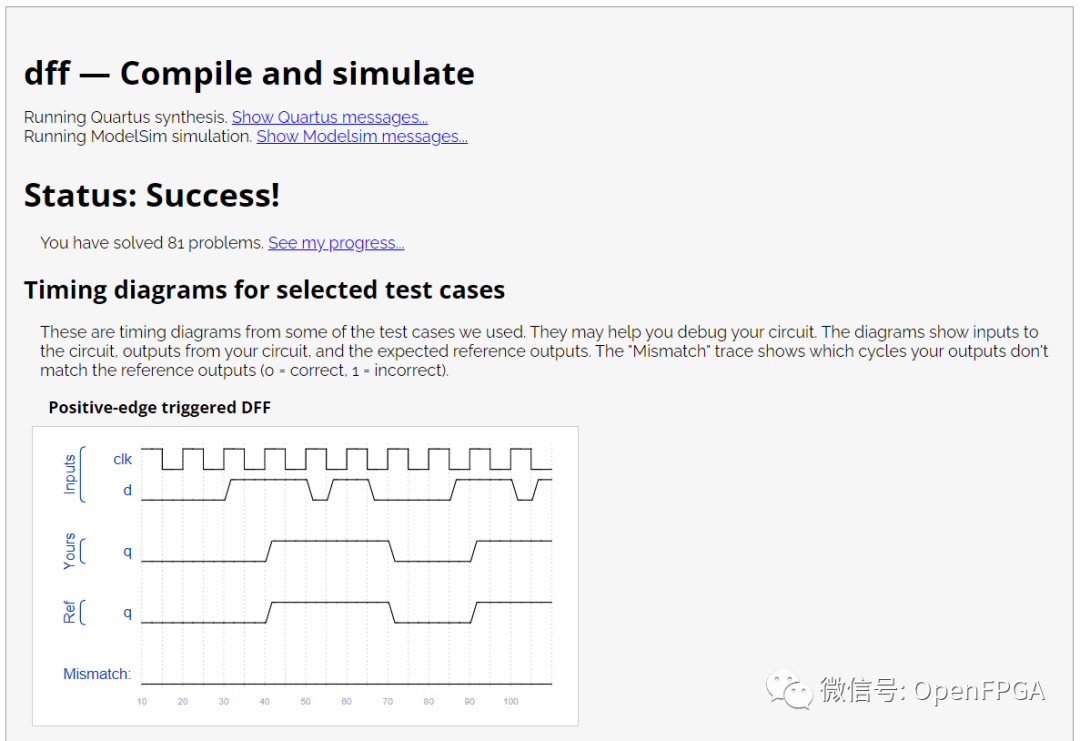

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

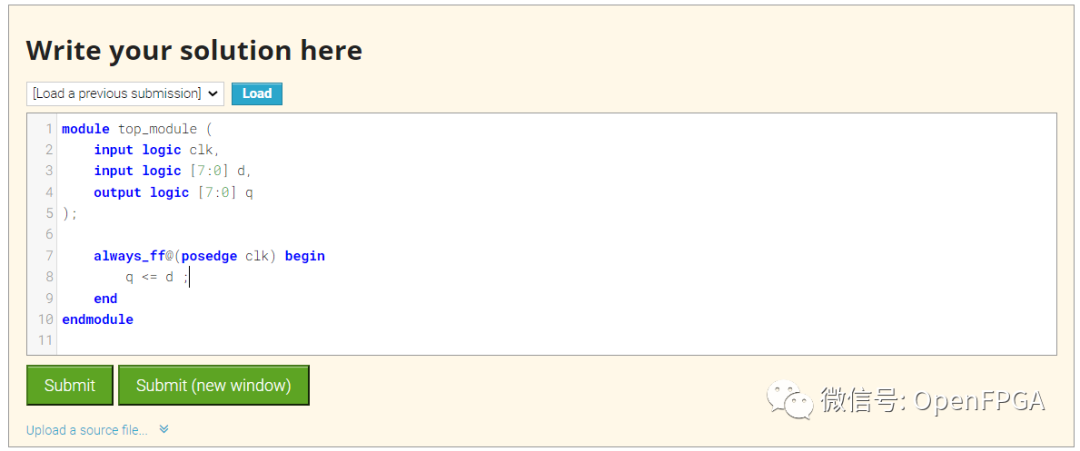

实现 8 个 D 触发器。

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

不需要将上面的电路复制八遍,只需将输入输出的位宽提高到八位即可,综合器会帮我们实现我们需要的8个触发器。

module top_module (

input logic clk,

input logic [7:0] d,

output logic [7:0] q

);

always_ff@(posedge clk) begin

q <= d ;

end

endmodule

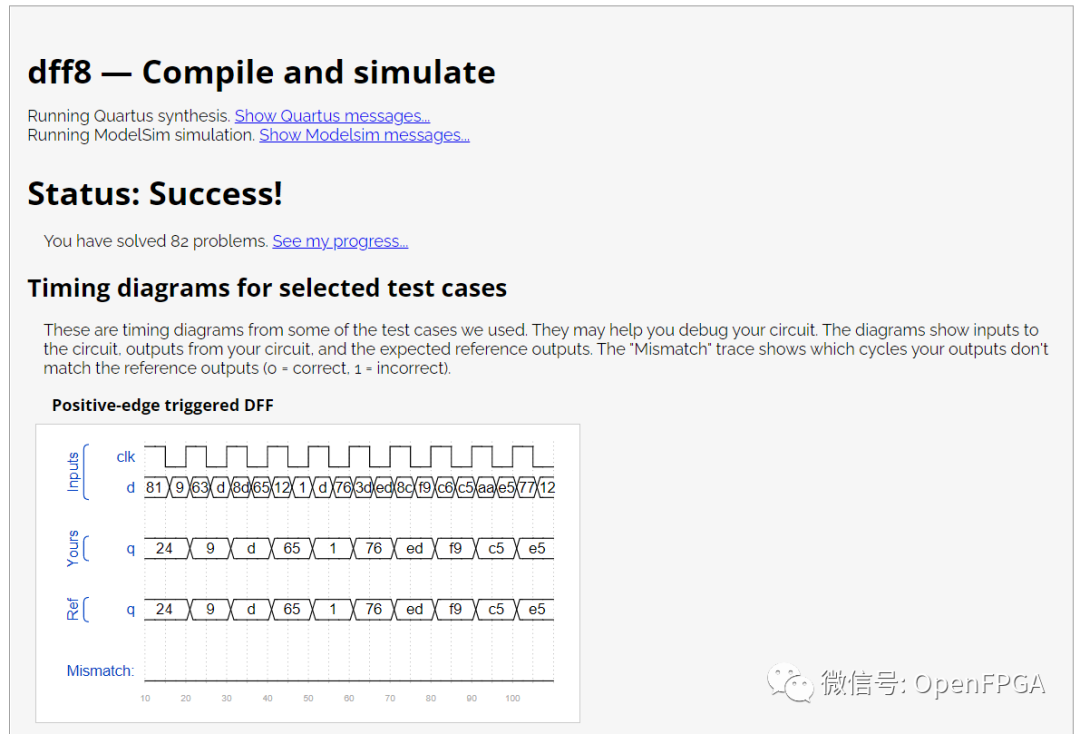

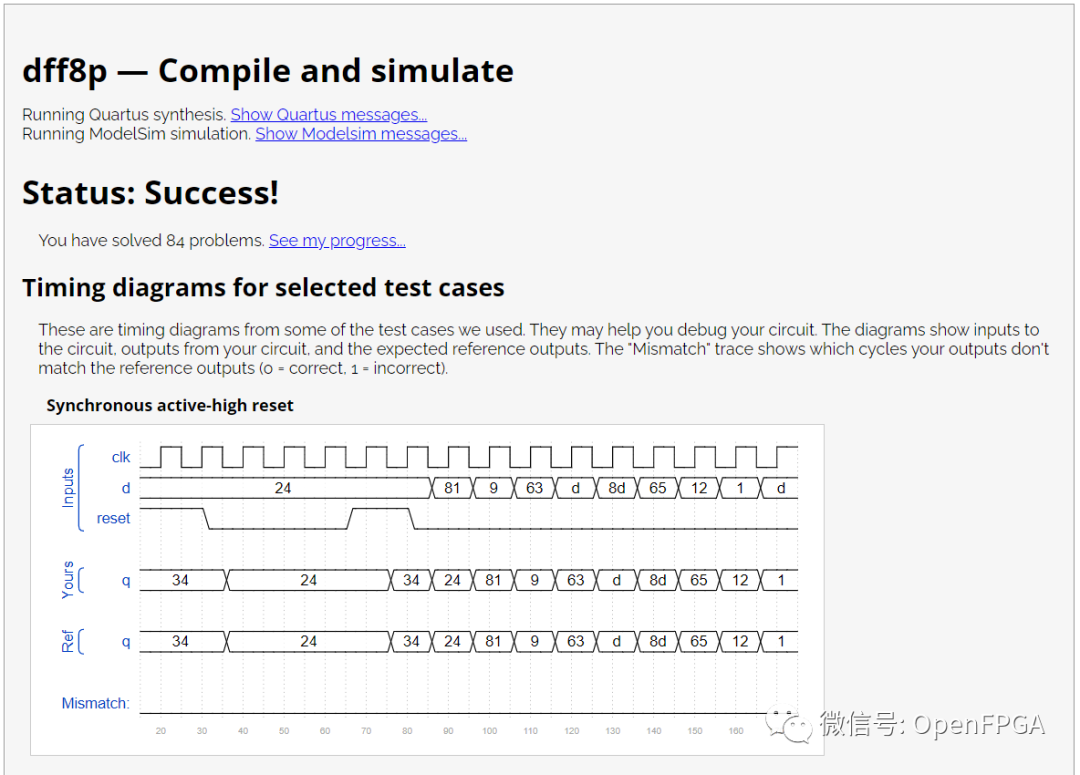

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

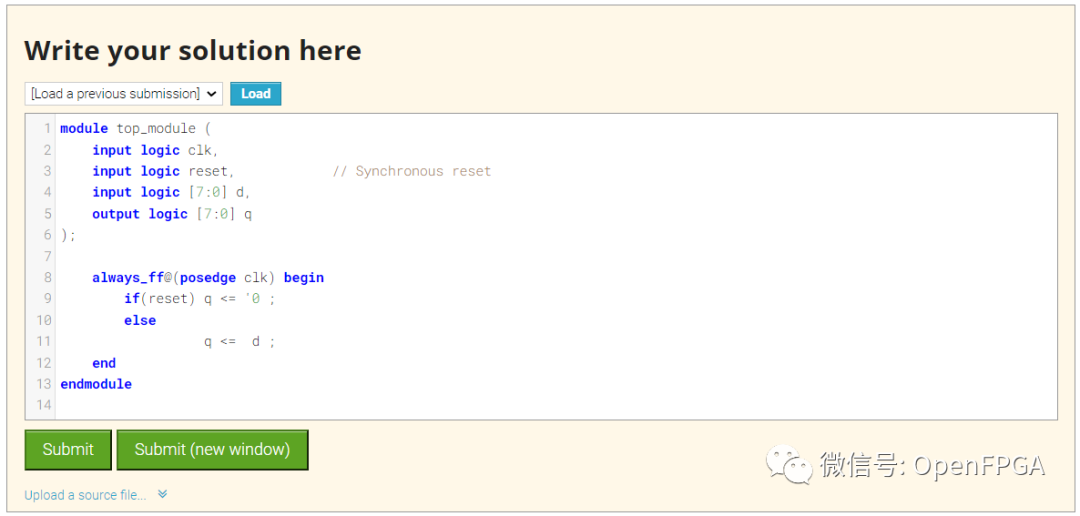

在上一题基础上加上同步复位电路。

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

这题难度不大,需要我们举一反三:明白同步复位和异步复位。

对于电路中的时序元件,把复位信号受到时钟的控制和复位信号不受时钟的控制两种电路分别称为同步复位电路和异步复位电路。

module top_module (

input logic clk,

input logic reset, // Synchronous reset

input logic [7:0] d,

output logic [7:0] q

);

always_ff@(posedge clk) begin

if(reset) q <= '0 ;

else

q <= d ;

end

endmodule

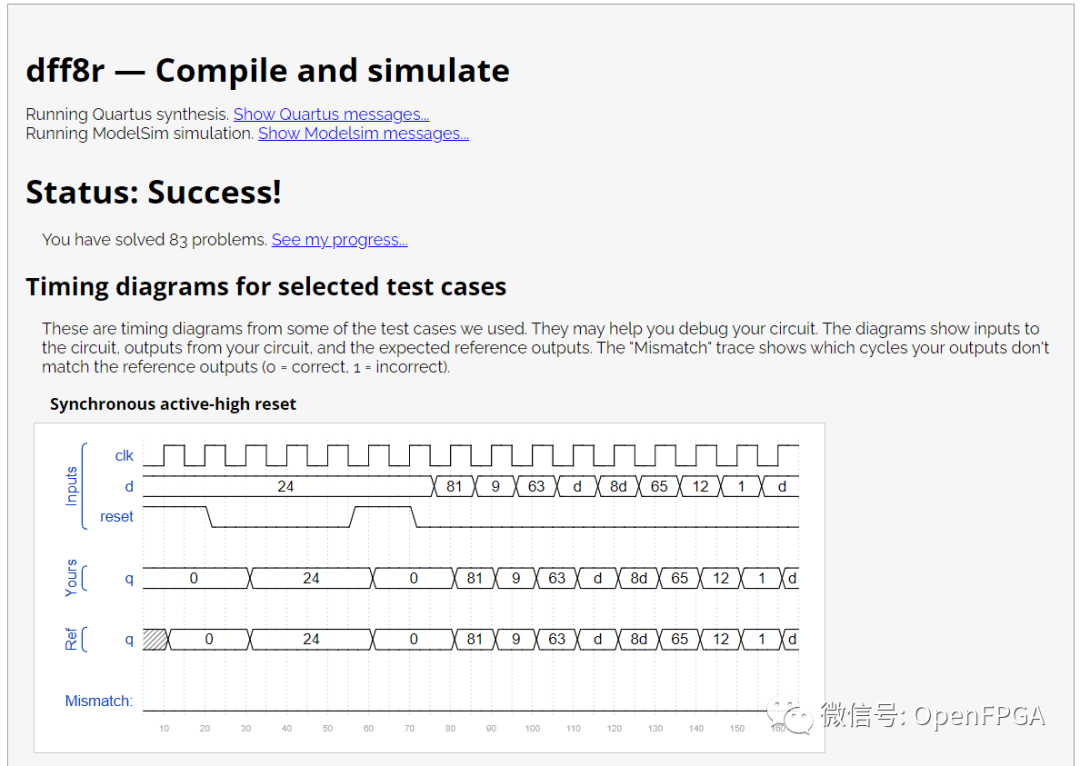

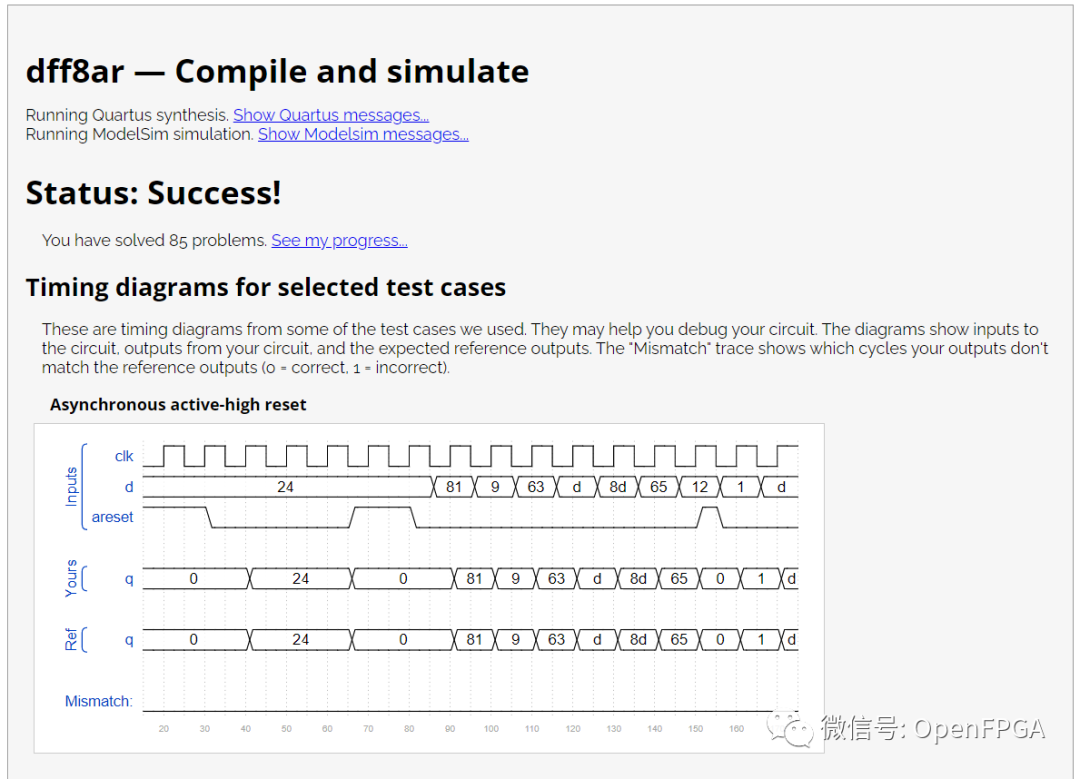

点击Submit,等待一会就能看到下图结果:

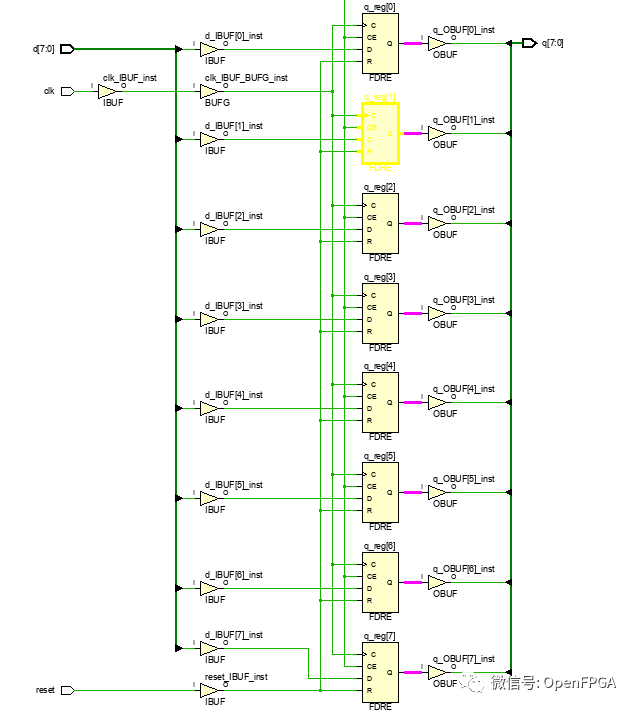

在vivado中综合的结果如下:

其中,FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 带使能功能的同步复位D触发器。

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

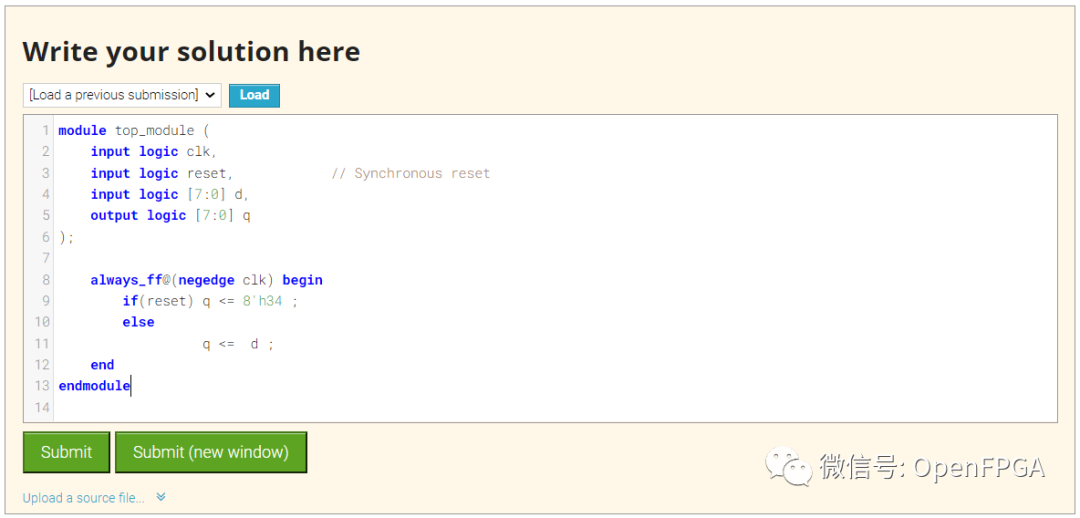

在上一题同步复位基础上,触发器必须复位时候为 0x34 而不是零。所有 DFF 都应由clk的下降沿触发。

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

module top_module (

input logic clk,

input logic reset, // Synchronous reset

input logic [7:0] d,

output logic [7:0] q

);

always_ff@(negedge clk) begin

if(reset) q <= 8'h34 ;

else

q <= d ;

end

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

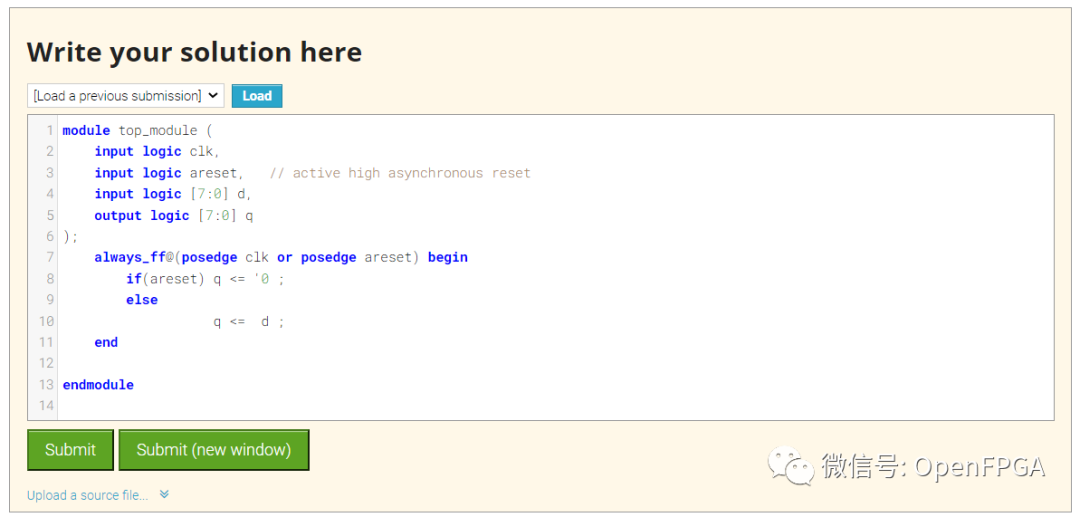

本题中的触发器引入了异步复位。当异步复位端有效时,触发器的输出复位为 0 。

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

module top_module (

input logic clk,

input logic areset, // active high asynchronous reset

input logic [7:0] d,

output logic [7:0] q

);

always_ff@(posedge clk or posedge areset) begin

if(areset) q <= '0 ;

else

q <= d ;

end

endmodule

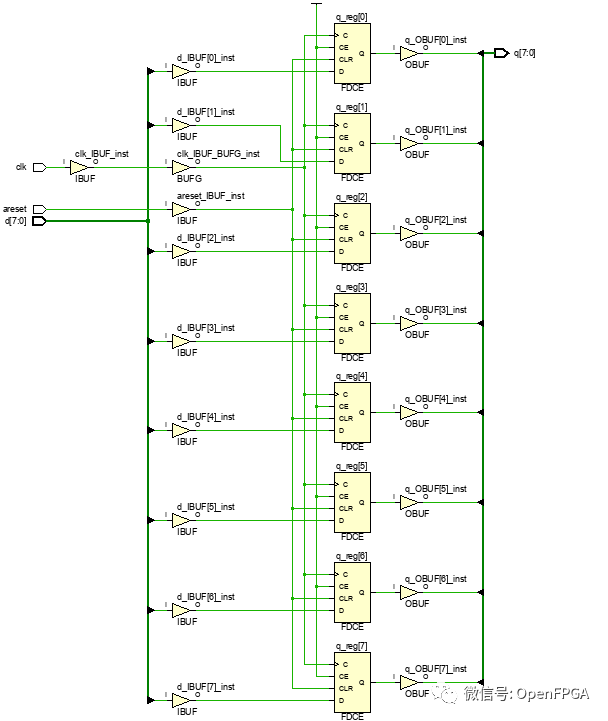

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

下图是Vivado中综合的结果:

FDC :: D Flip-Flop with Asynchronous Clear 带异步清除D触发器;FDCE:D Flip-Flop with Clock Enable and AsynchronousReset 带使能功能的异步清除D触发器,相比与FDRE将同步复位变化成异步复位,当同步复位接口为高电平时,直接触发寄存器复位(置0)。

这一题就结束了。

创建一个 16 路 D触发器。部分情况下,只需要多路触发器中的一部分触发器工作,此时可以通过 ena 使能端进行控制。使能端 ena 信号有效时,触发器在时钟上升沿工作。

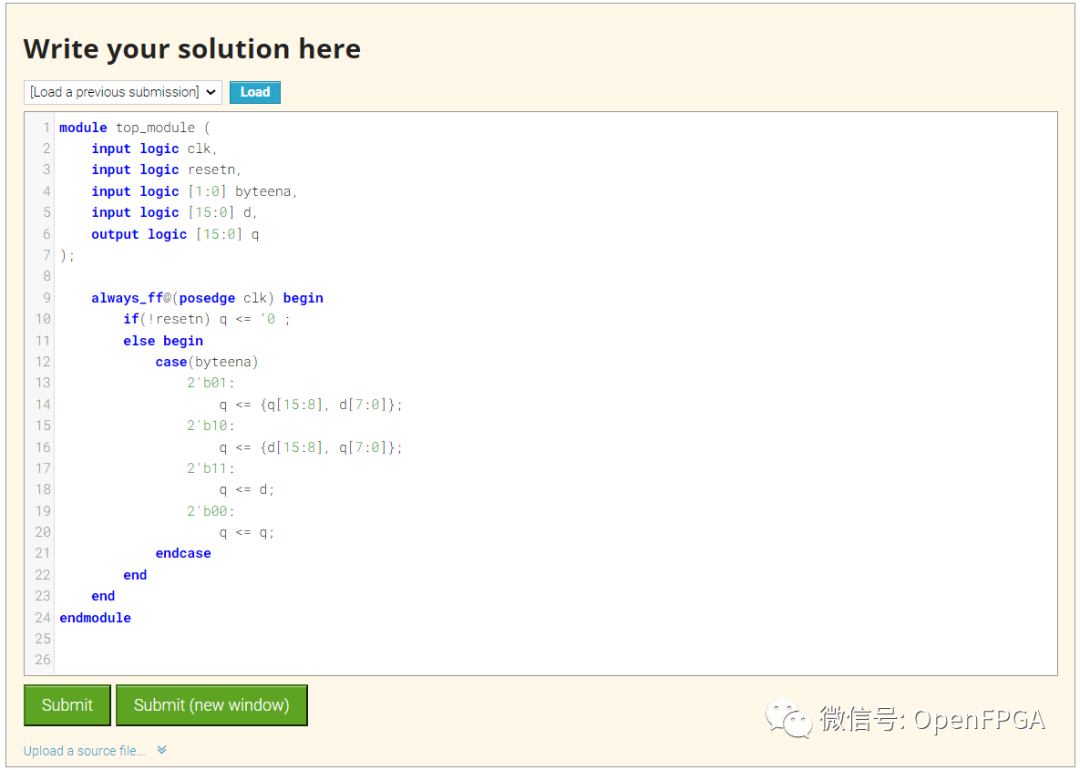

byteena 使能信号以 byte 为单位管理 8 路触发器在时钟边沿触发与否。byteena [1] 作为 d[15:8] 高位字节的使能端,byteena [0] 则控制 d 的低位字节。

resetn 为同步,低电平有效复位信号。

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output [15:0] q

);

module top_module (

input logic clk,

input logic resetn,

input logic [1:0] byteena,

input logic [15:0] d,

output logic [15:0] q

);

always_ff@(posedge clk) begin

if(!resetn) q <= '0 ;

else begin

case(byteena)

2'b01:

q <= {q[15:8], d[7:0]};

2'b10:

q <= {d[15:8], q[7:0]};

2'b11:

q <= d;

2'b00:

q <= q;

endcase

end

end

endmodule

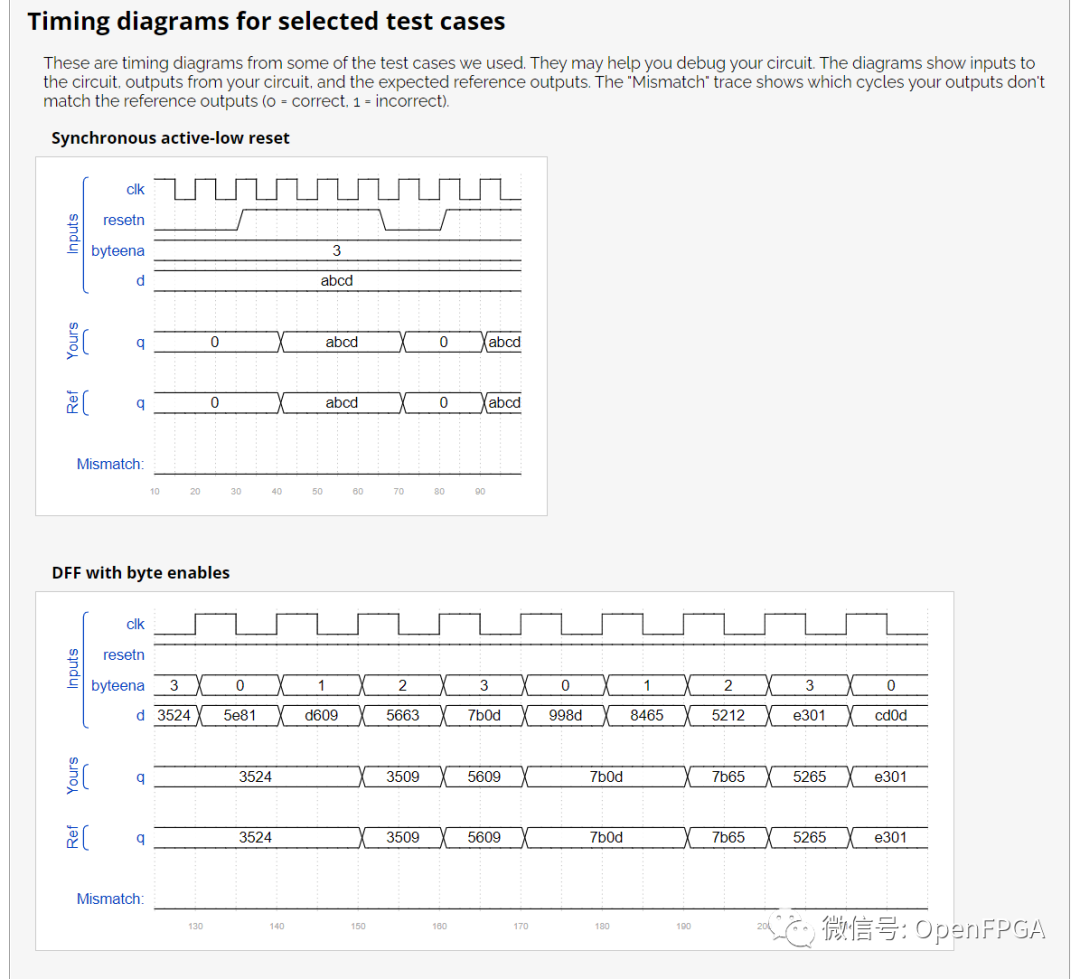

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

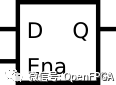

实现一个如下的电路:

从看到图片上的电路就应该认出这个基本元器件-锁存器,同D触发器对比这个元件没有 clk 端口,取而代之的是 ena 端口。

锁存器的特征在于,相较于 D触发器的触发事件发生于 clk 时钟的边沿,锁存器锁存的触发事件发生于使能端 ena 的电平。

module top_module (

input d,

input ena,

output q);

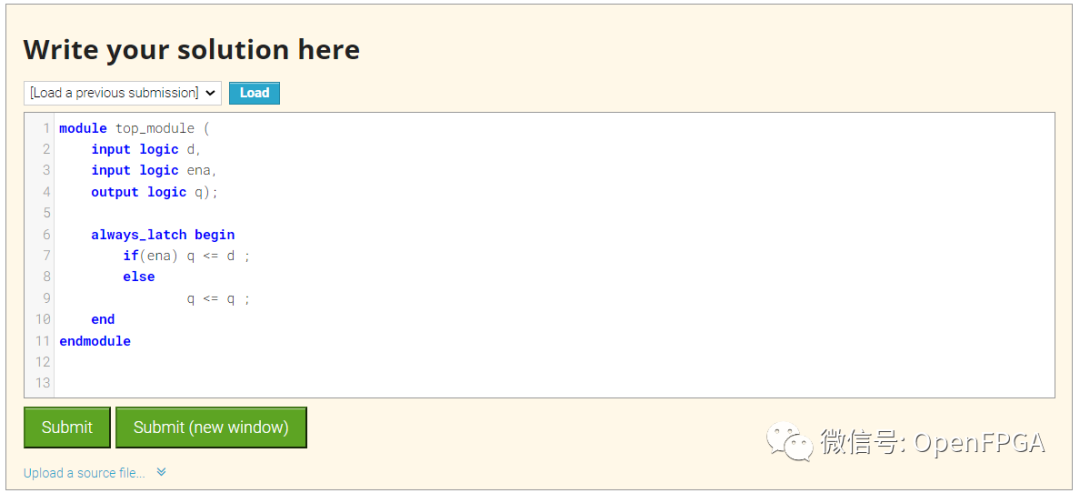

module top_module (

input logic d,

input logic ena,

output logic q);

always_latch begin

if(ena) q <= d ;

else

q <= q ;

end

endmodule

从上面的代码可以看出,SV在硬件描述过程中比Verilog代码可读性高很多,一眼就能看出这个电路的功能,而Verilog需要根据描述的功能推测电路功能。

点击Submit,等待一会就能看到下图结果:

注意图中无波形。但是注意图中的警告,这个在实际使用中非常重要,锁存器相比触发器会消耗更多的资源,所以综合器会在推断出锁存器时产生提醒,防止开发者在不想使用锁存器时,因为代码风格等原因误产生了锁存器。

这一题就结束了。

实现一个如下的电路:

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

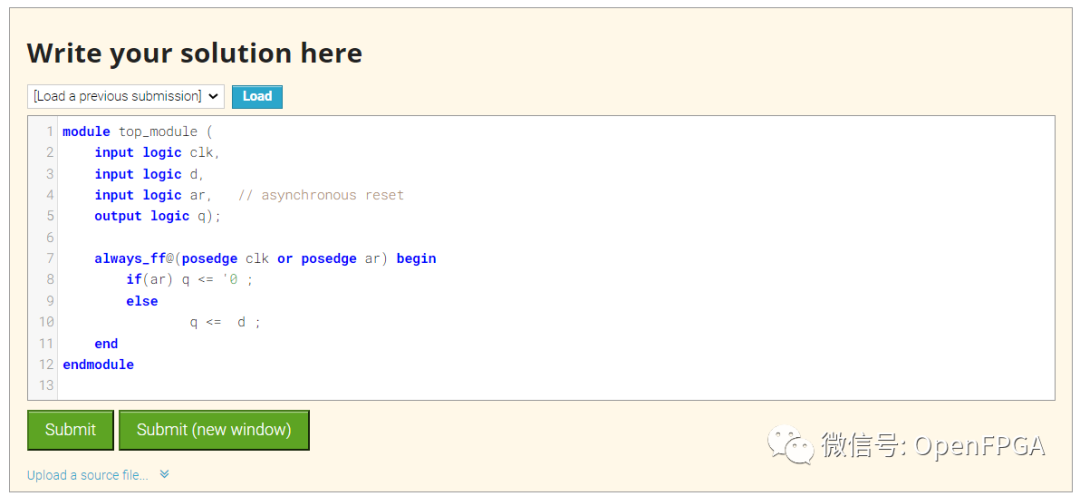

AR 代表 asynchronous reset,所以这是一个带有异步复位的 D 触发器。

图中的三角形代表时钟,不再用 CLK 标出。

module top_module (

input logic clk,

input logic d,

input logic ar, // asynchronous reset

output logic q);

always_ff@(posedge clk or posedge ar) begin

if(ar) q <= '0 ;

else

q <= d ;

end

endmodule

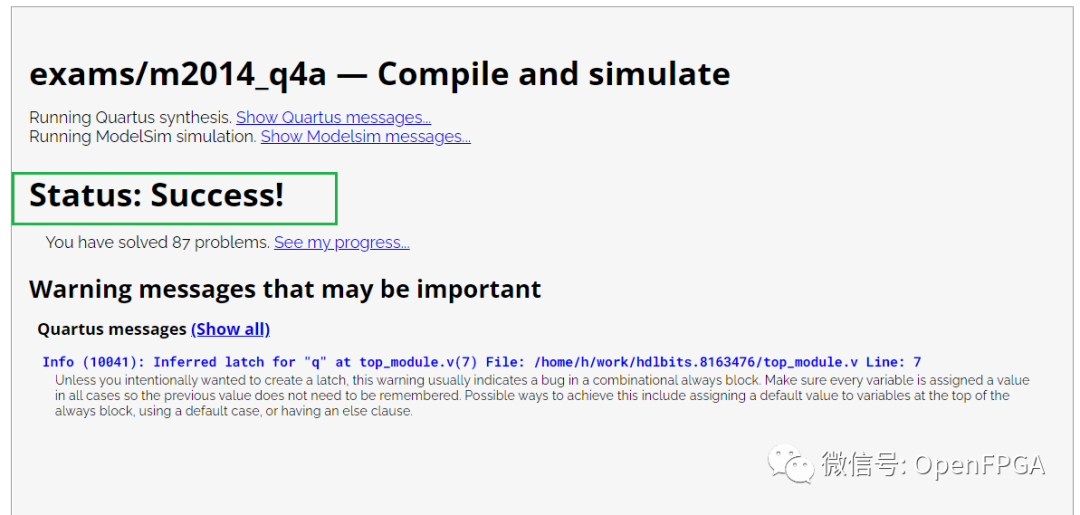

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

实现一个如下的电路:

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

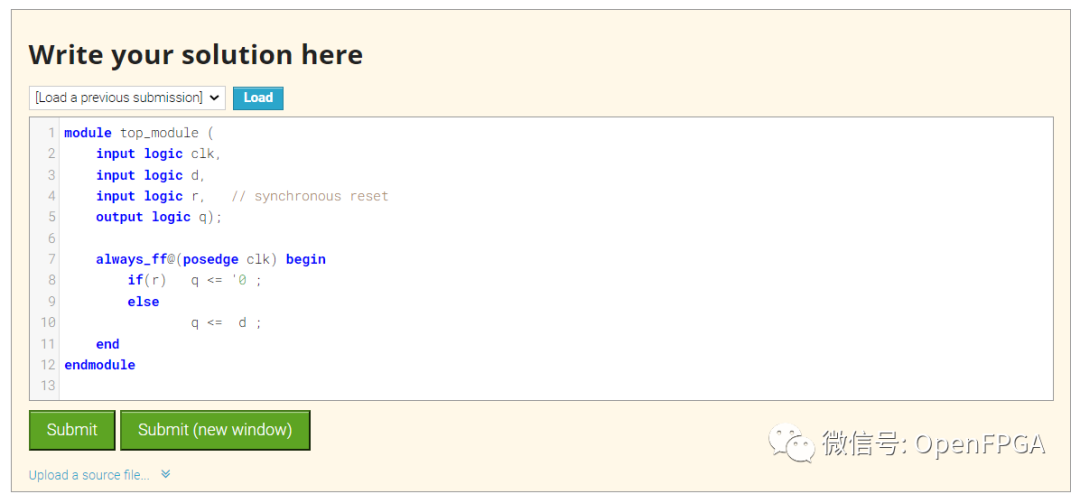

R 代表 synchronous reset。所以这是一个同步复位的D触发器。

module top_module (

input logic clk,

input logic d,

input logic r, // synchronous reset

output logic q);

always_ff@(posedge clk) begin

if(r) q <= '0 ;

else

q <= d ;

end

endmodule

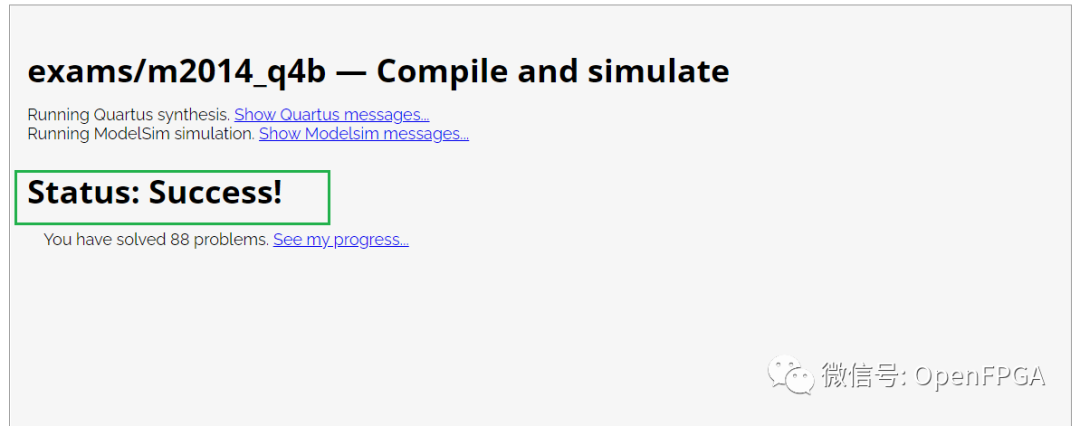

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

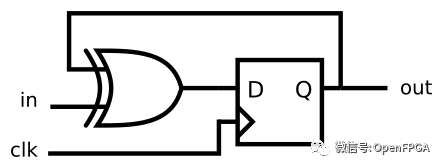

实现一个如下的电路:

module top_module (

input clk,

input in,

output out);

触发器的输出 q 和输入信号 in 一起作为异或门的输入。

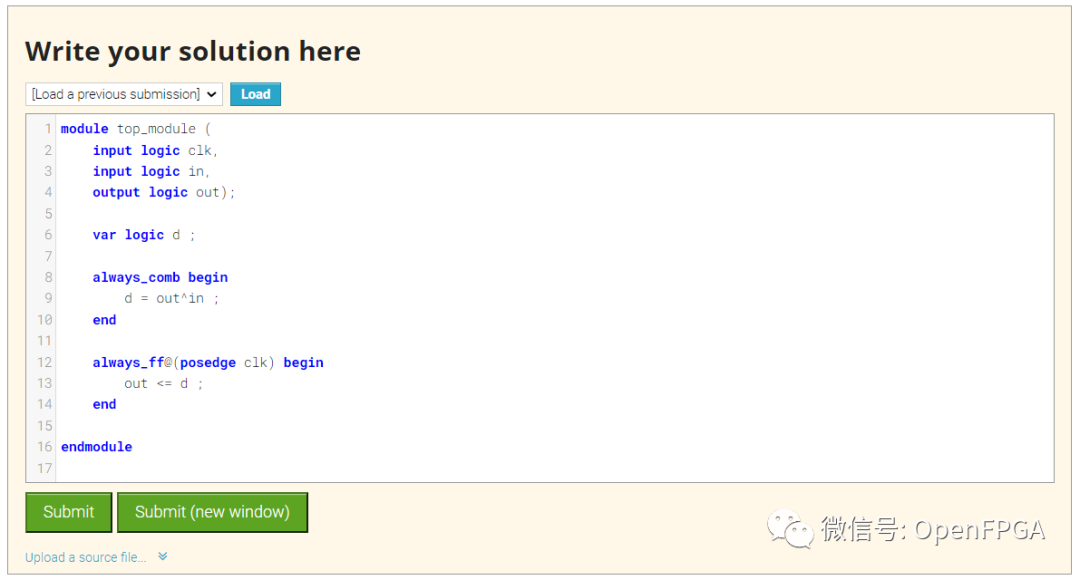

module top_module (

input logic clk,

input logic in,

output logic out);

var logic d ;

always_comb begin

d = out^in ;

end

always_ff@(posedge clk) begin

out <= d ;

end

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

今天的几道题就结束了,对于理解触发器的非常有帮助,尤其同步复位、异步复位及锁存器的理解非常有帮助,对于这些简单的代码,建议放到实际的EDA工具中跑下综合,查看一下FPGA具体的实现元器件是什么样,这样在后期自己设计代码时候的理解很有帮助。

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

审核编辑 :李倩

全部0条评论

快来发表一下你的评论吧 !