为了让音响工程师能够在现场活动(例如音乐会)期间提供高质量的声音,从所有乐器录制的声音都会通过混音器,通过混音器可以修改每个乐器(通道)的不同声音参数。大多数场地都有模拟混音器(它们比数字版本便宜),需要音响工程师站在它附近才能纠正所有不同的细节,因此,他无法准确听到观众听到的声音(因为通常音响设备是放在旁边某处)。

该项目旨在通过为模拟混音器设计一个可用于控制某些信号参数的附加模块,为音响工程师甚至乐队成员提供机动性。

该项目将帮助现场场地的音响工程师在远离物理调音台的情况下设置信号参数。这种增加的机动性将帮助他从观众的角度听到声音并进行相应的调整。

该设计基于 Arty s7 fpga 开发板以及将开发板连接到音频混音器和移动设备所需的不同外围设备。

该设计采用模块化结构,因此它的某些部分可用于其他信号处理应用。

我们的项目旨在创建功能齐全的畅销产品。虽然这种状态还很遥远,但它仍然是一个合理的目标。它还可以用于信号处理和 HDL 设计课程中的学术目的。

虽然最初针对 ArtyS7 板,但该设计可以移植到其他基于 FPGA 的开发板,只要它们具有所需数量的引脚。

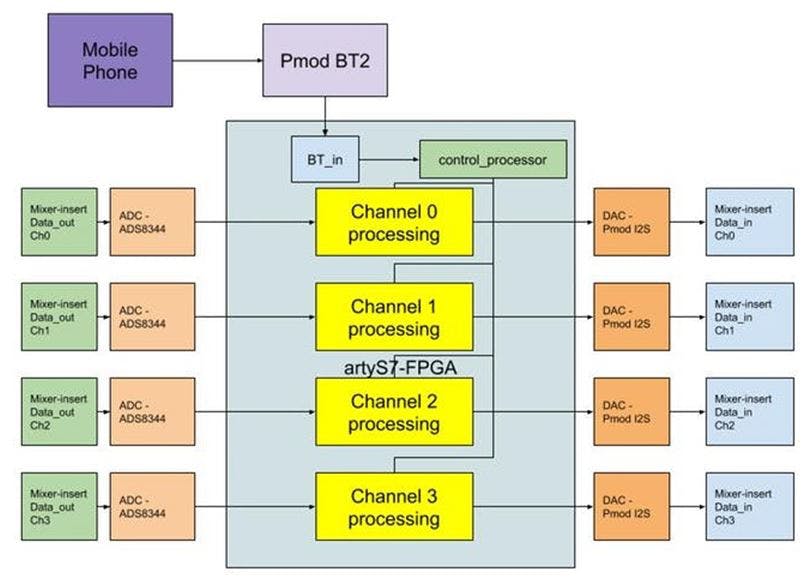

我们的设计基于artyS7 FPGA板,如下图:

手机(通过蓝牙)用于发送命令和控制整个系统和每个通道的系统。每个通道彼此独立地处理来自混音器的音频数据。音频数据来自模数转换器,经过所有所需的处理后,通过数模转换器返回模拟混音器。

所有模块均采用 Verilog 硬件描述语言设计。

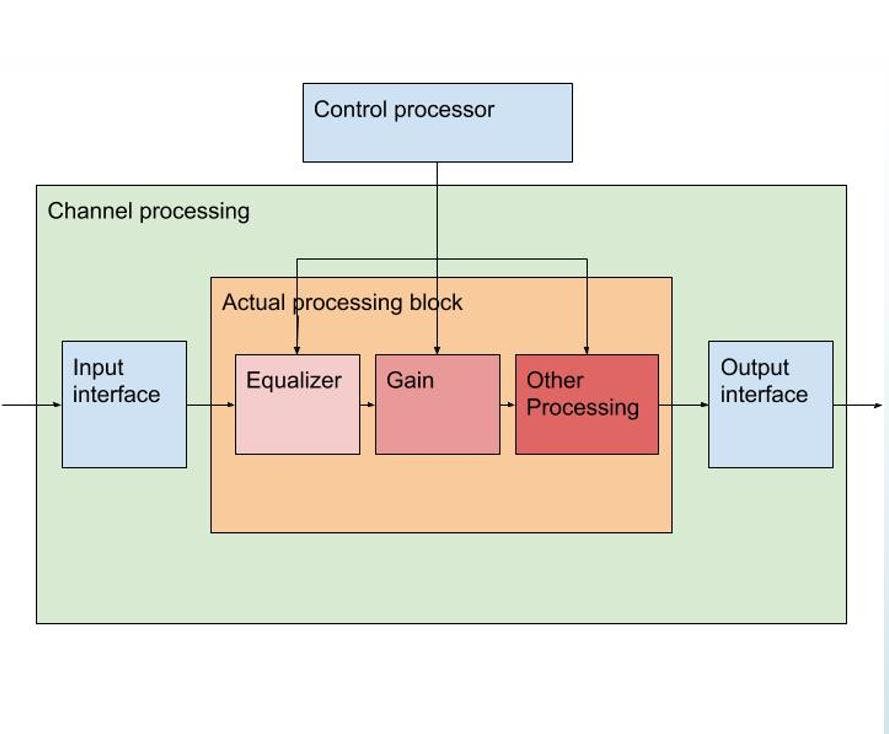

每个处理模块由一个输入级(与 ADC 接口)、一个输出级(与 DAC 接口)和实际处理级组成。处理阶段本身由多种音频效果或所需功能组成。这种架构允许轻松添加额外的处理层,因此具有高度可扩展性。

控制处理器(或 bt 接收器)通过简单的地址/数据/we 接口向每个子模块提供所有需要的信息(如果子模块处于活动状态,则为内部寄存器值)。

每个通道处理如下图:

每个处理块都有一个相关的地址范围,用于选择用于控制子模块操作的内部寄存器。在设计完所有模块后,将集中完整的地址映射(对于当前实现的地址,请参见 DEFINE.vh 文件)。

接口被设计为有限状态机。为了控制音频信号的采样率(我们选择了标准的 48kHz),必须创建一个额外的“立即采样”命令生成器。

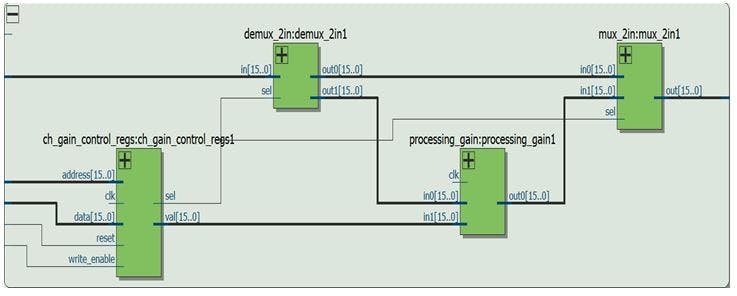

所有处理模块都有顺序电路和组合电路,所有这些都可以通过蓝牙接口配置内部寄存器来绕过或激活。处理块的结构如下所示(图取自增益处理块):

使用控制寄存器可以启用或禁用整个模块,并且可以为所有需要的计算参数设置不同的值。绕过块是通过使用 demux/mux 对来实现的。

增益模块是通过乘法和位移来实现的,因为浮点运算在 FPGA 上非常难以实现。

配置命令可以通过蓝牙发送。命令具有以下结构:addr_MSByte + addr_LSByte + data_MSByte + data LSByte。

主系统时钟为 100MHz,所有其他必要的时钟都来自它。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !