电子说

作为电子工程师,相信大家都对MOSFET不会陌生。工程师们要选用某个型号的 MOSFET,首先要看的就是规格书-datasheet,拿到 MOSFET的规格-datasheet 时,我们要怎么去理解那十几页到几十页的内容呢?我们就以英飞凌 IPP60R190C6 datasheet为例详细探讨一下。

1、VDS

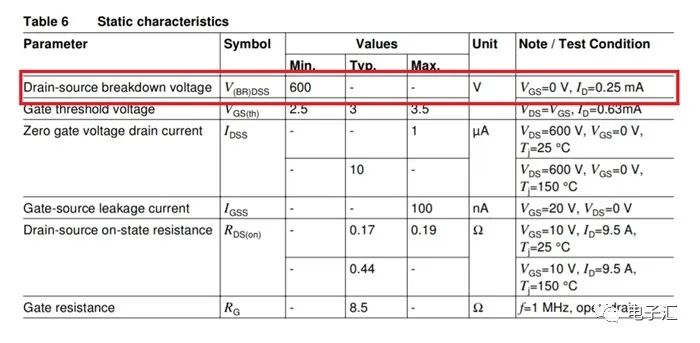

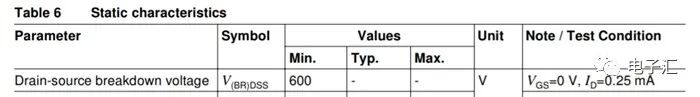

Datasheet 上电气参数第一个就是 V(BR)DSS,即 DS 击穿电压,也就是我们关心的 MOSFET 的耐压

图中V(BR)DSS的最小值是600V,是不是表示设计中只要MOSFET上电压不超过600V MOSFET就能工作在安全状态?

相信很多人的答案是“是!”,曾经我也是这么认为的,但这个正确答案是“不是!”

这个参数是有条件的,这个最小值600V是在Tj=25℃的值,也就是只有在Tj=25℃时,MOSFET上电压不超过600V才算是工作在安全状态。

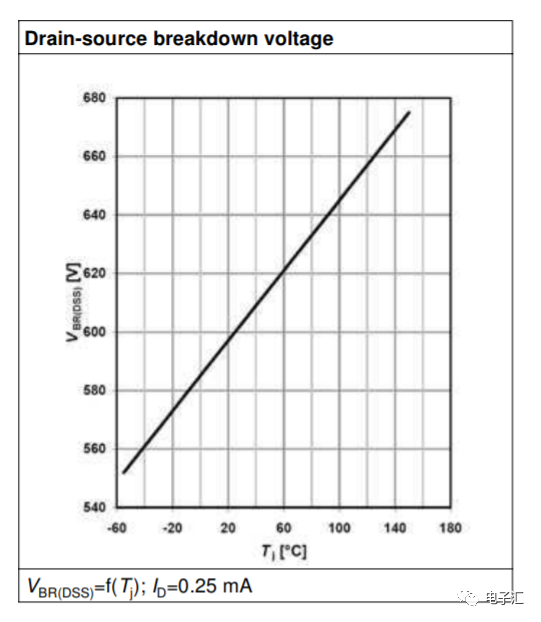

从下图datasheet上V(BR)DSS与Tj的关系中可以清楚地看出,MOSFET V(BR)DSS与温度是正相关的。要是电源用在寒冷的地方,环境温度低到-40℃甚至更低的话,MOSFET V(BR)DSS值<560V,这时候600V就已经超过MOSFET耐压了。

所以在MOSFET使用中,我们都会保留一定的VDS的电压裕量,其中一点就是为了考虑到低温时MOSFET V(BR)DSS值变小了,另外一点是为了应对各种恶例条件下开关机的VDS电压尖峰。

2、ID

相信大家都知道 MOSFET 最初都是按 xA, xV 的命名方式(比如 20N60~),慢慢的都转变成Rds(on)和电压的命名方式(比如 IPx60R190C6, 190 就是指 Rds(on)~).

其实从电流到 Rds(on)这种命名方式的转变就表明 ID 和 Rds(on)是有着直接联系的,那么它们之间有什么关系呢?

在说明 ID 和 Rds(on)的关系之前,先得跟大家聊聊封装和结温:

1). 封装:影响我们选择 MOSFET 的条件有哪些?

a) 功耗跟散热性能 -->比如:体积大的封装相比体积小的封装能够承受更大的损耗;铁封比塑封的散热性能更好.

b) 对于高压 MOSFET 还得考虑爬电距离 -->高压的 MOSFET 就没有 SO-8 封装的,因为G/D/S 间的爬电距离不够

c) 对于低压 MOSFET 还得考虑寄生参数 -->引脚会带来额外的寄生电感、电阻,寄生电感往往会影响到驱动信号,寄生电阻会影响到 Rds(on)的值

d) 空间/体积 -->对于一些对体积要求严格的电源,贴片 MOSFET 就显得有优势了

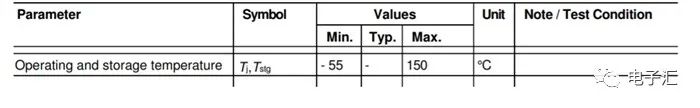

2). 结温:MOSFET 的最高结温 Tj_max=150℃,超过此温度会损坏 MOSFET,实际使用中建议不要超过 70%~90% Tj_max.

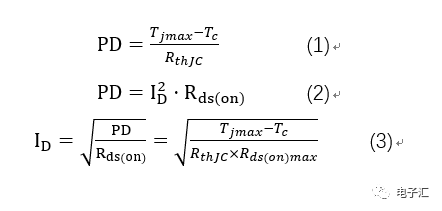

回到正题,MOSFET ID和Rds(on)的关系:

(1) 封装能够承受的损耗和封装的散热性能(热阻)之间的关系

(2) MOSFET通过电流ID产生的损耗

(1), (2)联立,计算得到ID和Rds_on的关系

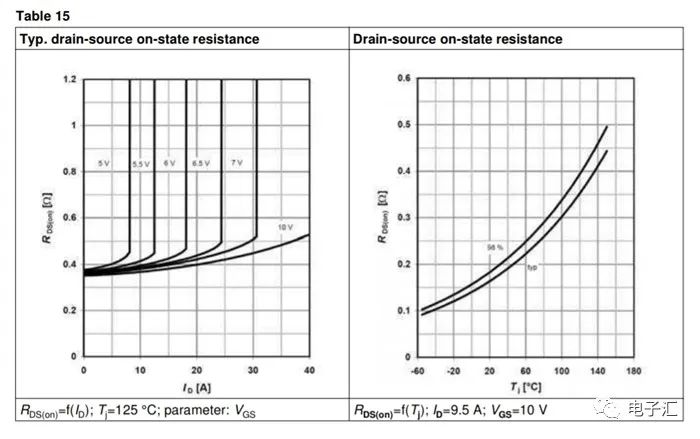

3、Rds(on)

从下面MOSFET Rds(on)与Tj的图表中可以看到:Tj增加Rds(on)增大,Tj与Rds(on)是正相关,MOSFET的这一特性使得MOSFET易于并联使用。

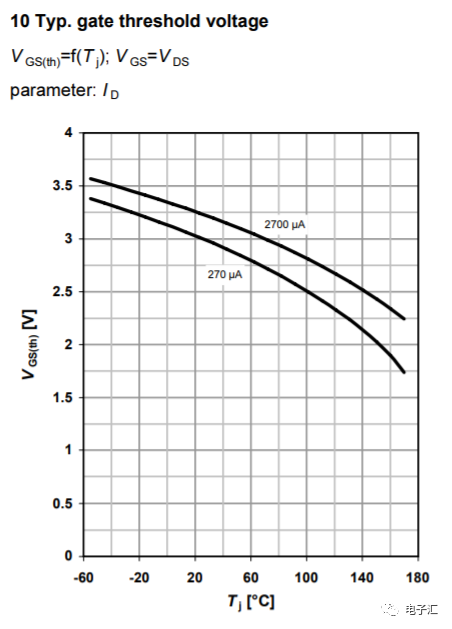

4、Vgs(th)

相信这个值大家都熟悉,但是Vgs(th)是负温度系数有多少人知道,你知道吗?(下图是IPP075N15N3 datasheet中Vgs与稳定的关系)。相信会有很多人没有注意到Vgs(th)的这一特性,这也是正常的,因为高压MOSFET的datasheet中压根就没有这个图,这一点可能是因为高压MOSFET的Vgs(th)值一般都是2.5V以上,高温时也就到2V左右。但对于低压MOSFET就有点不一样了,很多低压MOSFET的Vgs(th)在常温时就很低,比如BSC010NE2LS的Vgs(th)是1.2V~2V,高温时最低都要接近0.8V了,这样只要在Gate有一个很小的尖峰就可能误触发MOSFET开启从而引起整个电源系统异常。

所以,低压MOSFET使用时一定要留意Vgs(th)的这个负温度系数的特性!

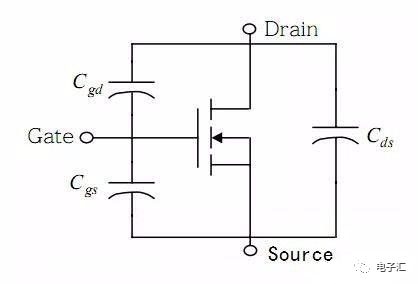

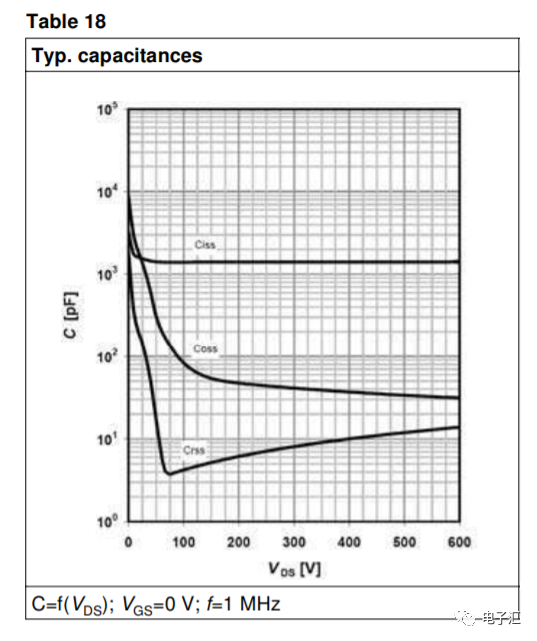

5、Ciss, Coss, Crss

MOSFET 带寄生电容的等效模型

Ciss=Cgd+Cgs, Coss=Cgd+Cds, Crss=Cgd

Ciss, Coss, Crss 的容值都是随着 VDS 电压改变而改变的。

在 LLC 拓扑中,减小死区时间可以提高效率,但过小的死区时间会导致无法实现 ZVS。因此选择在VDS 在低压时 Coss 较小的 MOSFET 可以让 LLC 更加容易实现 ZVS,死区时间也可以适当减小,从而提升效率。

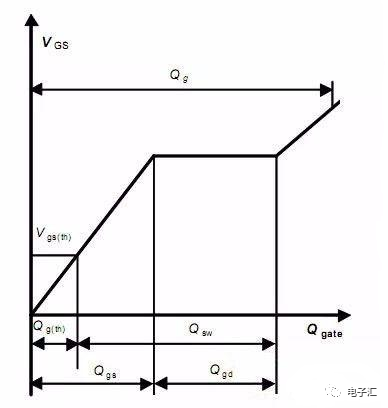

6、 Qg, Qgs, Qgd

从下图中能够看出:

1. Qg并不等于Qgs+Qgd!!

2. Vgs高,Qg大,而Qg大,驱动损耗大

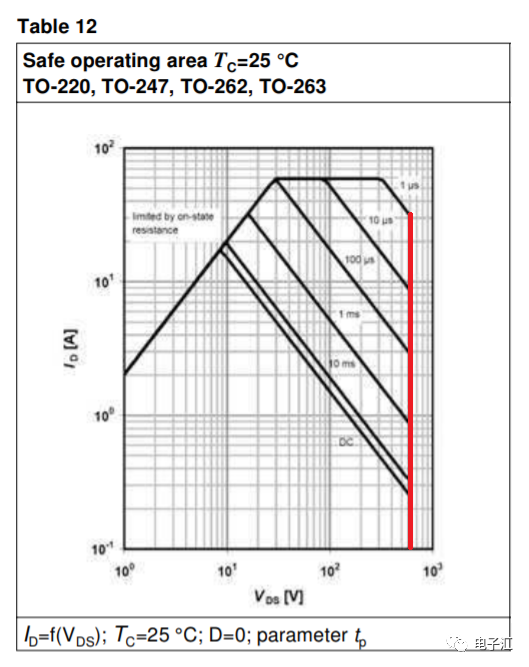

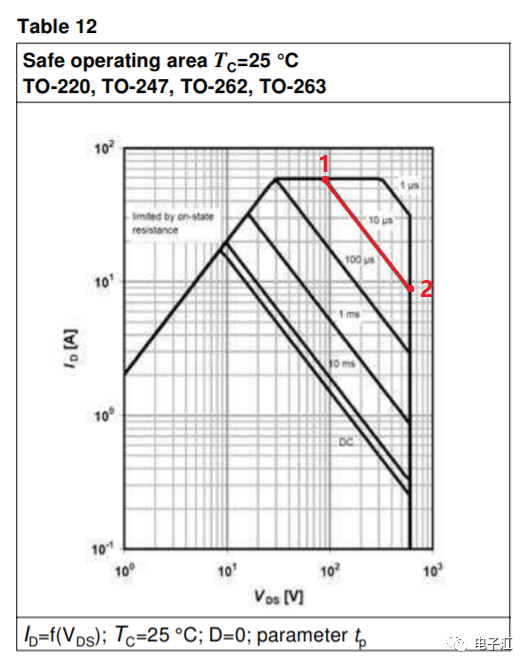

7、SOA

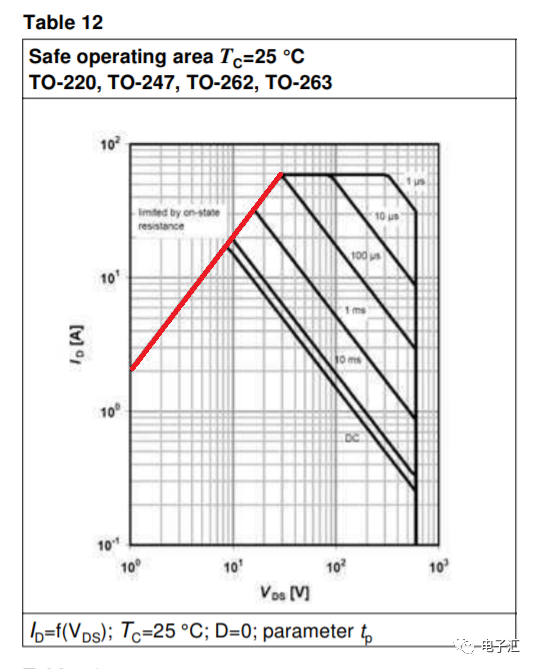

SOA曲线可以分为4个部分:

1). Rds_on的限制,如下图红色线部分

当VDS=1V时,Y轴对应的ID为2A,Rds=VDS/ID=0.5R ==>Tj=150℃时,Rds(on)约为0.5R.当VDS=10V时,Y轴对应的ID为20A,Rds=VDS/ID=0.5R ==>Tj=150℃时,Rds(on)约为0.5R.所以,此部分曲线中,SOA表现为Tj_max时RDS(on)的限制.

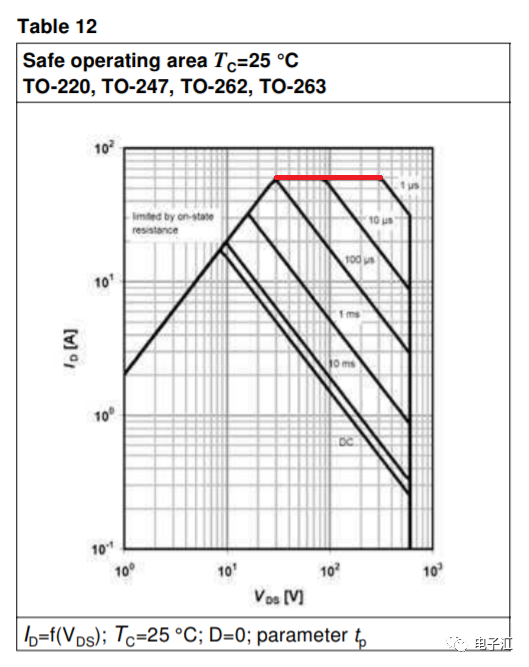

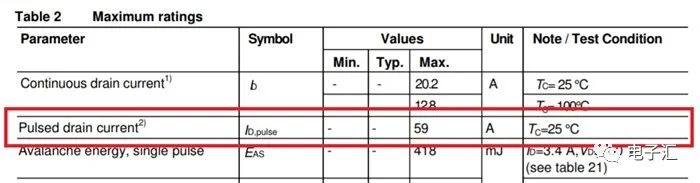

2).最大脉冲电流限制,如下图红线部分

此部分为MOSFET的最大脉冲电流限制,此最大电流对应ID_pulse.

3). VBR(DSS)击穿电压限制,如下图红线部分

此部分为MOSFET VBR(DSS)的限制,最大电压不能超过VBR(DSS) ==>所以在雪崩时,SOA图是没有参考意义的。

4). 器件所能够承受的最大的损耗限制

这里以图中红线的那条线(10us)来分析。

上图中,1处电压、电流分别为:88V, 59A,2处电压、电流分别为:600V, 8.5A。

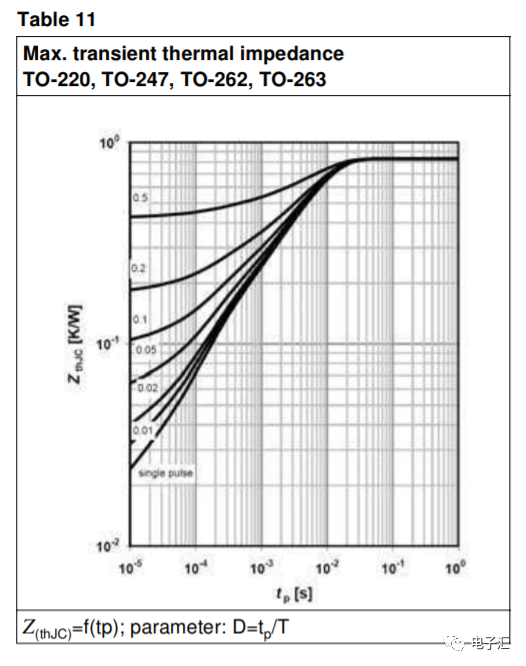

MOSFET要工作在SOA,即要让MOSFET的结温不超过Tj_max(150℃),Tj_max=Tc+PD*ZthJC, ZthJC为瞬态热阻。

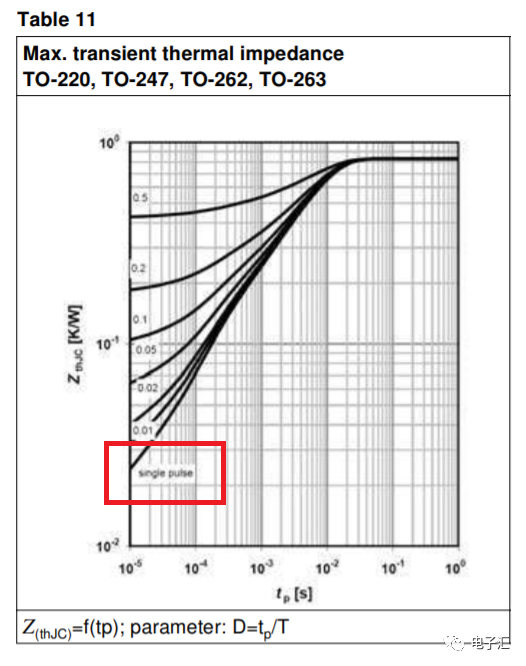

SOA图中,D=0,即为single pulse,红线附近的那条线上时间是10us即10^-5s,从瞬态热阻曲线上可以得到ZthJC=2.4*10^-2

从以上得到的参数可以计算出:

1处的Tj约为:25+88*59*2.4*10^-2=149.6℃

2处的Tj约为:25+600*8.5*2.4*10^-2=147.4℃

MOSFET datasheet上往往只有Tc=25和80℃时的SOA,但实际应用中不会刚好就是在Tc=25或者80℃,这时候就得想办法把25℃或者80℃时的SOA转换成实际Tc时的曲线。

把25℃时的SOA转换成100℃时的曲线:

1). 在25℃的SOA上任意取一点,读出VDS, ID,时间等信息

如上图,1处电压、电流分别为:88V, 59A, tp=10us

计算出对应的功耗:PD=VDS*ID=88*59=5192 (a)

PD=(Tj_max-Tc)/ZthJC -->此图对应为Tc=25℃ (b)

(a),(b)联立,可以求得ZthJC=(Tj_max-25)/PD=0.024

2). 对于同样的tp的SOA线上,瞬态热阻ZthJC保持不变,Tc=100℃,ZthJC=0.024.

3). 上面图中点1处的电压为88V,Tc=100℃时,PD=(Tj_max-100)/ZthJC=2083

从而可以算出此时最大电流为I=PD/VDS=2083/88=23.67A

4). 同样的方法可以算出电压为600V,Tc=100℃时的最大电流

5). 把电压电流的坐标在图上标出来,可以得到10us的SOA线,同样的方法可以得到其他tp对应的SOA(当然这里得到的SOA还需要结合Tc=100℃时的其他限制条件)

这里的重点就是ZthJC,瞬态热阻在同样tp和D的条件下是一样的,再结合功耗,得到不同电压条件下的电流

另外一个问题,ZthJC/瞬态热阻计算:

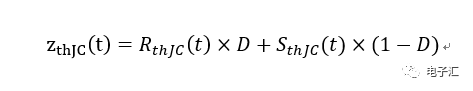

当占空比D不在ZthJC曲线中时:(其中,SthJC(t)是single pulse对应的瞬态热阻)

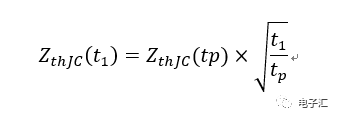

2.当tp<10us时

8、Avalanche

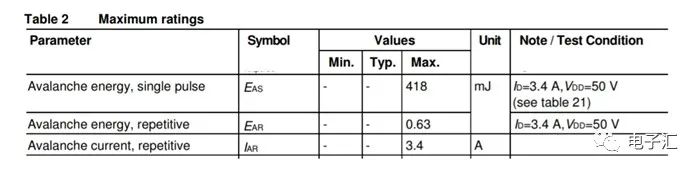

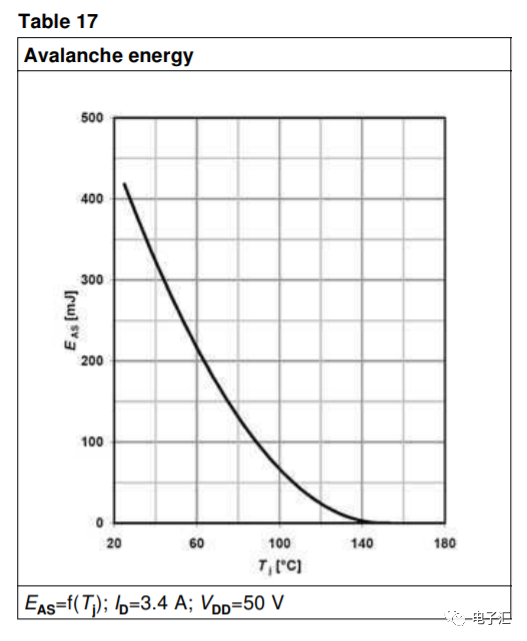

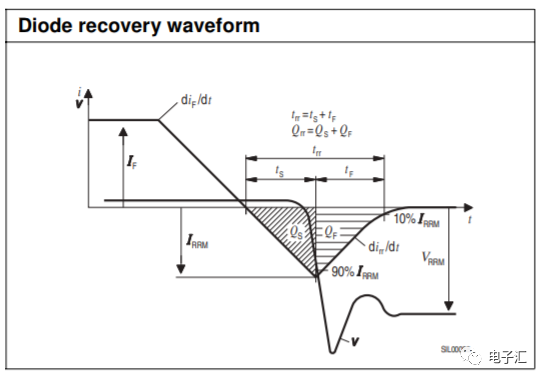

下图中,EAS:单次雪崩能量,EAR:重复雪崩能量,IAR:重复雪崩电流

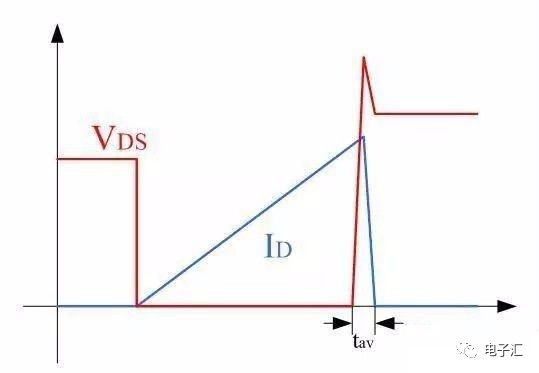

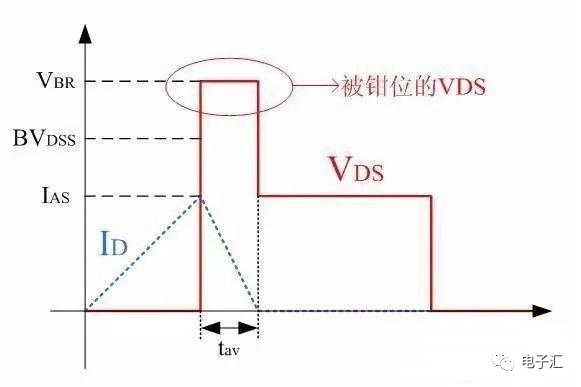

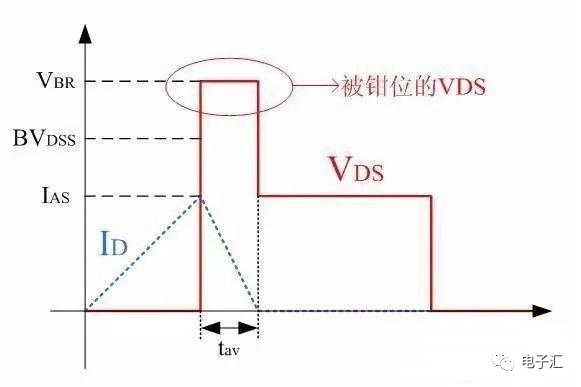

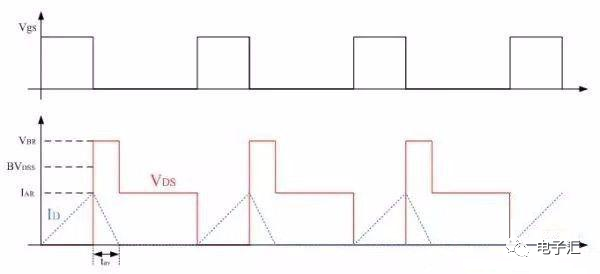

雪崩时VDS,ID典型波形与展开后的图像如下,可以发现MOSFET雪崩时,波形上一个显著的特点是VDS电压被钳位,即图中VDS有一个明显的平台

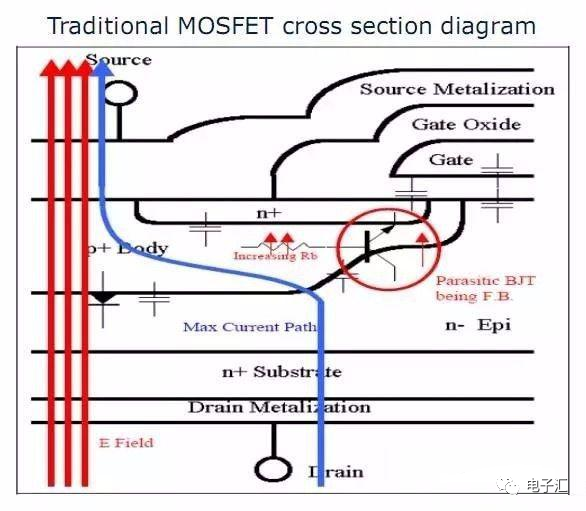

MOSFET雪崩的产生:

在MOSFET的结构中,实际上是存在一个寄生三极管的,如上图。在MOSFET的设计中也会采取各种措施去让寄生三极管不起作用,如减小P+Body中的横向电阻RB。正常情况下,流过RB的电流很小,寄生三极管的VBE约等于0,三极管是处在关闭状态。雪崩发生时,如果流过RB的雪崩电流达到一定的大小,VBE大于三极管VBE的开启电压,寄生三极管开通,这样将会引起MOSFET不能正常关断,从而损坏MOSFET。

因此,MOSFET的雪崩能力主要体现在以下两个方面:

1. 最大雪崩电流 ==>IAR

2. MOSFET的最大结温Tj_max ==>EAS、EAR 雪崩能量引起发热导致的温升

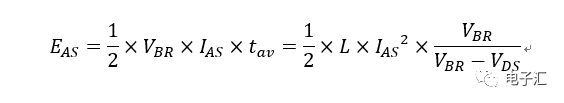

1)单次雪崩能量计算:

上图是典型的单次雪崩VDS,ID波形,对应的单次雪崩能量为:

其中,VBR=1.3BVDSS, L为提供雪崩能量的电感

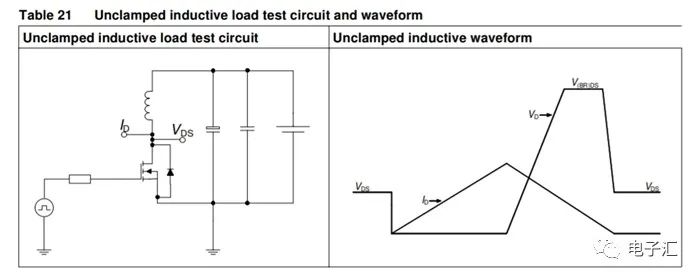

雪崩能量的典型测试电路如下:

计算出来EAS后,对比datasheet上的EAS值,若在datasheet的范围内,则可认为是安全的(当然前提是雪崩电流

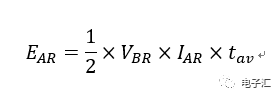

2)重复雪崩能量 EAR:

上图为典型的重复雪崩波形,对应的重复雪崩能量为:

其中,VBR=1.3BVDSS.

计算出来EAR后,对比datasheet上的EAR值,若在datasheet的范围内,则可认为是安全的(此处默认重复雪崩电流

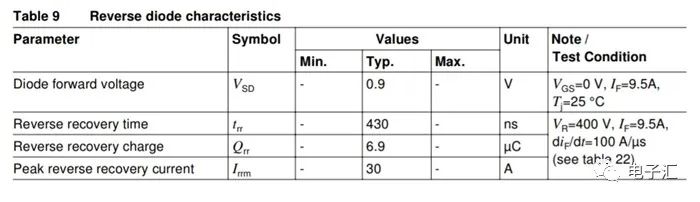

9、体内二极管参数

VSD,二极管正向压降 ==>这个参数不是关注的重点,trr,二极管反向回复时间 ==>越小越好,Qrr,反向恢复电荷 ==>Qrr大小关系到MOSFET的开关损耗,越小越好,trr越小此值也会小

10、不同拓扑 MOSFET 的选择

针对不同的拓扑,对MOSFET的参数有什么不同的要求呢?怎么选择适合的MOSFET?

1). 反激:

反激由于变压器漏感的存在,MOSFET会存在一定的尖峰,因此反激选择MOSFET时,我们要注意耐压值。通常对于全电压的输入,MOSFET耐压(BVDSS)得选600V以上,一般会选择650V。

若是QR反激,为了提高效率,我们会让MOSFET开通时的谷底电压尽量低,这时需要取稍大一些的反射电压,这样MOSFET的耐压值得选更高,通常会选择800V MOSFET。

2). PFC、双管正激等硬开关:

a) 对于PFC、双管正激等常见硬开关拓扑,MOSFET没有像反激那么高的VDS尖峰,通常MOSFET耐压可以选500V, 600V。

b) 硬开关拓扑MOSFET存在较大的开关损耗,为了降低开关损耗,我们可以选择开关更快的MOSFET。而Qg的大小直接影响到MOSFET的开关速度,选择较小Qg的MOSFET有利于减小硬开关拓扑的开关损耗

3). LLC谐振、移相全桥等软开关拓扑:

LLC、移相全桥等软开关拓扑的软开关是通过谐振,在MOSFET开通前让MOSFET的体二极管提前开通实现的。由于二极管的提前导通,在MOSFET开通时二极管的电流存在一个反向恢复,若反向恢复的时间过长,会导致上下管出现直通,损坏MOSFET。因此在这一类拓扑中,我们需要选择trr,Qrr小,也就是选择带有快恢复特性的体二极管的MOSFET。

4). 防反接,Oring MOSFET

这类用法的作用是将MOSFET作为开关,正常工作时管子一直导通,工作中不会出现较高的频率开关,因此管子基本上无开关损耗,损耗主要是导通损耗。选择这类MOS时,我们应该主要考虑Rds(on),而不去关心其他参数。

电子汇

全部0条评论

快来发表一下你的评论吧 !