在大多数情况下,隔离SPI非常简单。这些线路都是单向的,使用标准的数字逻辑电平来存储数据,并且没有集电极开路输出来支持电线和连接。只要速度相当适中,低于约5MHz时钟速率,大多数数字隔离器就可以完成这项工作,而不会大惊小怪。不幸的是,随着时钟速率的增加,有一个限制速度的问题。

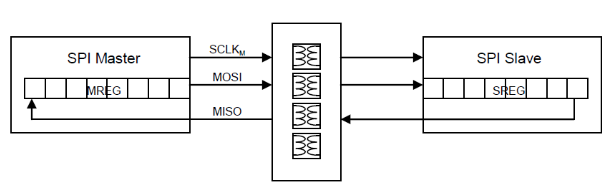

SPI的标准实现使用主器件生成的时钟信号SCLKM来控制总线上的所有数据移动。数据在主站和从站之间移动,就好像它们是两个相互连接的移位寄存器一样。主站和从站将数据提供给时钟一端的总线,并将数据读入另一端的移位寄存器。只要通过总线的往返传播延迟小于时钟周期的一半,该系统就可以正常工作,因为数据必须在下一个时钟边沿,半个时钟周期后返回主站。

.

将隔离集成到SPI总线中会限制SCLKM速率,因为来自从器件的数据必须在下一个时钟边沿之前到达主设备。由于发生这种情况所需的最短时间是最大传播延迟的 2 倍,因此这设置了时钟速率的最大限制。

我们通常建议将ADuM1401C用于此工作,因为它的保证速度为45 MHz,最大传播延迟为32 ns。当用于隔离SPI时,时钟半周期必须大于2个传播延迟,或最大SCLKM速率为7.8MHz。与数字隔离器的最大吞吐量相比,这是对数据速率的严重限制。事实上,数字隔离器需要小于5.5 ns的最大保证传播延迟才能支持45 MHz SPI。

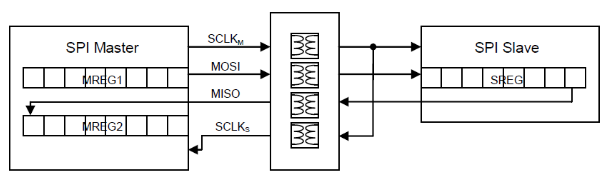

幸运的是,有一个直接的解决方案可以消除这个瓶颈。如果SCLKM信号与来自从器件的数据一起通过耦合器包装回去,则新信号SCLKS和数据之间的时序与耦合器的传播延迟偏斜相同。SCLKS可用于将数据时钟回主站,其速率再次由耦合器的保证数据速率设置。在每个事务之后,辅助缓冲区 MREG2 被复制到 MREG1 在本例中,这将 SPI 时钟速率提高到完整的 45MHZ,提高了 5 倍。该解决方案的成本是额外的耦合器通道来包装主时钟信号和主控制器中的额外输入移位寄存器

推荐用于SPI应用的iCoupler器件是ADuM1401C和ADuM3441。使用这些器件可以实现高达 50 MHz 的数据速率。

审核编辑:郭婷

全部0条评论

快来发表一下你的评论吧 !