模拟技术

ADC架构——SAR型

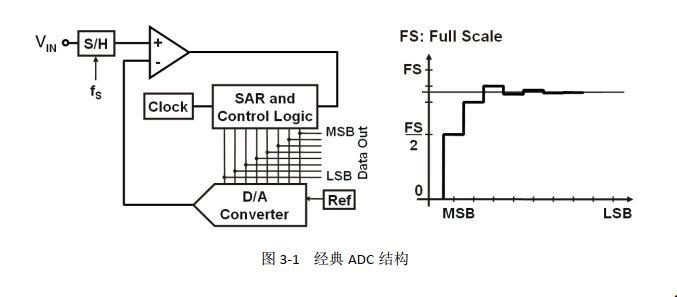

SAR型ADC,又叫逐渐逼近型ADC,属于瞬死值转换型-转换对象是模拟信号在采样时刻或前几个时刻抽样值,即时输出结果。

顾名思义,就是每个采集都是一位一位的确定正确输出,再比较下一位值。

优点:简单易用功耗低。

采样过程

A. 输入信号输入SH保持器中并保持,此时值为45,其实为模拟电压,所以45为伪代码。

B. 在第一个上升沿中,SAR先将最高位置为1,即把32送给DA转换器,DA转换器的输出模拟信号与SH比较,因为45大于32,比较器输出高,提示SAR的最高位置1,在CLK下降沿时,ADC将输出最高位数据(MSB)为1(1XXXXX).

C. 在第二个CLK上升沿中,SAR会将MSB-1值为1(11XXXX),SAR寄存器实际值为32+16=48大于45,比较器输出低,所以MSB-1位置为0(10XXXX).

D. 重复以上周期,在第三个CLK上升沿时,SAR会将MSB-2置为高位(101XXX),此时SAR寄存器实际值为32+8=40,小于45的,所以SAR会将MSB-2置为高(101XXX)。

E. 同理

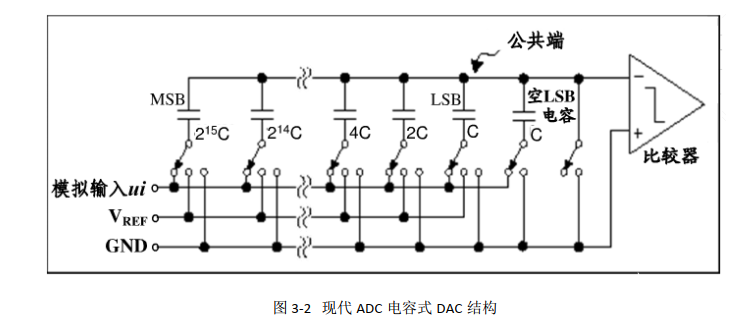

SAR 电容型电压

采样过程:电容阵列公共端接,即比较器输入负端,自由端连接到模型输入ui上,使得电容阵列上的电压与ui成正比,

保持阶段:公共端与地断开,所有电容的自由端接地,比较器输入电压等于-ui。

采样过程就是不断的将负端与正端比较,小于正端输入1,大于正端输出0.

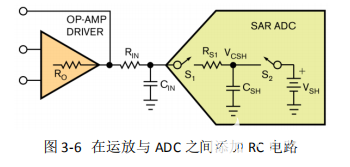

C.使用运算放大器驱动SAR型ADC

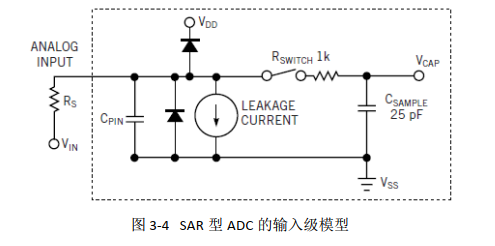

在设计SAR 型ADC时,首先需要考虑采样速率与外部信号源内阻,忽视这样子参数,会影响到ADC的输出结果。

信号进入ADC内部会遇到输入引脚电容Cpin和ESD(静电放电保护)二极管,这些对输入信号的影响很小,同时还可以忽略输入漏电流。

信号的采集速率主要与Rs和Cs有关。

当我们采用运放驱动SAR型ADC,由于运放具有高输入阻抗,低阻抗输出的特别,可以有效的降低外部的输入阻抗。

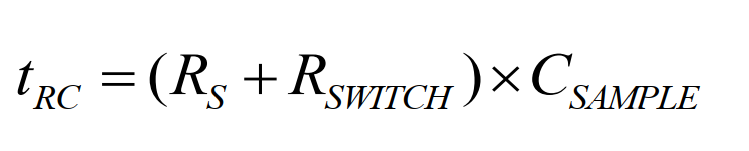

从时间常数关系式可以知道,当外部信号阻抗越大,时间常数就越大。

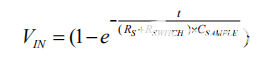

开关电容充电时间与电压的关系式如下:

在相同的时间,时间常数trc越大,Vin值越小,充放电时间越慢,一次的保持时间也就越慢。

举了例子:

一次采样时间为750ns,如果外部输入信号阻抗过大,导致采样时间超过750ns,就会出现欠采样,采样频率不够。 所以采用运放来驱动ADC。

同时运放的输出一般不会负责电容,(这方面具体什么原因我也不知道,在工作中师傅指点出来的),ADC端口一般都有输入电容,所以常常会在运放与ADC直接串电阻或者RC电阻。

全部0条评论

快来发表一下你的评论吧 !