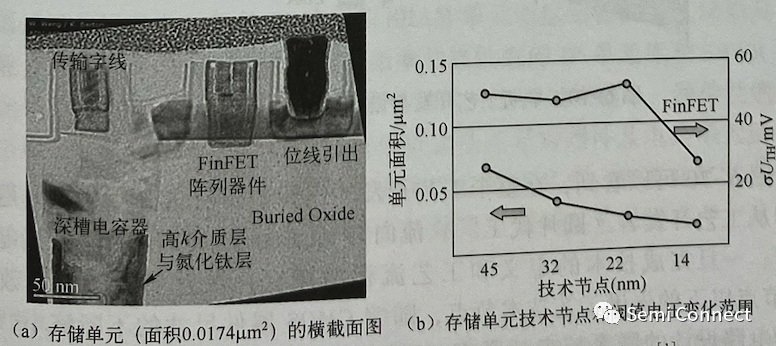

在当前计算密集的高性能系统中,动态随机存储器(DRAM)和嵌入式动态随机存取存储器(embedded-DRAM,eDRAM)是主要的动态快速读/写存储器。先进的 DRAM 存储单元有两种,即深沟槽(Deep Tench)式存储单元和堆叠(Slack)式电容存储单元。 70nm 技术节点后,堆叠式电容存储单元逐渐成为业界主流。为了使系统向更高速、高密度、低功耗不断优化,DRAM存储单元也在不断微缩(如14nm 工艺节点)。

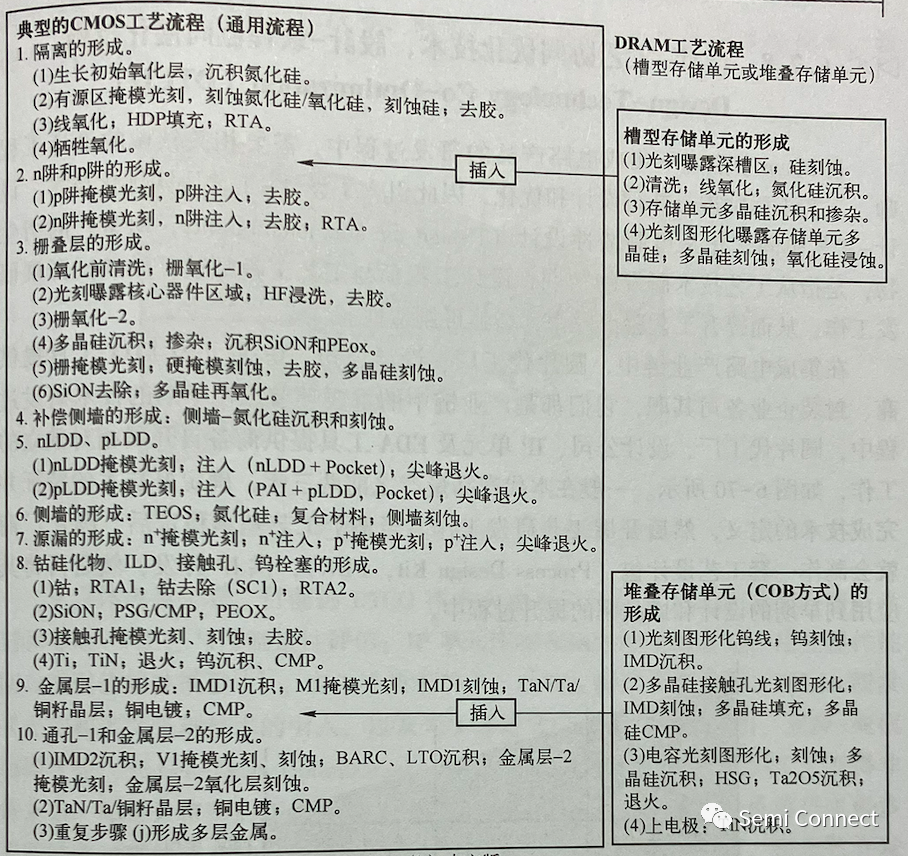

上图所示为 DRAM 的制造工艺流程。由图可见,堆叠式电容存储单元在 CMOS 场效应晶体管之后(MOL中)形成的,主要用于制造独立式的高密度 DRAM;而深沟槽式电容存储单元是在 CMOS 场效应晶体管之前(FEOL 之始)形成的,因此不会影响CMOS 场效应晶体管的特性,比较适合将DRAM 和逻辑电路集成在同一晶片上,因此称为eDRAM (嵌人式 DRAM)。

新型的 eDRAM 可以集成在 14nm 高性能的 FinFET 逻辑技术平合上(利用SOI 和高K 金属栅技术),如图所示。深沟槽式电容器在 FEOL 的开始阶段就已经形成,单元沟槽电容可达 10fF。电容器的上电极采用的是用原子层沉积(ALD)的TiN 薄膜。填充在沟槽电容器的重掺杂多晶硅连接到鳍式场效应晶体管(FinFET),即存储单元的传输管 (Pass Transistor)。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !