算术运算电路

算术运算电路的核心为加法器.

基本加法器

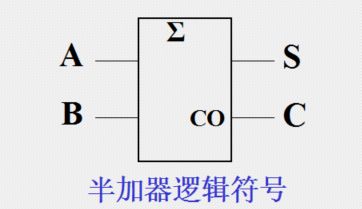

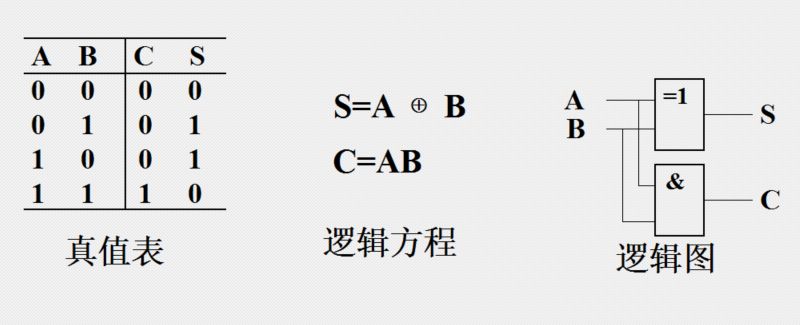

1. 半加器(HA)

仅考虑两个一位二进制数相加,而不考虑低位的进位,称为半加。

设: A、B为两个加数,S 为本位的和,C 为本位向高位的进位。则半加器的真值表、方程式、逻辑图如下所示

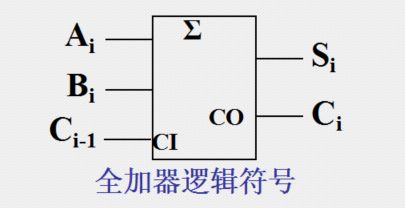

2. 全加器

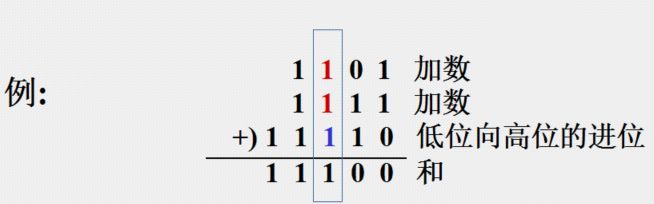

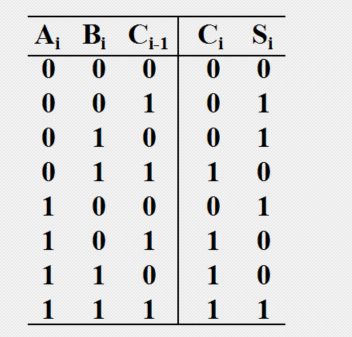

在多位数相加时,除考虑本位的两个加数外,还须考虑低位向本位的进位.

实际参加一位数相加,必须有三个量,它们是:

本位加数 Ai 、Bi ;

低位向本位的进位 Ci-1

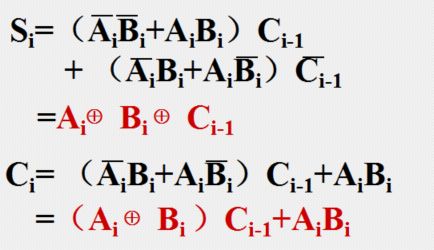

一位全加器的输出结果为:

本位和 Si ;

本位向高位的进位 Ci

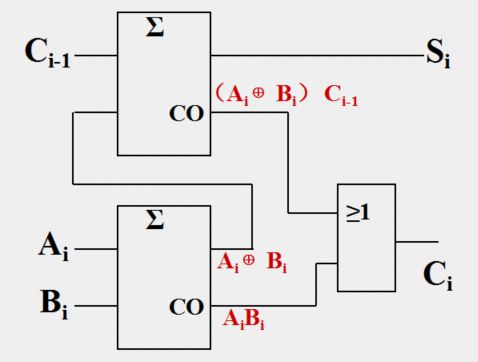

全加器电路设计:

由两个半加器实现一个全加器

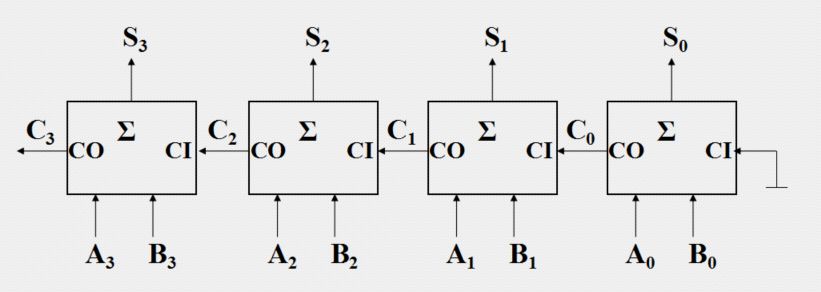

3. 串行进位加法器

当有多位数相加时,可模仿笔算,用全加器构成串行进位加法器.

四位串行进位加法器

串行进位加法器特点: 结构简单; 运算速度慢.

高速加法器

(1) 全并行加法器

特点: 速度最快,电路复杂。

(2) 超前进位加法器

设计思想: 由两个加数,首先求得各位的进位,然后再经全加器算出结果.

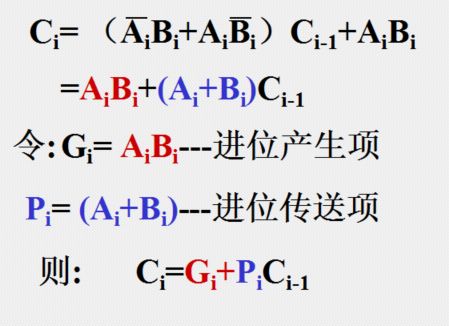

全加器的进位表达式:

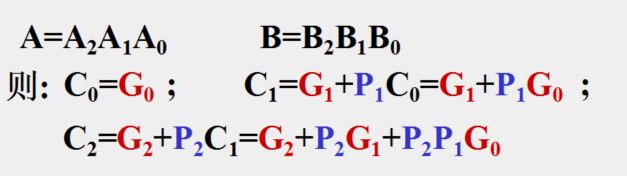

若两个三位二进制数相加

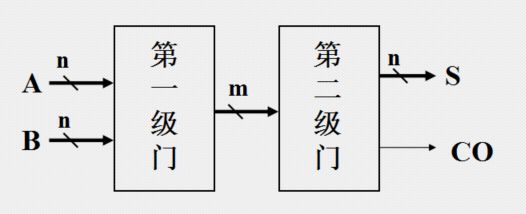

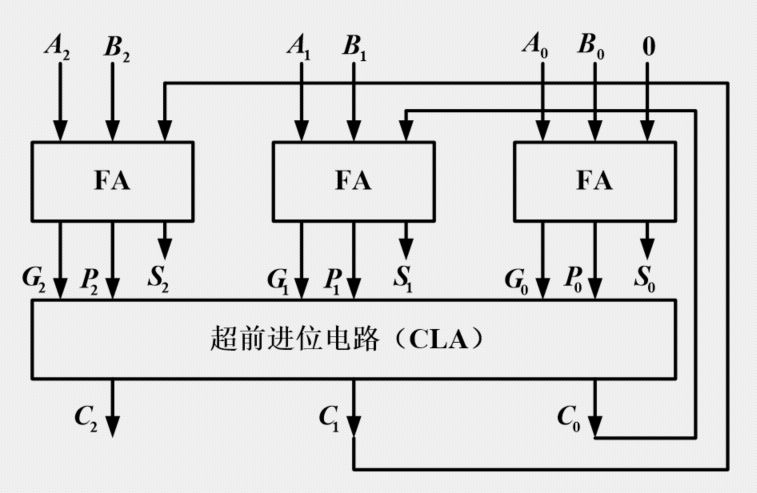

由Pi 、Gi 并经过两级门电路就可求得进位信号C.实际实现中,是将求Gi和Pi的电路放进全加器中,而将全加器中求进位信号的电路去除.

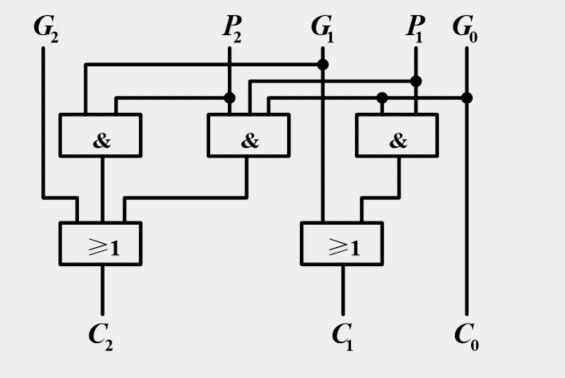

根据Gi 、Pi 来求进位信号C 的电路称为超前进位电路(CLA)

CLA逻辑图:

3位超前进位加法器

全部0条评论

快来发表一下你的评论吧 !