移动通信

根据工信部统计,截至2022年底我国移动通信基站总数达1083万个,其中5G基站有231万个,比例超过60%。而为了实现更深更广的网路覆盖,就有了小基站的出现,它能够深入室内做弱信号和盲区的定点覆盖,并按需提供大容量、低时延、高可靠性的网络服务,其作为5G时代的增量点,在整个生态中发挥重要的作用,预计到2025年,我国将新建共600万站。

随着使用者对网络速度、覆盖范围的需求与整体市场的快速发展,推动了基站从频率、带宽、效率到可靠性等多方面都有了更多的提升。对此,射频器件作为通信基站的核心也备受关注。这当中有一项能直接影响信号稳定的关键器件就是PLL时钟电路芯片,或称为频率源,该芯片是电子系统的信号源头,也被称作现代电子系统的“心脏”,在微波通信和FMCW雷达等领域皆占有至关重要的角色,其作用是给微波扫频信号提供一定分辨力的频率参考信号,并对微波信号输出频率进行逐点锁定,以得到高准确度和稳定度的扫频输出信号。

PLL时钟电路芯片最主要的特点是能使频率稳定度高,尤其是相位噪声低,优点是使用灵活且易于控制,因此对于现代电子系统来说,为了能实现更稳定的频率、更小的频差,在许多情况下都会采用时钟电路芯片。然而,它的技术难度大,因此一直以来都是国外大厂的天下,但目前已有国内厂家打破了这个垄断的局面,推出自行研发的芯片方案。

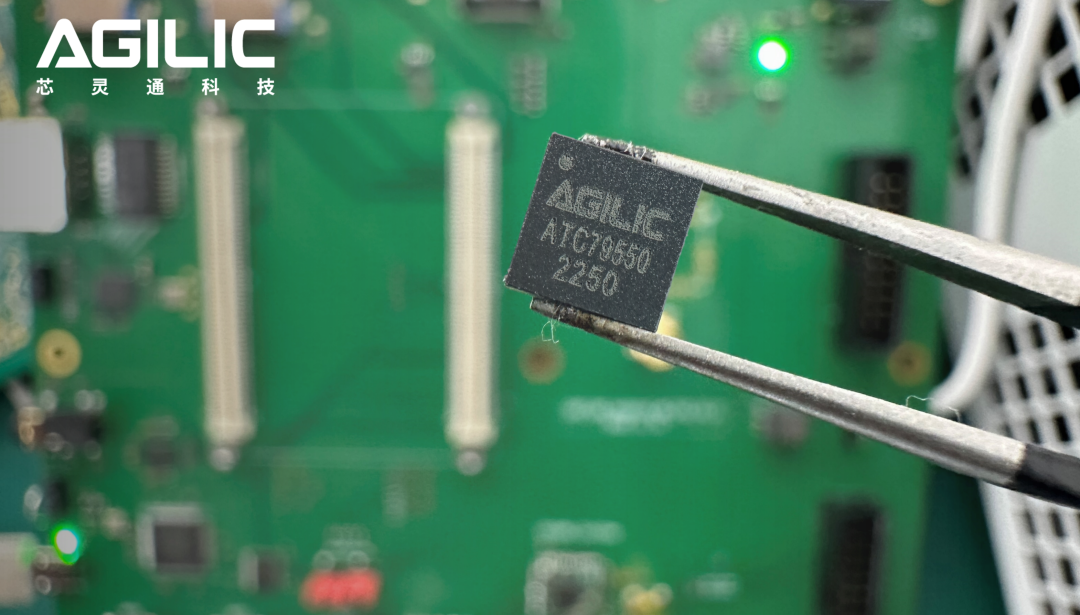

新锐射频芯片设计公司芯灵通(天津)科技有限公司于今年3月发表的PLL时钟电路芯片ATC79550,是一颗能实现小数分频或整数分频的锁相环PLL频率综合器。其基波输出频率范围为在3540MHz至4760MHz,并集成压控振荡器(VCO),可完成2/4/8/16分频输出,杂散抑制达到77dBc,10KHz处相位噪声小于-87dBc/Hz。ATC79550能被应用在移动通信基站、无线局域网、低频时钟发生器、FMWC雷达系统、卫星导航和防撞系统等多种场景,当前已量产,并开始于客户端送样。 目前,国内仅有极少数的厂家拥有PLL时钟芯片的关键技术,而芯灵通科技便是其中之一,并且真正具备量产能力。芯灵通科技CEO傅海鹏表示,“PLL时钟芯片技术基本上是由国际大厂所垄断,而中国每年对此类型的芯片进口采购额超5000万,而在中美贸易战的影响持续扩大下,我们希望通过对该技术的掌握能降低被卡脖子的风险,并助力芯片国产化“。

▲芯灵通科技自行研发的PLL时钟电路芯片 芯灵通推出的ATC79550面积小、性能高,用于提供高稳定度的时钟、本振信号、发射信号。通过突破超低相位噪声设计的技术难点,能使宽带射频通信的频率源器件得到更高的性能。除此之外,其自研的IP能更有效地降低成本、提高研发效率并有助于产品的迭代。芯灵通科技的核心团队在射频芯片设计领域已有十五年以上的经验,拥有丰富的技术积累和自主知识产权与多项专利,具备较强的技术壁垒,提供前沿的产品和解决方案。

芯灵通(天津)科技有限公司成立于2021年,坐落于天津市滨海高新区,是一家Fabless半导体芯片设计公司,专注于射频FEM与射频SoC(收发机芯片)的研发。产品主要面向物联网、工业与车载WiFi、移动通讯、毫米波雷达与超宽带SoC。并致力于提供小面积、高效率、高集成的宽带射频芯片与解决方案,实现国产化替代。

编辑:黄飞

全部0条评论

快来发表一下你的评论吧 !