锁相环英文名称PLL(Phase Locked Loop),中文名称相位锁栓回路,现在简单介绍一下锁相环的工作原理。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图1所示。

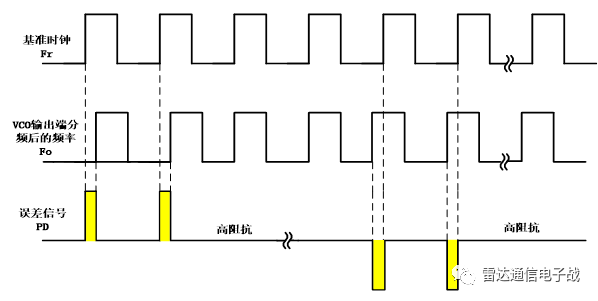

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号(PD),经环路滤波器滤波后形成电压VR来控制压控振荡器的电压,该电压对振荡器输出信号的频率实施控制。 假设外部基准时钟产生的频率为Fr,电压振荡器VCO产生的频率为Fo,当Fr和Fo输入相位比较器的输入端时,比较器就会输出比较误差信号PD,如图2所示:

当Fr>Fo时,也就是VCO分频后的振荡频率比基准频率低的时候,此时相位比较器的输出PD如图2所示,比较器会输出正脉冲信号,使VCO的振荡频率提高。

当Fr时,也就是vco分频后的振荡频率比基准频率高的时候,此时相位比较器的输出pd如图2所示,比较器会输出负脉冲信号,使vco的振荡频率降低。<>

误差信号PD通过环路滤波器的积分,便可以得到直流电压VR,由于控制电压VR发生变化,VOC振荡频率会发生变化,使得Fr=Fo,当Fr=Fo时,误差信号PD会成为高阻状态,使得PLL锁栓。

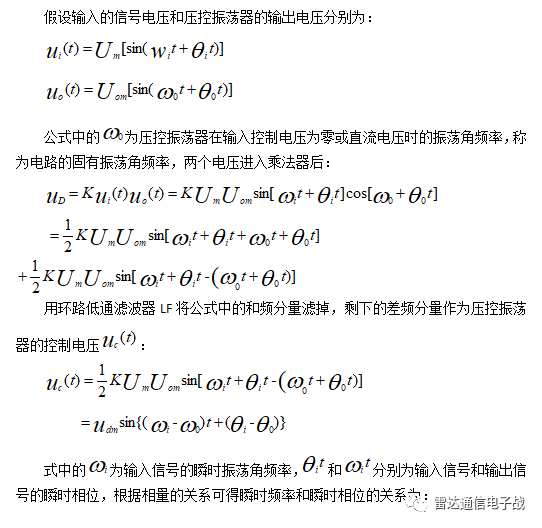

锁相环中的鉴相器由模拟乘法器组成的鉴相器电路如图3所示:

实际应用中,假设外部基准时钟100MHz,VCO输出为1000Mhz,那么可以将VOC输出的频率进行2分频为500MHz运用到实际应用电路中,将VOC输出的频率进行10分频为100MHz运用到实际应用电路中,需要单独输出一路对VCO进行10分频到和外部基准时钟一样的频率用来校准VCO输出的1000Mhz时钟。

总之,外部的100MHz的基准时钟不是用来使PLL产生时钟的,是PLL会产生一个时钟VCO,但是这个时钟是一个不稳定的时钟,需要用外界一个稳定的晶体时钟进行校准。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !