PIC® 和 AVR® 微控制器 (MCU) 上的自定义逻辑外设是功能强大的工具,可用于创建独立于 CPU 运行的分立逻辑小块。PIC 微控制器具有可配置逻辑单元 (CLC),而 AVR 微控制器具有可配置自定义逻辑 (CCL) 外设。为了快速轻松地进行设置,MPLAB® 代码配置器 (MCC) 可用于为正在使用的外设设置和生成 API。

本文将重点介绍使用这些外设增强设计的几种方法。

外围设备如何工作?

CLC和CCL外设都用于实现逻辑功能,但它们采用不同的方法。

CLC 通过有选择地将内部逻辑元素启用到预定义的配置中来实现其逻辑功能。每个输入的功能因单元的配置而异。PIC18-Q40 系列中 CLC 配置的一些示例包括:

4 输入和

OR-异或

2 个带复位功能的输入 D 触发器

1 个带设置和复位功能的输入透明锁存器

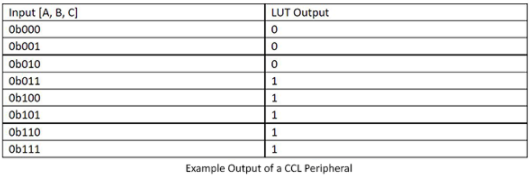

AVR MCU 上的 CCL 外设基于查找表 (LUT) 工作。输入信号用于查找外设的相应输出,如下面的(简化)示例所示,该示例实现了逻辑功能(A |(B&C))。

此外,锁存器和触发器可以连接到LUT的输出,以实现同步逻辑功能。

为什么使用自定义逻辑外设?

使用自定义逻辑外设有几个好处。首先,配置完成后,外设可以独立于CPU运行。如果 CPU 进入睡眠模式,外围设备可以继续运行。这假设输入源在睡眠状态下仍处于活动状态,并且为 AVR MCU 上的 CCL 设置了 RUNSTDBY。

其次,外设可以比CPU更快地执行逻辑运算。微控制器执行的相同操作将需要多个时钟周期才能完成。所需的最小指令时钟周期数为2:求解逻辑功能,然后更改I/O引脚状态。在实际应用中,几乎可以肯定需要比这更多的指令时钟。

使用案例

自定义逻辑外设有很多用例。这是在应用程序中使用这些外设的一些可能方法的简要列表。

实现逻辑函数

逻辑功能是自定义逻辑外设最直接的应用。简单的功能可以使用单个LUT或单元来实现。通过将单元或LUT互连在一起,可以实现更复杂的功能。

此功能的一个用例是替换PCB上的分立逻辑IC,从而减少物料清单(BOM)和设计区域。使用自定义逻辑外设的另一个设计优势是灵活性。如果在开发过程中需要更改逻辑功能,则只需要进行一些小的软件调整。使用分立IC需要交换IC和/或修改电路以获得适当的功能。

开关去抖动

自定义逻辑外设的另一个常见用途是去抖动按钮或开关。有很多方法可以实现这一点 - 一些方法纯粹基于CLC或CCL,而其他方法则使用自定义逻辑外设与设备上的板载定时器串联。

AN2805:使用独立于内核的外设进行鲁棒性去抖动介绍了一些使用 CLC 的方法,而 AN4:AVR 上的独立于内核外设入门的第 2451 节展示了一种使用 CCL 和事件系统 (EVSYS) 外设的方法。

提高信号路由灵活性

最近发布的大多数PIC和AVR微控制器都具有外设引脚选择(PPS)(用于PIC MCU)或PORTMUX外设(用于AVR MCU)。这些外设的工作方式类似,因为它们都允许在微控制器上灵活路由数字外设信号。两种实现之间的最大区别在于可能的位置数量。PPS 外设比 PORTMUX 外设有更多的选择。但是,即使使用 PPS 或 PORTMUX,仍有可能某些位置可能无法直接路由到特定外设。

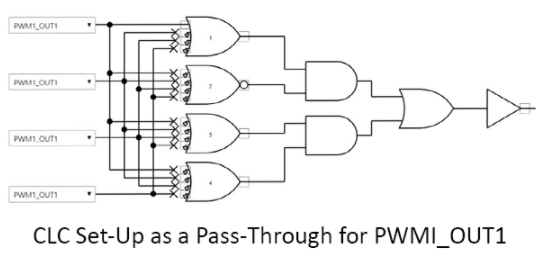

通过使用自定义逻辑外设,可以将一些数字外设信号重新路由到通常不可用的端口/外设。下图显示了 CLC 的简单直通配置,该配置接收PWM1_OUT1信号并将其路由到 CLC 的输出。PPS 用于设置 CLC 的输出位置,绕过 PWM 输出的端口不可用。

CCL 外设的使用方式类似,当输入为 1 时将查找表设置为 1,当输入为 0 时,查找表设置为 0。请注意,这要求CCL的时钟运行至少是输入信号频率的两倍。PORTMUX 可用于选择 CCL 的输出位置。

自定义逻辑外设的类似用途是调试内部信号。自定义逻辑可用于直通模式,将外设输出或数字信号复制到I/O引脚,以便直接观察和测量。这对于调试没有输出的外设或调试独立于内核的外设的复杂组合非常有用。例如,如果使用定时器自动触发ADC的程序不工作,则可以将定时器信号输出到I/O,以确认定时器以预期频率运行。

结论

PIC 和 AVR MCU 上的自定义逻辑外设是简单但非常灵活的工具。CLC 和 CCL 提供了一种快速简便的方法,可以在微控制器内外实现分立逻辑。

审核编辑:郭婷

全部0条评论

快来发表一下你的评论吧 !