大家好!今日给大家介绍下Virtual Input/Output IP 核的几个重要参数。

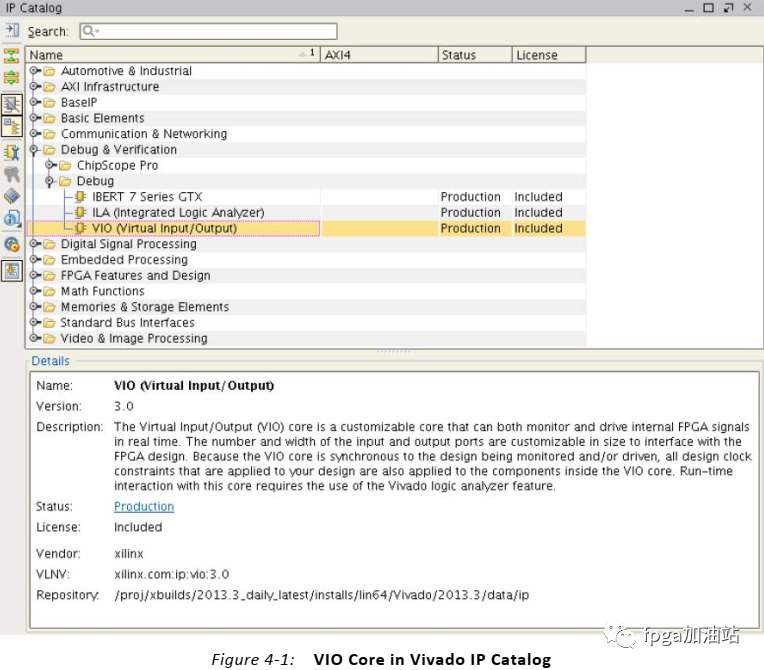

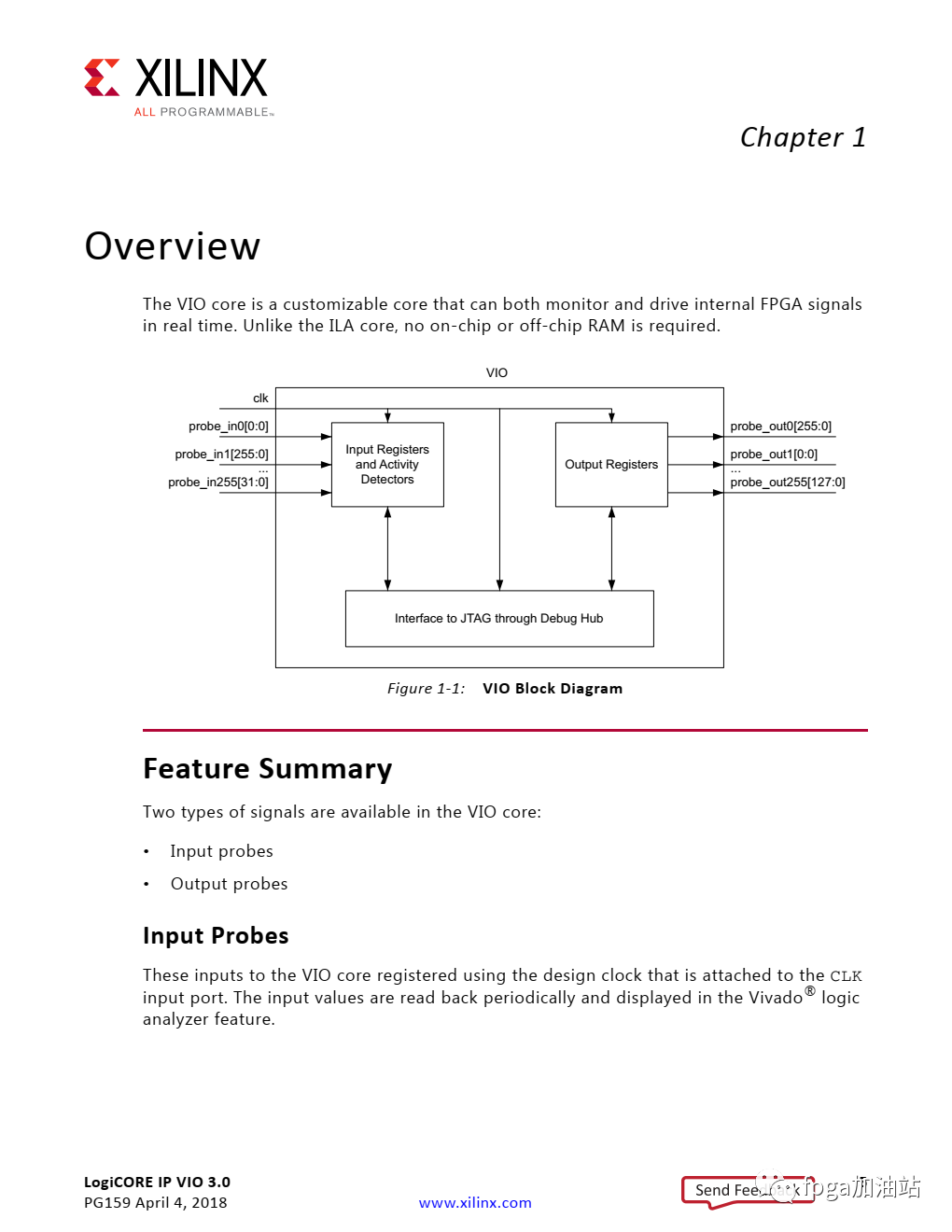

VIO内核是一个可定制的内核,可以实时监控和驱动内部FPGA信号。与ILA内核不同,不需要片内或片外RAM。

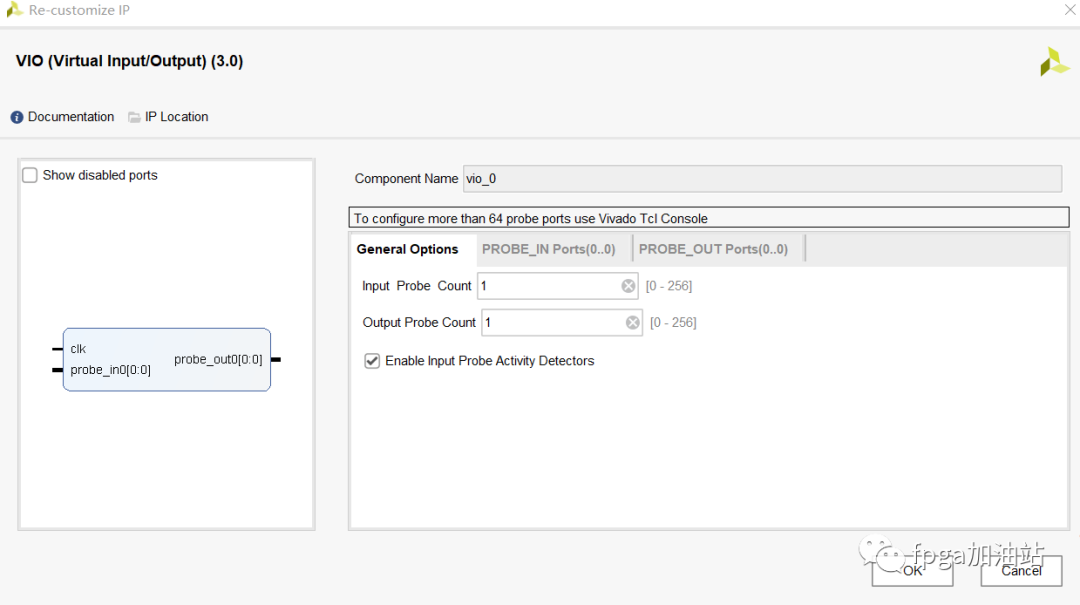

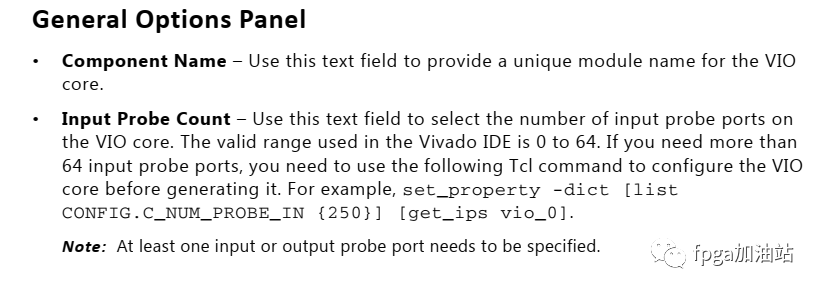

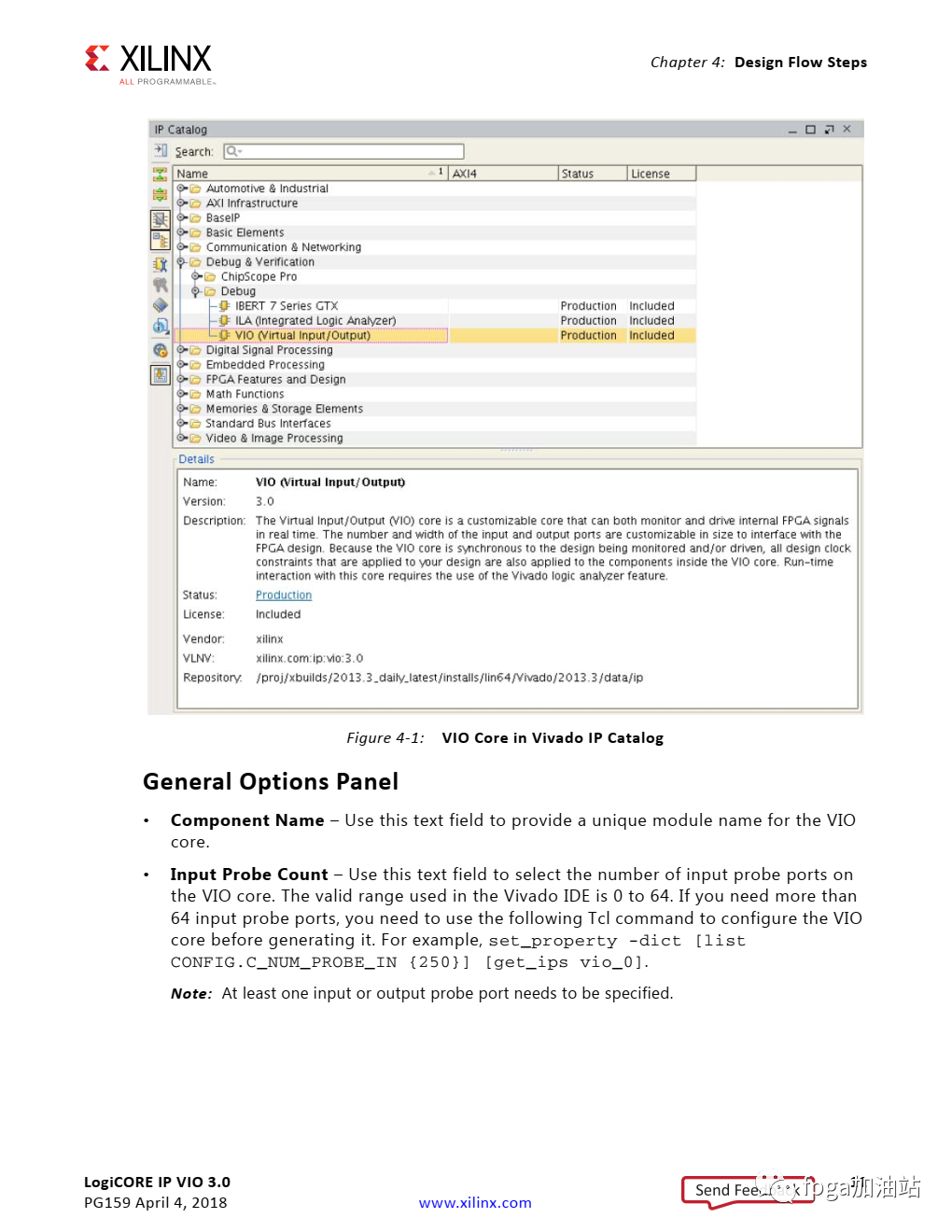

•组件名称–使用此文本字段为VIO核心提供唯一的模块名称。

•Input Probe Count(输入探针计数)–使用此文本字段选择VIO内核上的输入探针端口数。Vivado IDE中使用的有效范围是0到64。如果需要64个以上的输入探测端口,则需要使用以下Tcl命令在生成VIO内核之前配置它。例如,set_property-dict[list CONFIG.C_NUM_probe_IN{250}][get_ips VIO_0]。

注:至少需要指定一个输入或输出探测端口。

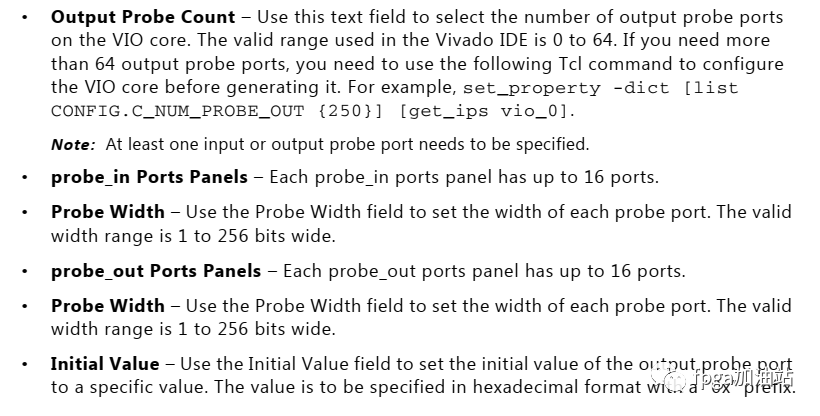

•输出探针计数–使用此文本字段选择VIO内核上的输出探针端口数。Vivado IDE中使用的有效范围是0到64。如果需要64个以上的输出探测端口,则需要使用以下Tcl命令在生成VIO内核之前配置。例如,set_property-dict[list CONFIG.C_NUM_probe_OUT{250}][get_ips VIO_0]。

注:至少需要指定一个输入或输出探测端口。

•probe_in Ports面板–每个probe_in Ports面板最多有16个端口。

•Probe Width(探针宽度)–使用Probe Wighth(探针长度)字段设置每个探针端口的宽度。有效宽度范围为1到256位宽。

•probe_out端口面板–每个probe_out-Ports面板最多有16个端口。

•Probe Width(探针宽度)–使用Probe Wighth(探针长度)字段设置每个探针端口的宽度。有效宽度范围为1到256位宽。

•初始值–使用初始值字段将输出探针端口的初始值设置为特定值。该值将以带“0x”前缀的十六进制格式指定。

左右滑动查看:

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !