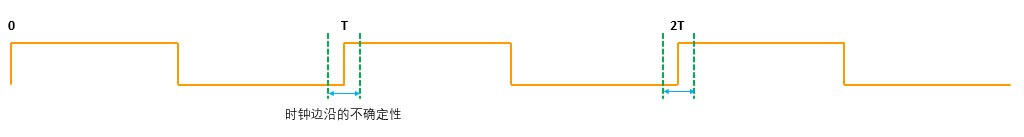

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在理想值附近的一个范围内,从而造成相邻的时钟边沿存在偏差。在时序分析时,时钟抖动是一个重要的因素。多种因素会导致时钟抖动,包括PLL回路噪声、电源纹波、热噪声以及信号之间的串扰等。

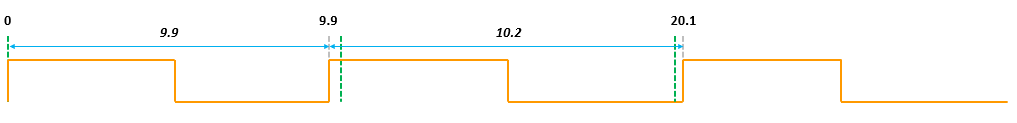

下图显示了时钟抖动的基本概念。假定PLL生成时钟频率为100MHz,那么周期就是10ns。理想情况下,时钟上升沿将出现在0ns、10ns、20ns、30ns等时刻。然后,PLL并非是一个理想时钟源,所以,实际的时钟上升沿可能会出现在0ns、9.9ns、20.1ns、29.8ns等时刻。换言之,实际是时钟沿将出现在nT-jitter到nT+jitter的范围内(这里n为整数)。需要注意的是图中时钟边沿的不确定性对于时钟上升沿和时钟下降沿都是有效的,前者为整周期抖动,后者为半周期抖动。为方便起见,我们只讨论整周期抖动。

时钟抖动的几种类型:

周期抖动

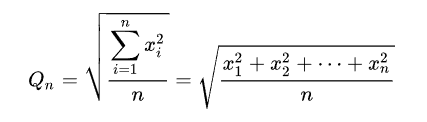

周期抖动的定义是实际时钟周期与该时钟的平均周期的偏差,即T1-Tavg,T2-Tavg,T3-Tavg,……,TN-Tavg(其中Tavg为平均周期)。这其实是周期抖动的计算方式之一,被称为峰峰周期抖动(Peak-to-peakjitter)。周期抖动还可以采用RMS(Root MeanSquare,平方平均数,又名均方根)周期抖动来计算。计算公式如下图所示。式中xi代表一个峰峰周期抖动。

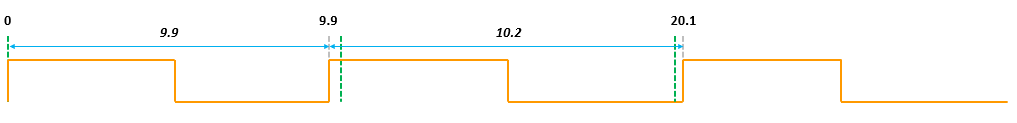

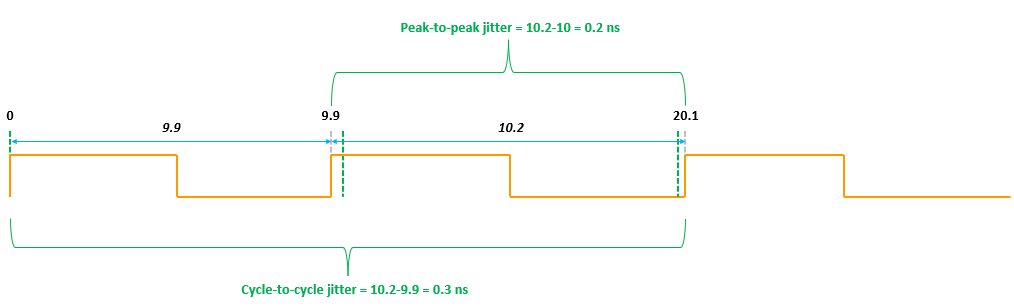

下图显示了峰峰周期抖动。图中绿色虚线为理想时钟上升沿位置,灰色虚线为实际上升沿位置。Tavg即为(9.9+10.2)/2,T1=9.9,T2=10.2,从而可计算出T1-Tavg和T2-Tavg。实际测量时要选择多个样本周期。

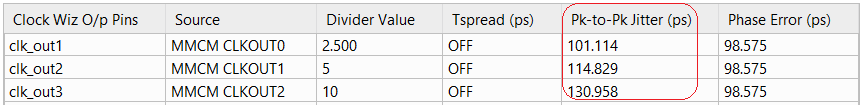

在Vivado Clocking Wizard IP中,会给出生成时钟的峰峰周期抖动,如下图所示。

相邻周期抖动

相邻周期抖动(Cycle-to-cycle jitter),顾名思义,指的是相邻的两个时钟周期之间的周期长度差异,如下图所示。第一个时钟周期长度为9.9ns,与之相邻的第二个时钟周期长度为10.2ns,所以相邻周期抖动为10.2-9.9=0.3ns。实际测量时要选择多个周期样本。需要注意的是相邻周期抖动只关注两个连续周期之间的周期长度变化,并不参考任何理想时钟。不难发现,相邻周期抖动就是峰峰周期抖动的差分:

(T1-Tavg)-(T2-Tavg)=T1-T2

最后,我们用一张图即可展示峰峰周期抖动和相邻周期抖动的差异,如下图所示。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !