到目前为止,这是一个有趣的旅程,研究了ADC中潜在噪声源。我们研究了模拟和数字电源输入以及接地连接。沿着这些思路,我们还研究了PSRR和PSMR。之后,我讨论了涉及ADC模拟输入的噪声。现在,让我们来看看ADC上需要注意噪声的最关键的地方之一——ADC时钟输入。

通过时钟电路进入ADC的任何噪声都可能直接进入输出。ADC中涉及该电路的噪声机制可以被认为是混频器。在查看噪声时以这种方式考虑此输入确实可以正确看待事物。通过时钟输入进入ADC的噪声频率将被混入模拟输入信号,并显示在转换器输出端的FFT中。

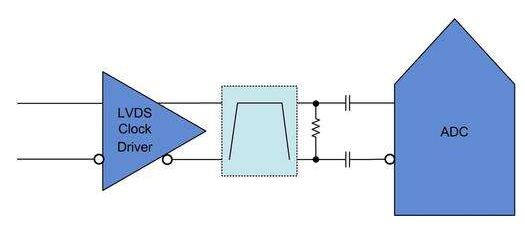

与时钟电路和相关物理布局相关的几点需要注意。首先,最好将时钟驱动器放置在ADC附近,以保持布线尽可能短。时钟信号传播的距离越短,拾取系统中可能存在的任何错误噪声的可能性就越小。尽管大多数ADC时钟都是差分的,并且提供抗共模噪声的能力,但并没有完全的抗扰度。一种选择是在ADC的时钟频率处添加一个中心频率的带通滤波器,如下图所示。

图1.典型ADC LVDS时钟电路(滤波器可选)。

该滤波器应放置在靠近ADC的位置,以消除可能耦合到系统中时钟信号的任何噪声。最好将滤波器放置在靠近ADC的位置,因为将滤波器放置在靠近时钟驱动器的位置,会使噪声在滤波器之后耦合到时钟信号上,并进入ADC。

不仅要注意时钟驱动器和ADC的放置和布线,而且考虑时钟驱动器本身也很重要。利用良好的布局和路由技术,并选择性地滤波时钟信号有助于减少外部噪声源,但不要忘记考虑时钟源本身。选择具有低相位噪声的时钟驱动器非常重要。但是,您也可以根据自己的喜好关注抖动。

审核编辑:郭婷

全部0条评论

快来发表一下你的评论吧 !