电子说

如 76059 - Versal ACAP DDRMC - DDR4 和 LPDDR4/x PCB 仿真支持文章中所述,使用 Versal ACAP DDRMC 时,Vivado 会为外部参考时钟端口自动生成所需 I/O 标准约束。 这些约束可确保输入参考时钟搭配所需参考电路使用时,能遵循各数据手册要求正常运作,并且 PVT 运作期间也同样如此。

虽然可以为 DDRMC 外部参考时钟使用其他 I/O 标准和约束组合,但不建议违背这些设计准则要求。 对于此类情境,用户需查询 Versal ACAP 数据手册,了解受支持的 I/O 标准和输入要求。

此外,受支持的 I/O 标准和 I/O 约束还存在其他限制,需交叉比对《Versal ACAP SelectIO 资源架构手册》(AM010) 以了解这些限制。 在某些情况下,如不使用 IP 生成的默认设置,将导致与用户生成的设置产生冲突,而在此情况下唯一的解决途径是在 Vivado 外部手动修改设计文件中 IP 生成的约束。

解决方法:

当 AXI_NOC 实例配置为包含集成的 DDRMC 时,在每个 DDRMC 的 IP 外部边界处会出现 1 个 sys_clk 端口。此端口必须连接到一个时钟源,用户可在 AXI NoC 配置 GUI 的“DDR Basic”(DDR 基本设置)选项卡上选择该时钟源的频率。“DDR Basic”选项卡还提供了以下三个可用的“System Clock”(系统时钟)选项以供选择:“Differential”(差分)、“No Buffer”(无缓冲)或“Internal”(内部)。

“Differential”和“No Buffer”都要求在 DDRMC 使用的三个 XPIO bank 之一中的“Global Clock (GC)”(全局时钟)输入管脚上布局差分时钟源。“Internal”使用 CIPS 中片上生成的内部 HSM1 参考时钟。 设计中任一或所有 DDRMC 实例都能使用该内部 HSM1 参考时钟。

外部参考时钟应保持稳定运行一段时间,然后才能启动 DDRMC。

外部参考时钟应持续运行,既不停止也不更改时钟周期。

外部参考时钟的 RMS 抖动应少于 3 ps,占空比应为 50/50。

不支持扩展频谱时钟设置。

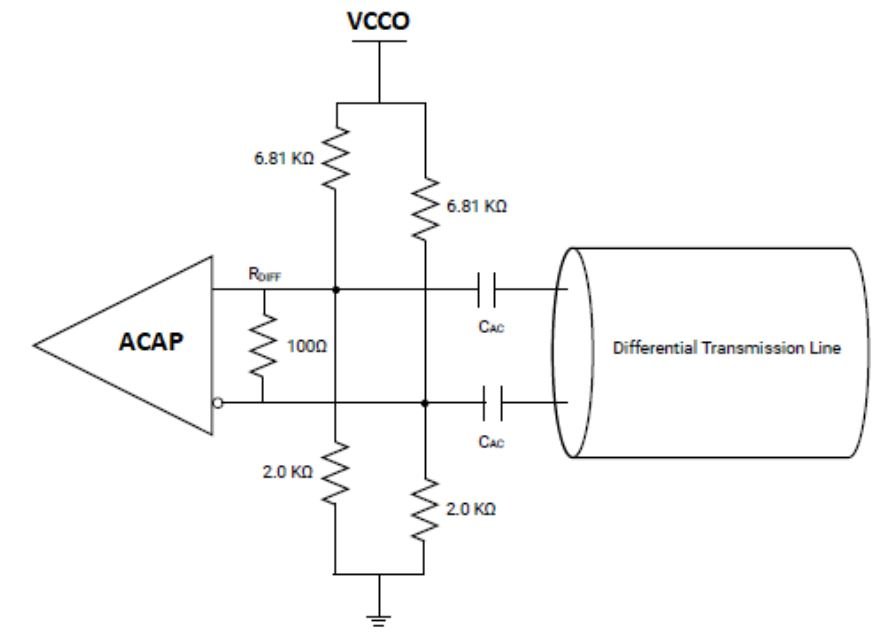

下图显示的是使用 DDR4、LPDDR4 或 LPDDR4X 的 Versal ACAP DDRMC 应用所期望的外部参考时钟偏置电路。

VCCO 将因使用的存储器技术而异:

DDR4 将使用 1.2 V

LPDDR4 将使用 1.1 V

LPDDR4X 将使用 1.2 V

AC 耦合电容器建议为 0.1 uF。

如需了解 ACAP DDRMC 接口的其他设计要求,请参阅《Versal ACAP PCB 设计用户指南》(UG863)。

以下列示了 IP 生成的默认 I/O 标准和约束以供参考:

DDR4

LPDDR4

LPDDR4X

如需获取有关 I/O 标准和 IP 生成的默认约束的更多详细信息,请参阅 76059 - Versal ACAP DDRMC - DDR4 和 LPDDR4/x PCB 仿真支持文章。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !