存储技术

Storage-3---并行Nor Flash

1.特征属性

并行(ISA)Nor Flash有5V、3V和1.8V三种不同的供电体系,容量从2Mb-1Gb,具有x8、x16可选配置的引导和统一扇区架构。Parallel Nor Flash具有高性能、低功耗、高耐久性、高可靠性的特点。

部分Parallel Nor Flash提供性能增强的产品,支持突发模式和地址数据多路复用(AD Mux)使得具有更快的有效编程和读取时间,更加适合要求更高密度、更好性能和更低功耗的应用程序的需求。

2.结构

Parallel Nor Flash已经很接近DDR了,它有单Bank和多Bank体系,其中多Bank体系结构可以实现同时读写功能,更快的有效编程和突发读取时间,非常适合要求高性能和低功耗的应用。

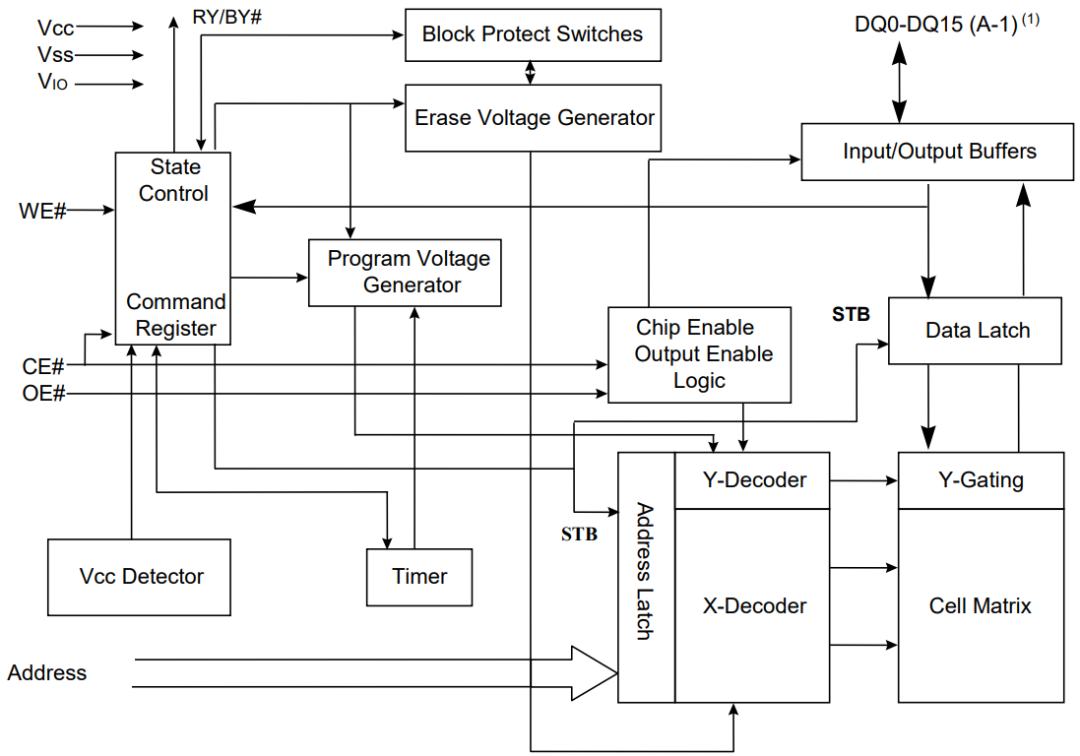

图3-1:Parallel Nor Flash的典型结构

3.接口

Parallel Nor Flash数据和地址接口遵循JEDC规范,读写接口在引导和统一扇区架构中提供,配置为x8、x16。

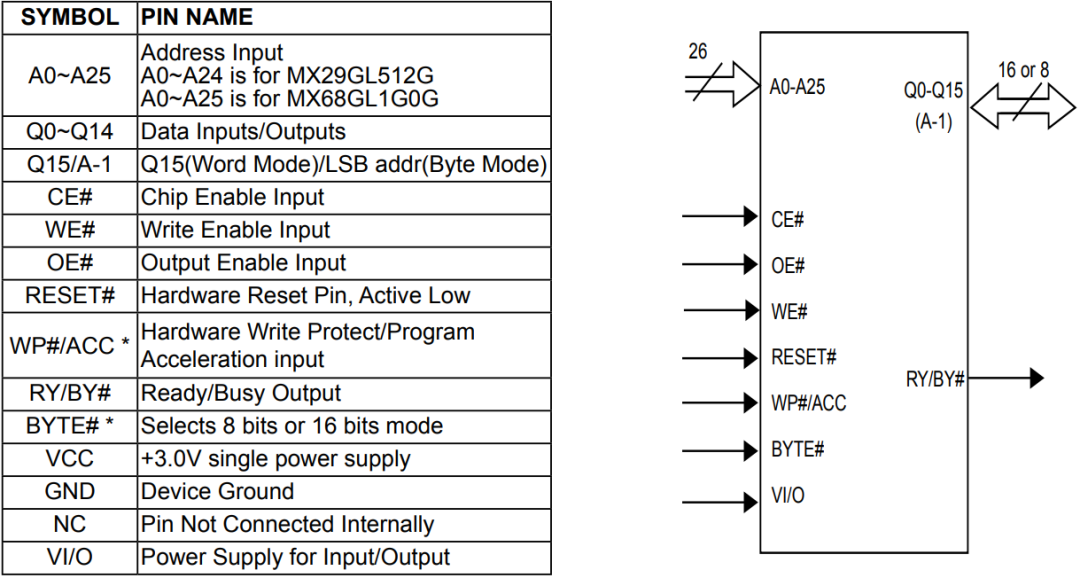

图3-2:Parallel Nor Flash的简图和基本引脚定义

不同的品牌的并行Nor Flash,数据线位宽没有区别,但是地址线的数量受容量和内部结构的影响,会有一些差异,设计时不能按照标准品来进行使用。

4.传输速度和容量

Parallel Nor Flash的传输速度评估和串行不太一样,串行一般使用时钟频率,吞吐量,但Parallel Nor Flash的定位已经不再是纯粹的静态存储器件,而是需要运行程序。所以Parallel Nor Flash使用写入速度(ns)和读取速度(ns)来评估,转换吞吐量需要使用页面容量×访问时间来获得。

5.MCP

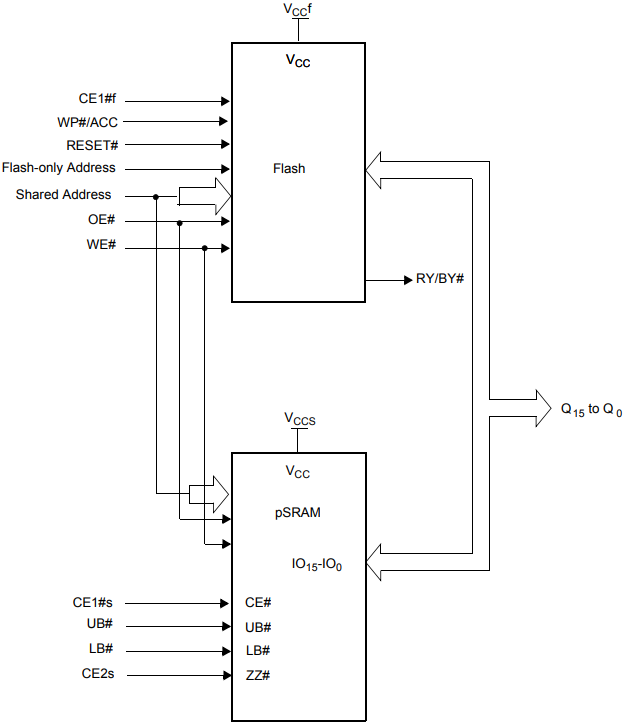

MCP,即Multi Chip Package,多芯片封装,将多种存储芯片封装成一个芯片,体积小节约PCB空间,简化电路设计。MCP解决方案组合为嵌入式和无线应用程序的使用提供了灵活的选择和快速的上市优势,凭借较小的占地面积和向后兼容的引脚,客户可以选择不同的密度来满足其经济高效的解决方案。如图3-3和图3-4基于Flash的MCP方案有两种:Parallel Nor-Based MCP--->Parallel Nor Flash + Pseudo Static RAM (pSRAM)和Nand-Based MCP--->SLC Nand Flash and LPDDR2。

图3-3:Parallel Nor Flash + Pseudo Static RAM的MCP

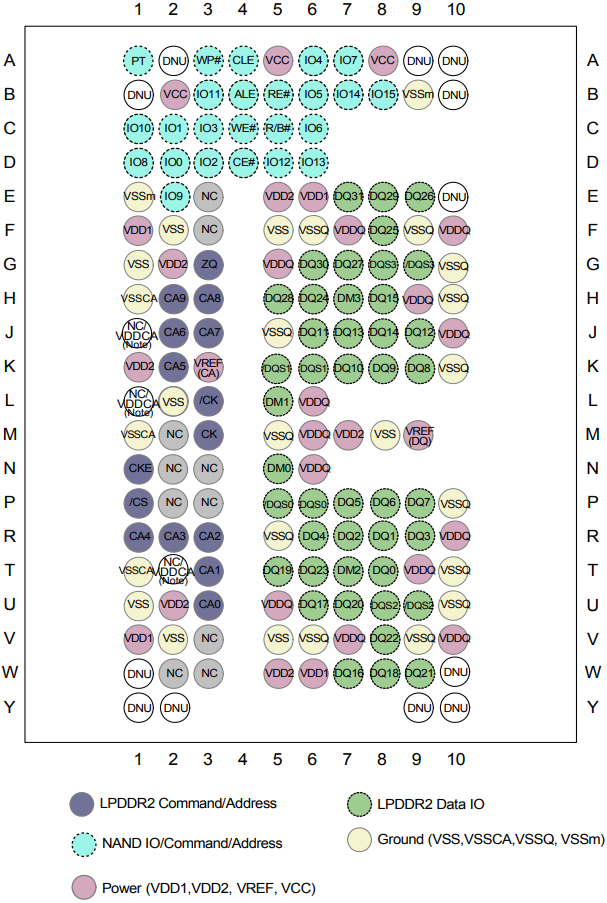

图3-4:SLC Nand Flash and LPDDR2的MCP(NAND x16+LPDDR x32)

图3-4也支持Nand x8+LPDDR x32,Nand x8+LPDDR x16,Nand x16+LPDDR x16多种配置。对MCP的理解,可以认为是两枚独立的芯片叠封在一起,但调试和使用则需要作为一个系统来进行。实际上Parallel Nor Flash的市场越来越小,它的多数使用场景逐渐被串行Nor Flash(吞吐量大,引脚数少,调试便捷)取代,优势越来越不明显。

最后补充一点上节Serial Nor Flash,SOC选用Serial Nor Flash的考虑点之一是将Boot启动程序放置于Serial Nor Flash中,这样SOC直接从Serial Nor Flash启动就会很快。而从eMMC启动,SOC需要先将Boot程序搬运(拷贝)到DDR上,然后SOC在DDR上运行Boot程序,整个系统才开始运行。选择哪种启动介质,这个取决于系统的大小、Boot程序的复杂度、启动时间要求和成本考虑。

全部0条评论

快来发表一下你的评论吧 !