概述

本文介绍一个FPGA开源项目:UDP千兆以太网光通信。利用SFP接口,可以通过使用SFP转RJ45模块或者直接使用光纤进行以太网通信。

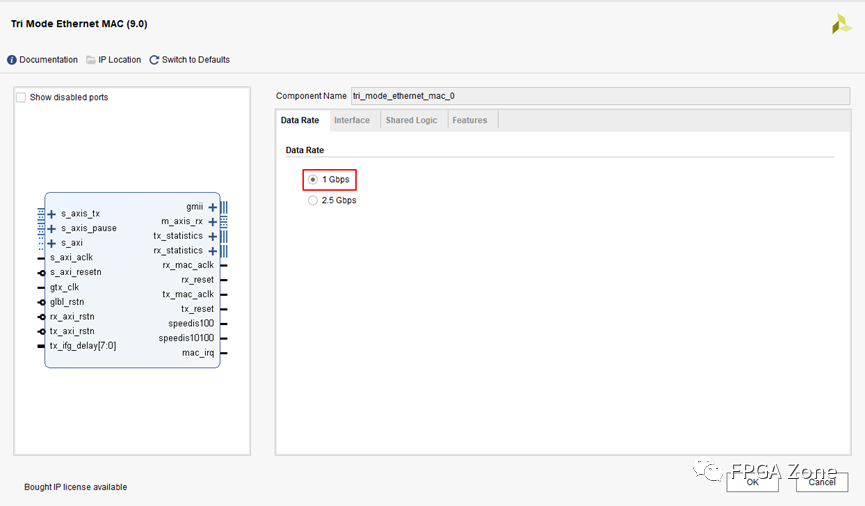

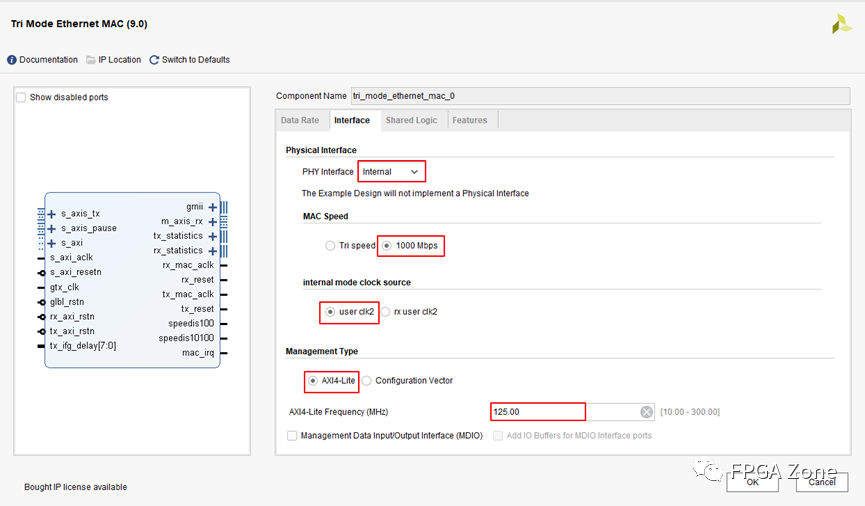

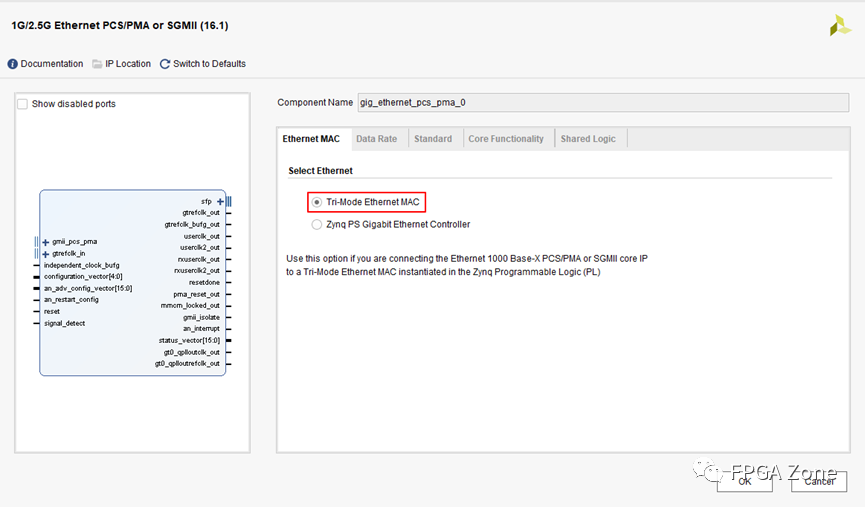

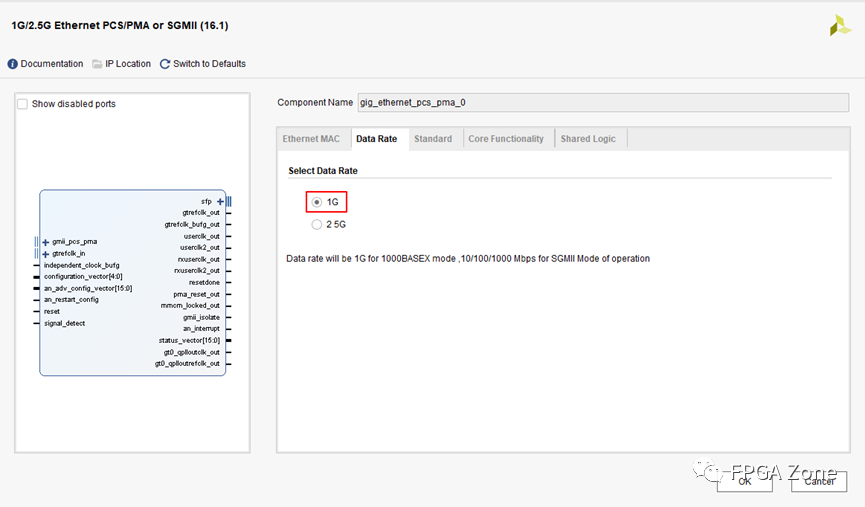

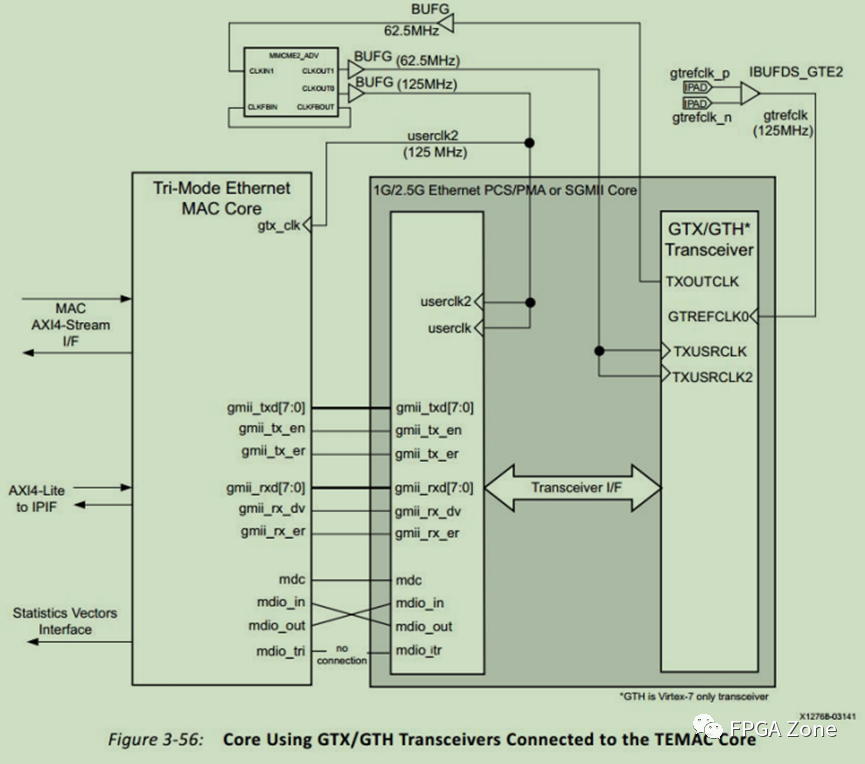

本工程主要是围绕“Tri Mode Ethernet MAC”IP核以及“1G/2.5G Ethernet PCS/PMA or SGMII”IP核建立。其中,“Tri Mode Ethernet MAC”IP作为以太网MAC,通过GMII接口与“1G/2.5G Ethernet PCS/PMA or SGMII”IP核进行核间通信。

软硬件平台

软件平台 :Vivado 2017.4;

硬件平台 :XC7Z035FFG676-2;

IP核参数配置

Tri Mode Ethernet MAC

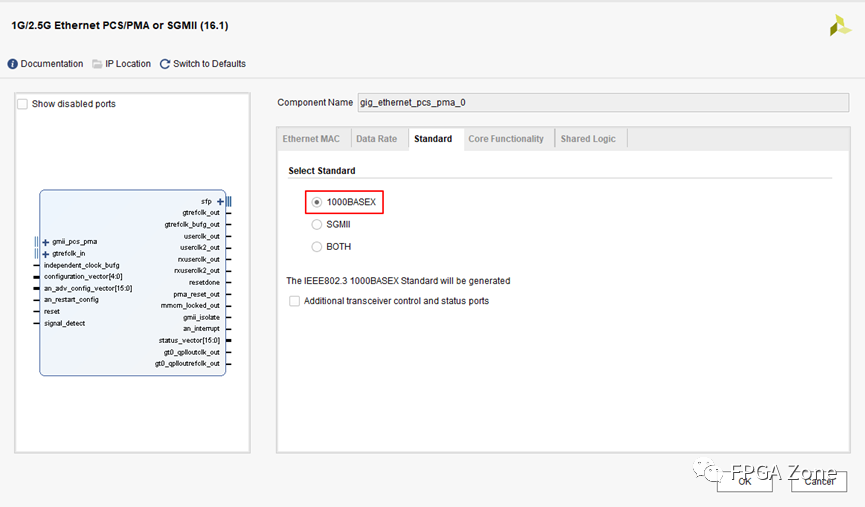

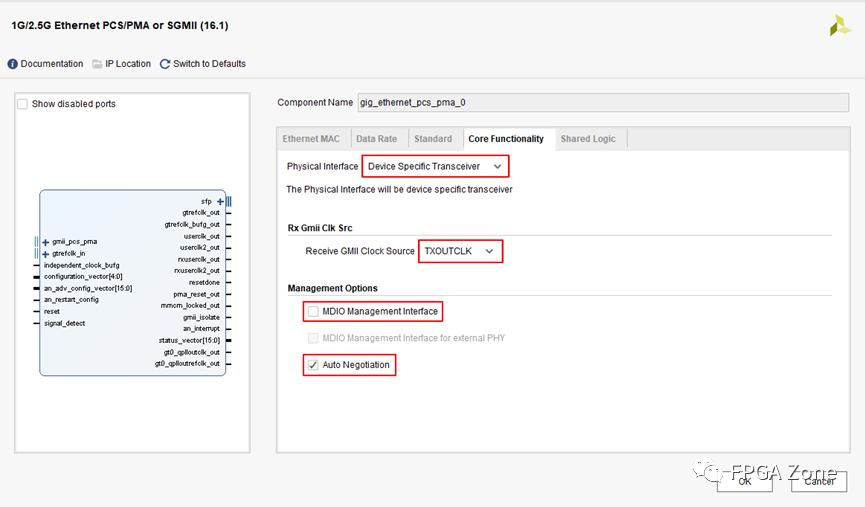

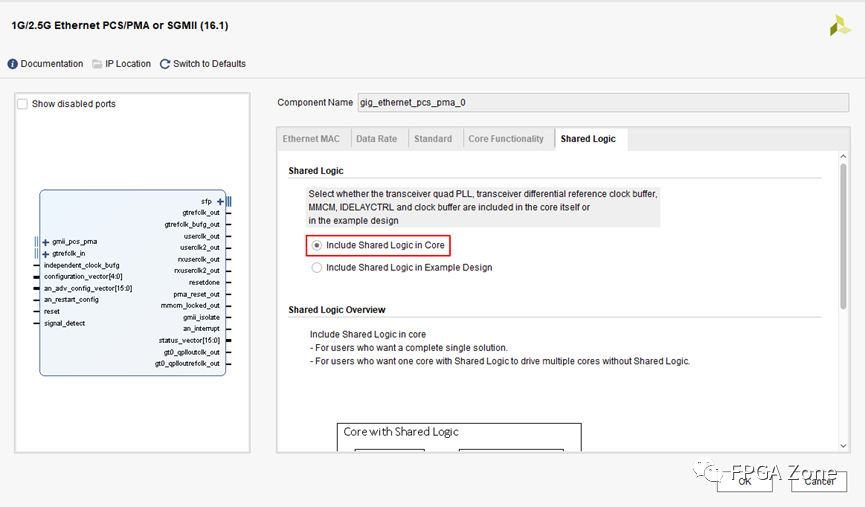

1G/2.5G Ethernet PCS/PMA or SGMII

接口互联

上述两个IP核之间通过GMII接口进行通信,Tri Mode Ethernet MAC工作时钟源采用1G/2.5G Ethernet PCS/PMA or SGMII输出的125Mhz的userclk2,GMII接口各信号与userclk2时钟同步。

功能测试

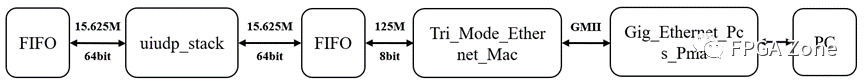

该Vivado工程实现的功能为千兆以太网光纤数据回环传输。在电脑端通过网络调试助手向FPGA板卡发送长度小于1472字节的数据包,FPGA收到数据后解析、缓存用户数据,最后回传给电脑端,数据传输方案如下图所示:

其中uiudp_stack数据位宽为64bits,而Tri Mode Ethernet MAC数据位宽为8bits,因此二者之间需要插入FIFO进行数据位宽以及时钟域转换。

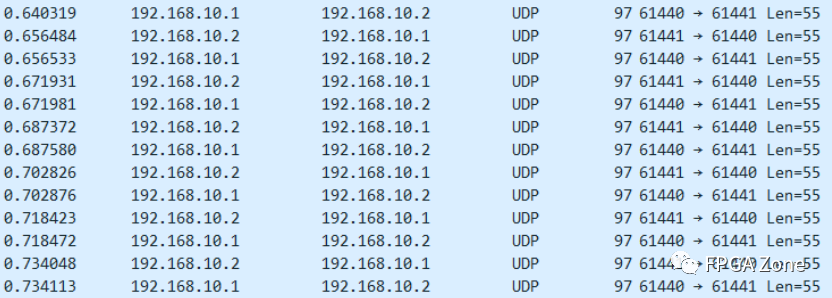

通过wireshark软件对电脑和FPGA之间传输的UDP数据包进行捕获,部分结果如下图所示:

全部0条评论

快来发表一下你的评论吧 !