1.FLASH器件特性

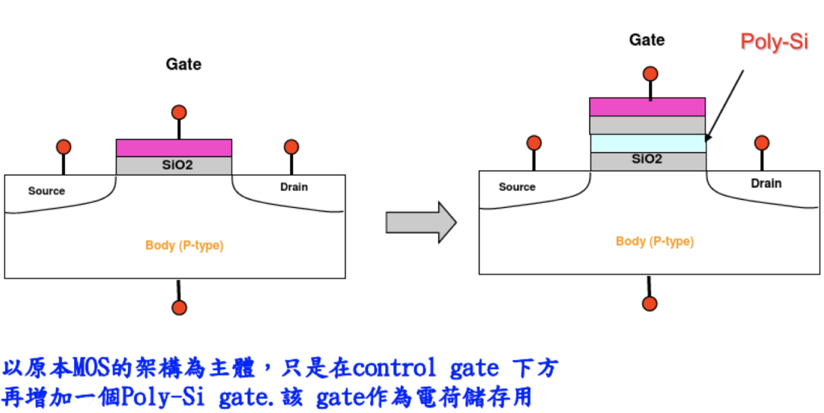

Flash 分为 NAND flash和 NOR flash。均是使用浮栅场效应管(FloatingGate FET) 作为基本存储单元来存储数据的,浮栅场效应管共有4个端电极,分别是源(Source)、漏(Drain)、控制栅(ControlGate)和浮栅(FloatingGate)。 Flash 器件与普通MOS管的主要区别在于浮栅,Flash 器件通过浮栅注入和释放电荷表征“0” 和 “1”。当向浮栅注入电荷后,读出 “0”;(Program(注入电荷))。当浮栅中没有电荷时,读出 “1”;(Erase(释放电荷) )

FLASH 器件栅极与硅衬底之间有二氧化硅绝缘层,用来保护浮置栅极中的电荷不会泄漏。采用这种结构,使得存储单元具有了电荷保持能力,就像是装进瓶子里的水,倒入水后水位就一直保持在那里,直到你再次倒入或倒出。通常用 DataRetention :数据保持力,衡量FLASH存储单元保存电荷的能力。

2. FLASH操作的电路原理-读

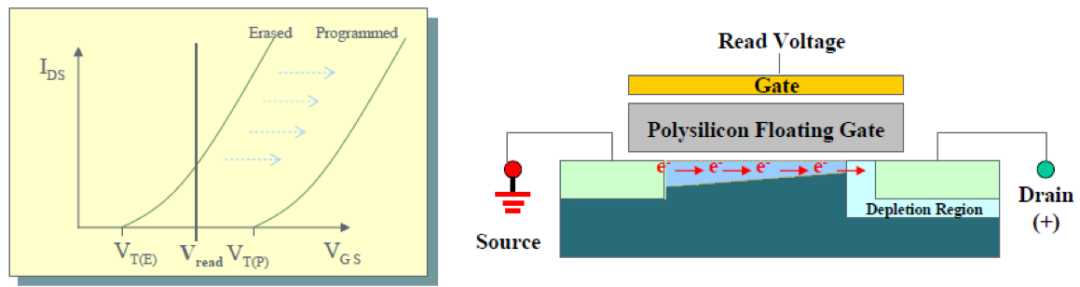

以 NOR FLASH 为例。通常 FLASH 会将 Vread 读参考电压设置在, Program (写)和 Erase(擦除)两种操作,对应的阈值电压 Vtp 和 Vte 之间。(否则会影响浮栅内电荷的稳定性)。

NOR FLASH 非门逻辑,Floating Gate 中有电荷时读出“0”,无电荷时读出“1”。一旦 FG 放置了电子,当在CG上施加正电压时,它部分取消了加在CG上电压带来的电场影响,这样晶体管导通需要在CG上放置更高的电压。即当浮栅门积累或存储的电子逐渐增多,门级阈值电压 VT 就会相应的升高,因为需要更高的电压克服浮栅内电子的影响才能使MOS导通。

假如在FG上没有电子时,CG上放置电压 Vt1 时导通,在FG上放置电子后,CG上需要放置电压Vt2导通,满足Vt2 > Vt1。为了读出cell的值,在CG上放置一个电压V(Vread),要求Vt1 < V 。<>

如果晶体管导通(代表数值1),即DS间能读到电流,那么FG上肯定没有电子,即逻辑“ 1 ”。

如果晶体管不导通(代表数值0) ,即DS间不能读到电流,那么FG上肯定放置有电子,即逻辑“ 0 ”。

3. FLASH操作的电路原理-写和擦

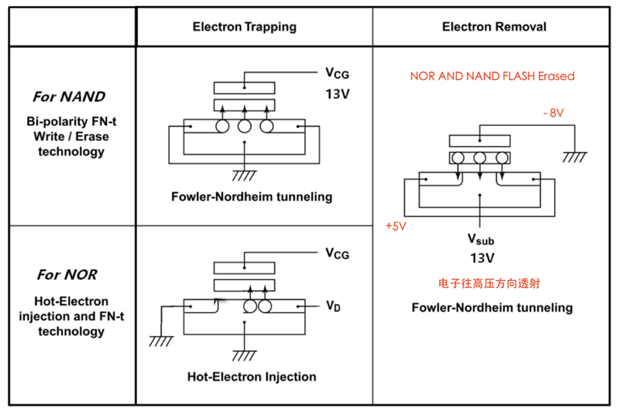

NAND型:擦和写均是基于隧道效应,电流穿过浮置栅极与硅基层之间的绝缘层,对浮置栅极进行充电(写数据)或放电(擦除数据)。

NOR型:擦除数据仍是基于隧道效应(电流从浮置栅极到硅基层),但在写入数据时则是采用热电子注入方式(电流从浮置栅极到源极,这种方法效率较低,因此 NOR FLASH写速率较低)。

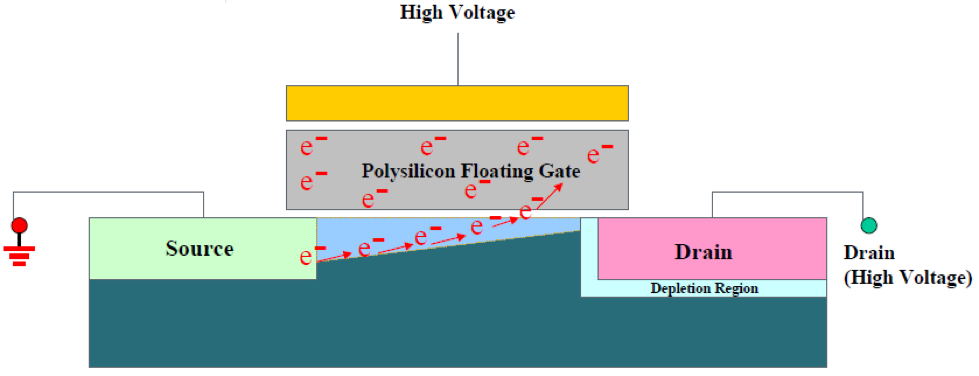

以 NOR FLASH 为例。写操作时,通常在门极施加高压( ~如10V ) ,同时漏源之间施加偏置电压 Vds,电子从源极向漏极流动。当Vds逐渐升高,电子也逐渐加速,变成热电子,和漏端的晶格碰撞后,一小部分被散射,穿过氧化物绝缘层(SiO2),最终被浮栅门吸收和保存。

当浮栅门积累的电子足够多,存储单元的状态就由 Erased(data=1) 变成 Programmed(data=0) 。外电场撤掉之后,电子被困在浮栅门,Programmed状态因而得以保持 。

同样 以 NOR FLASH 为例。擦操作时,要让FLASH的状态由 Programmed 变成 Erased, 需要执行写的逆操作,把浮栅门保存的电子排出来 。其中常用的做法是在门极施加较大的负压( ~ 如-8V ) ,同时在源极施加正电压( ~如5V ) ,这时在FN隧道效应 (FowlerNordheimTunneling) 的作用下,浮栅门里的电子能翻越氧化物绝缘层的势垒,返回到N型的源端。

4. FLASH 丢参的电学原理

我们有时候会发现一些 FLASH 出现存储单元丢参的情况,从FLASH 器件的特性和电路原理上看。假设给FLASH一个干扰,存储单元的内容,由 “1” 变 “0” 容易,还是 “0” 变 “1” 容易呢?

很明显, “0” 变 “1” 更加容易。因为 0 变 1 是擦除,擦除放电,电荷自己是会出现越来越少的情况,但一般不会越来越多,除非给一个强能量克服氧化物绝缘层的作用。即电荷是可以在外部干扰的作用下减少,减少到一定程度,存储单元的内容就从“0”变成了“1”。

这也是为啥空片的 FLASH 不用担心干扰问题,其电学原理是一致的,没写的cell(存储单元)是 “1” 状态也就是我们常见的全 FF ,写入的 cell 是program “0” 状态,干扰都是从 “0” 往 “1” 的方向干扰的,不可能把 “1” 干扰成program “0” 状态(电荷不会自己越来越多),因此空片的FLASH基本不用担心外部干扰问题。

常见的外部干扰有:供电电压波动不稳、外部强磁场、强辐射等能够导致电荷释放的场景。常见的电荷泄漏就是存储单元的电荷由于某种原因逐渐流失,最终导致位反转。

(1)电荷自然流失:速度非常慢,一般是每周或者每月流失个位数的电子(如SLCNAND的数据保存时间一般是10年(25C,<5000P/E cycles) )。

(2)外界温度:温度上升,电荷自然流失的速度会加快 。

(3)错误操作:反复擦写次数很高的情况下(例如:>10KP/E cycles)(反复擦写会导致绝缘层晶格受损,也会导致电荷流失速度加快)。

(4)外界电场/磁场干扰:电场改变导致电子加速流失。

5. FLASH 丢参的相关案例1

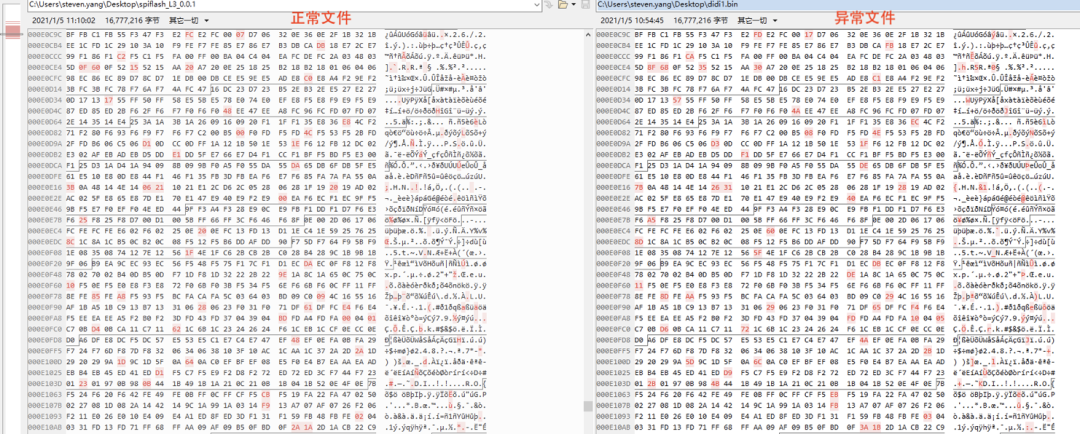

案例1:产品 A 灰测时,发现 电量较低时 产品不播语音问题。经过进一步分析,确认为FLASH音频文件被改写了,导致播放音频时获取文件失败,不播放语音。对FLASH文件进行回读后,对比如下:

对比烧录文件 和 FLASH 问题片子,发现 问题 FLASH 片每个 cell 里面每个 bit 随机出现 “0” 变 “1” 的情况,并且有大片数据不稳定的表现。存储扇区部分字节由 “0” 异变到 “1” ,在很多情况下如电子的自然流失是有一定概率出现的,但是大片出现异变,很明显受到外部因素的影响,最常见的为供电电压波动带来的电场干扰。

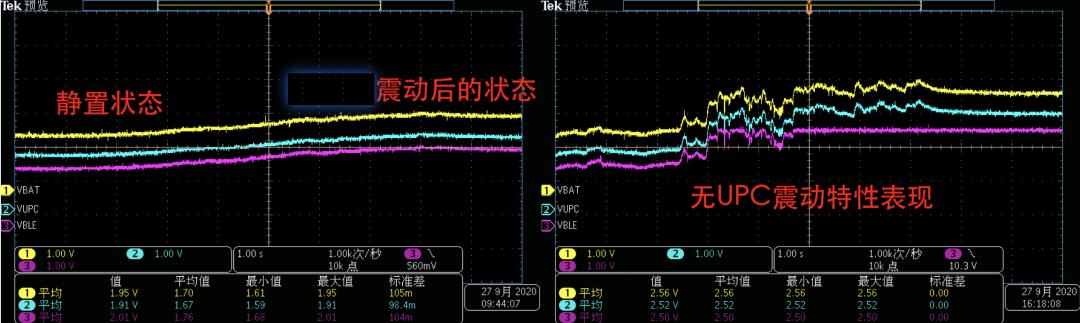

进一步排查供电电源不稳的原因,确认确实会出现该问题,我们使用一次性干电池(锂-亚硫酰氯)。其发生低电时,震动电池,会使得电池内部残余的电解液在外力作用下震荡到炭包内部,提供短时间的电化学反应可能,但是毕竟被吸附的很少,当这部分电解液也被消耗之后,电池马上恢复至无电状态。

即出现低电时电池的电压低于 FLASH 最低供电电压2.7V(2.7-3.6V),但系统(BLE)还能正常工作,FLASH掉电不完全。震动电池时电压又瞬间恢复到3.0V以上,FLASH未掉电完全后上电。这样的供电环境下压测操作FLASH,容易复现问题。

6. FLASH 丢参的相关案例2

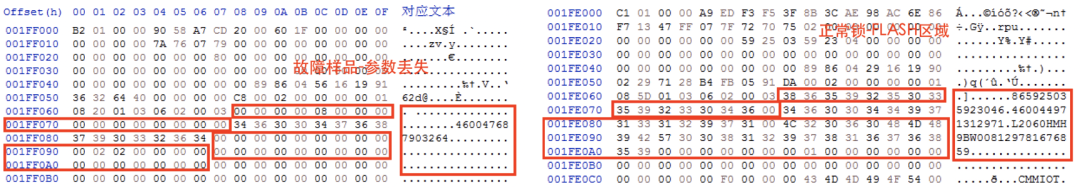

案例2:产品路测时发现核心参数区参数丢失,但自己写入的参数都正常的问题,确认参数丢失区都是 “1” 异变到 “0”。

为 “0”表示自己主动写过,且浮栅内有电子,根据前面的分析可知电子自己不会越来越多。FLASH写 “0” 时需要给 浮栅场效应管 提供较大能量,使电子加速穿过氧化物绝缘层(SiO2),进入浮栅门,并被困住。因此此种情况基本排除是由于硬件的外部干扰导致发生 “1” 变 “0”。后期排查软件,确认是野指针导致参数存储区发生踩踏行为。

7. 结语

我们可以通过FLASH器件的特性来分析 FLASH cell 内容出现丢失问题的原因,同时确认外部工作环境的影响用于指导设计。

审核编辑:汤梓红

全部0条评论

快来发表一下你的评论吧 !