电子说

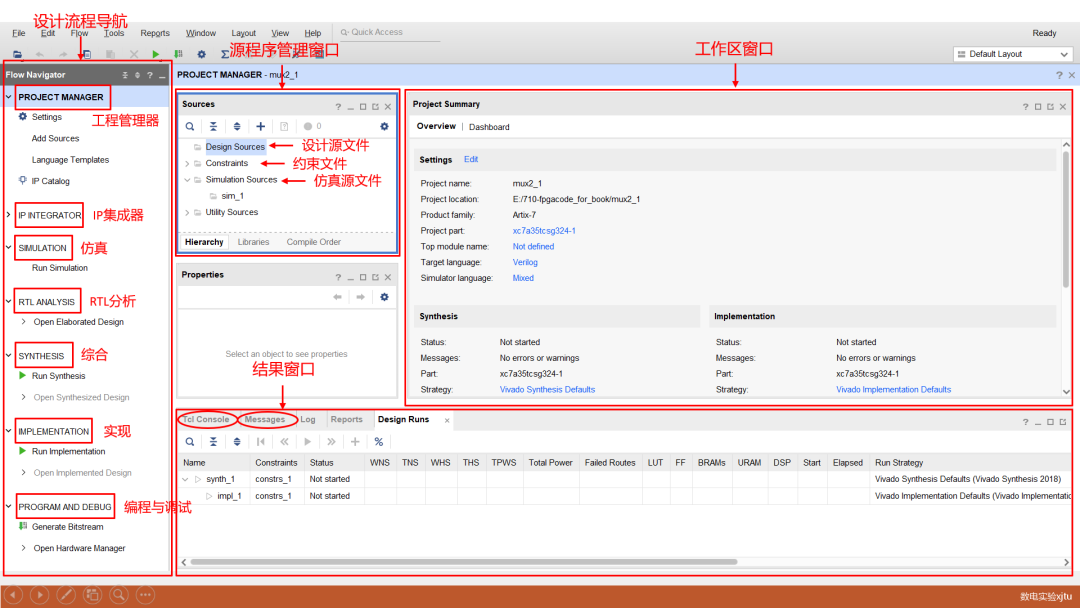

Vivado设计主界面,它的左边是设计流程导航窗口,是按照FPGA的设计流程设置的,只要按照导航窗口一项一项往下进行,就会完成从设计输入到最后下载到开发板上的整个设计流程。

源程序管理窗口包含了一个设计中最基本的三种文件,设计源文件,约束文件,仿真源文件,如果添加了IP核,这里还会有IP源文件。

工作区窗口会显示工程相关的基本信息,以及我们对系统进行的详细设计都在这个窗口完成,例如设计代码的输入,查看综合实现结果、创建Block Design等。

运行每一个步骤之后,会在结果窗口中的Message窗口显示设计相关的所有信息,包括错误(error)和警告(warning)提示都会显示在Message下面。

基于Vivado开发环境的设计流程

1.设计输入

在Vivado中可以使用硬件描述语言描述电路,也可以通过IP集成器创建图形化工程。

在设计流程导航窗口(Flew Navigator)中,“Settings”可以进行vivado工具使用相关的常用设置,"Add Sources"可以添加或创建设计文件。"Language Templates"是语言模板,提供了一些硬件描述语言的常用设计的写法。“IP Catalog”可以打开IP目录,里面包含了Xilinx提供的IP核以及用户自己设计的IP核等。

IP集成器(IP INTEGRATOR)可以创建一个Block Design,可以将IP核,或HDL module以图形化的方式添加到图形化界面中,再通过端口的互联,像搭积木一样完成一些复杂的设计。

2.仿真(Simulation)

设计输入完成之后,需要进行仿真,这里可以进行功能仿真,也可以进行时序仿真,时序仿真就是考虑了走线时延及器件延迟的仿真。

3.RTL分析

RTL(寄存器传输级)分析会生成RTL原理图,可以对设计进行逻辑和功能检查。因为使用HDL描述设计时可能出现语法或逻辑上的错误,一般语法错误Vivado会自动检测和提示,而逻辑错误软件没有明显提示,可以使用RTL分析进行检查。

4.综合(Synthesis)

综合是将较高层次的逻辑设计代码或原理图等设计输入转化为较低层次的由FPGA芯片中底层基本单元表示的电路网表。

5实现(Implementation)

综合之后要进行实现,实现是将综合后的电路网表针对具体指定器件以及相关物理与性能约束进行优化、布局、布线的过程。

因此,在实现前还要添加约束文件,将设计的端口对应到具体的FPGA引脚上,还要根据板卡指定引脚供电电压等,此外,还要针对性能要求进行相关时序约束,保证时序收敛,作为FPGA入门,我们暂不考虑时序约束。

6.编程与调试(Program and Debug)

在这一步可以生成可配置文件,也就是将实现产生的网表文件转化为可下载到FPGA中的比特流文件,完成对FPGA的配置。

源程序管理窗口

源程序管理窗口包含了一个设计中最基本的三种文件,设计源文件,约束文件,仿真源文件,如果添加了IP核,这里还会有IP源文件。

工作区窗口

工作区窗口会显示工程相关的基本信息,以及我们对系统进行的详细设计都在这个窗口完成,例如设计代码的输入,查看综合实现结果、创建Block Design等。

结果窗口

Tcl console可以使用Tcl命令完成Vivado所有的操作。

Message会显示设计相关的所有信息,包括错误(error)和警告(warning)提示都会显示在message下面,其它的窗口目前阶段我们不常用,就不多做介绍了。

全部0条评论

快来发表一下你的评论吧 !