电子说

0****1

时序逻辑电路设计方法

时序逻辑电路的特点是输出信号不仅与电路的输入有关,还与电路原来的状态有关。

因此,电路需要具有记忆功能的存储电路。FPGA中基本的存储单元是D触发器,也是实现时序逻辑的基本单元。

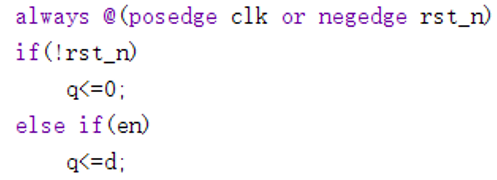

那么,什么样的语句会被综合成触发器呢?在Verilog中,常使用always进程块描述时序逻辑。此时,always进程块中的敏感列表一般为时钟边沿和异步控制信号,

** always ** @(posedge clk,posedge rst)

always进程块的执行是在时钟边沿触发下进行的。

时序逻辑电路按状态变化的特点,可以分为同步时序逻辑电路和异步时序逻辑电路。

同步时序逻辑电路的各个触发器状态的转换在同一时钟脉冲作用下完成。目前,大多数数字电路都是同步时序电路。我们实验中所涉及到的也都是同步时序电路。

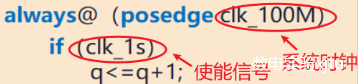

在设计时需要注意,所有always敏感列表中第一项敏感信号应该为同一时钟信号,比如,都为系统时钟clk的上升沿。

不出现其他派生信号,比如,系统时钟产生的分频信号等等。

异步时序逻辑电路中,没有统一时钟,各触发器状态转换是异步完成的。

在always进程块描述时序逻辑时,赋值语句使用非阻塞赋值,即“<=”。

0****2

时序逻辑电路设计实例

下面来看几个D触发器的设计实例,来理解Verilog语句与电路之间的关系。

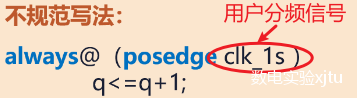

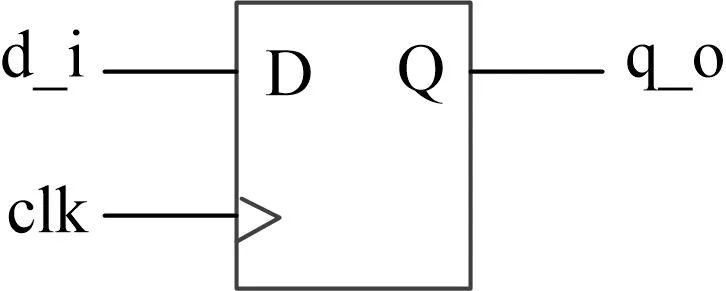

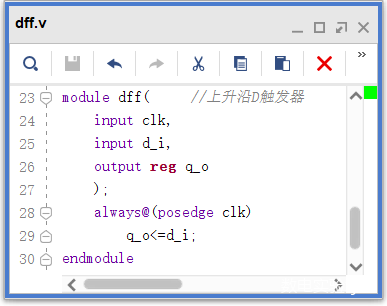

实例1:基本D触发器

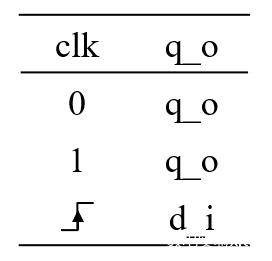

设计一个简单的D触发器,在时钟上升沿触发下,输出等于输入,其他时间输出保持不变。

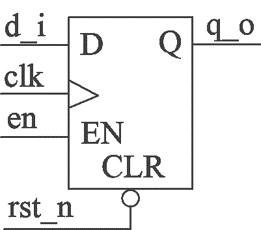

使用always语句进行描述,敏感列表为时钟上升沿。当时钟信号由0变为1时,执行always语句“q_o=d_i”,如下图所示。

我们看到输入信号d_i不出现在敏感信号列表中,也就表明,输入的变化不会引发输出立即变化,只有在时钟上升沿时才被采样。

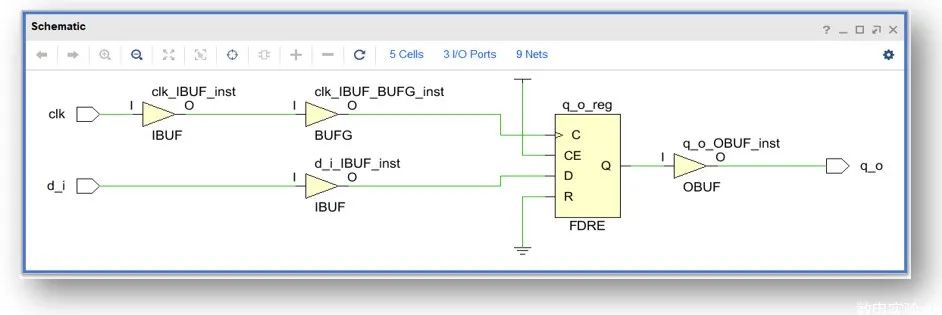

下面是综合后的原理图,综合就是将Verilog设计对应到FPGA内部组成单元上。

我们看到,综合出的是D触发器(FDRE为D触发器,参见赛灵思官方文档ug799),其中敏感列表中的clk被综合为触发器的时钟信号C,d_i连接D触发器输入端D。D触发器还包含信号CE(时钟使能端),以及R(复位端,高有效),在本示例中均未用到。因此,将CE连接高电平,使时钟始终有效,R连接低电平,使复位无效。

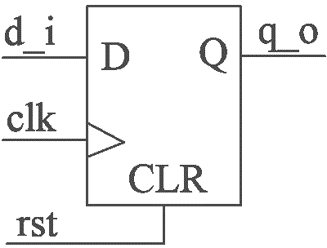

实例2:带复位(高有效)的D触发器

下面的例子加入了复位信号。复位分为同步复位和异步复位。

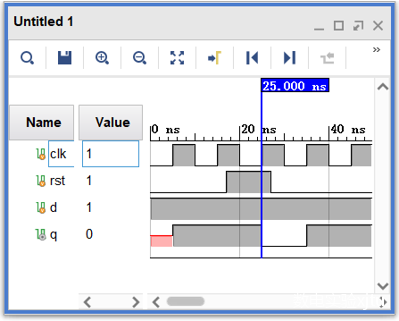

同步复位中,当复位信号有效时,必须要等到时钟上升沿到来时,才能执行复位信号相关的行为语句,如仿真波形图中所示。

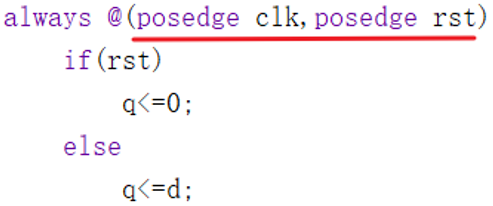

异步复位中的复位信号与时钟没有关系,只要复位信号有效,就立即执行复位相关的逻辑行为。要实现异步复位,复位信号要放在敏感列表中。

仿真波形图中可以看到,当rst有效时,输出立即被复位,下一个clk上升沿到来时,此时,rst信号仍然有效,因此,输出为0。再一个clk到来时,复位无效,则输出等于输入。

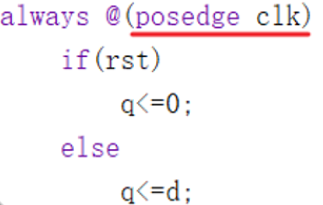

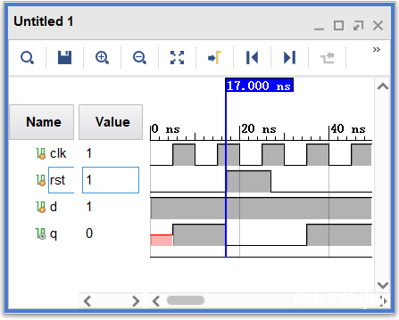

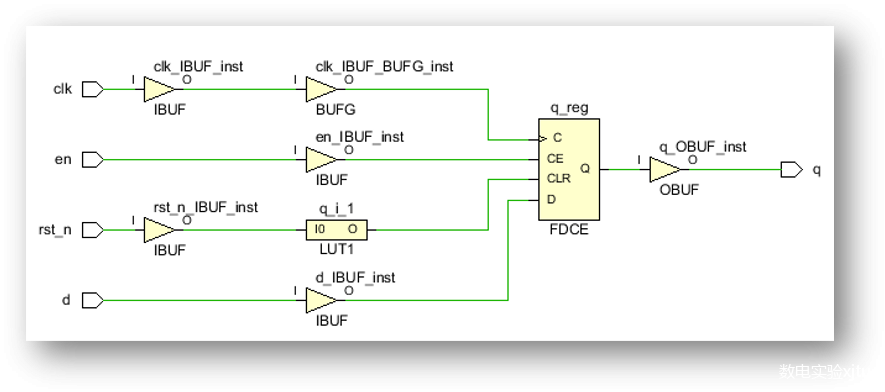

实例3:含异步复位(低有效)和同步使能的D触发器

下面是一个带有同步使能信号的D触发器。

这里我们使用了低电平复位,当复位信号无效,使能信号有效时,在时钟上升沿触发下,输出等于输入。

在综合后的原理图中,en使能信号连接在了D触发器的CE端。复位信号rst_n与CLK的连接经过一个LUT(LUT是FPGA用于实现组合逻辑的基本单元查找表),在Vivado中可以看到该LUT的真值表,它实现的是反相器的功能,这也说明了赛灵思的FPGA中触发器的复位引脚是高有效的,如果你设计中复位是低有效,这里就会多出一个反相器将其逻辑取反。

03

always进程块用法总结

always进程块是最常用的行为描述语句,他可以描述组合逻辑也可以描述时序逻辑。

描述组合逻辑时,敏感列表中为输入电平信号,而描述时序逻辑时,敏感列表为时钟边沿及异步控制信号。Vivado综合工具会根据always后面的敏感列表的不同形式综合出相应的电路。

always在仿真中还可以通过延时控制来产生激励信号。例如,always #5 clk=~clk,表示当执行到该语句时,需要延迟5个时间单位的时间(由`timescales 定义),然后再执行“clk=~clk”。

全部0条评论

快来发表一下你的评论吧 !