电子说

峰值保持电路是用于捕捉变化的输入信号的峰值,是利用记录仪记录峰值的关键电路,其有各种电路结构,分析也相对简单。

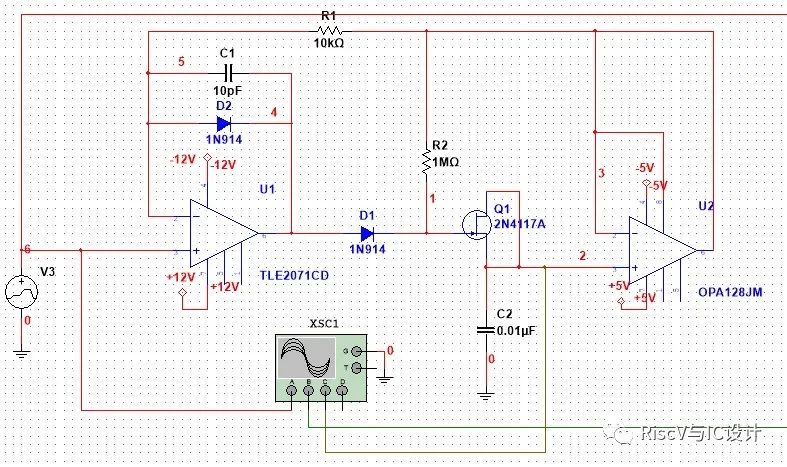

电路设计最简单的就是功能设计,比如设计峰值保持器,最头疼的就是设计时要求电路满足一定的指标,比如要求峰值保持器满足2mv的跟踪精度、能对4Mhz的波形进行跟踪,一下子问题就复杂了,在不讲指标要求的情况下,谈电路设计是毫无意义的,这里介绍两种经典实现:一种是TI公司的参考设计,采用高速运放;另一种是采用高速比较器的实现方式。

1)采用高速运放

2)采用高速比较器

此电路更加简洁,工作速度更快,可以跟踪MHz以上的信号,是非常实用的电路

全部0条评论

快来发表一下你的评论吧 !