电子说

01

输入输出范围

轨到轨运放,想必大家都不陌生。

供电电源轨

Power rail

什么是供电电源轨?

运放供电电压,决定运放处理信号的范围。

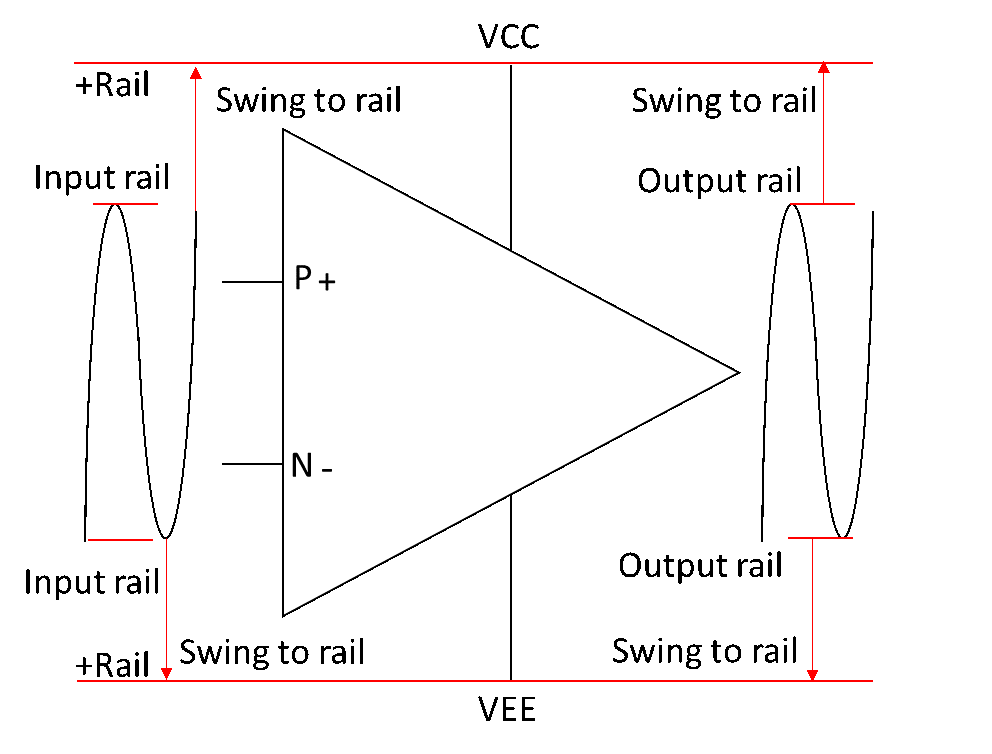

轨到轨指的是,运放输入输出范围,可以摆到电源轨。

如下图所示:

为什么会有非轨到轨特性?

输入:差分基本放大电路,MOS/BJT在输入电压(共模)较大时,进入非线性区,导致非轨到轨现象产生。

输出:甲乙类功率放大电路,BJT的饱和电压、二极管的Forward压降,导致此现象产生。

非轨到轨特性对电源设计的影响?

在下最早接触电力电子设计时,碰到过这种情况。选用某非轨到轨运放,输入正弦波,输出突然被削顶。

而后突然惊觉。竟选用非轨到轨运放。难怪如此。说起来抽象,直接上图:

结论1:

结论:在现今CMOS电平横行年代,轨到轨特性尤为重要!

02

频率特性(速度)

1

带宽增益积

GBW: Gain bandwidth product

什么是GBW?

运放开环带宽为1时的频率,亦称为单位增益带宽。

啰嗦一句,这里工程师,经常把GBW误称为带宽。真实的两个概念,运放一般给出带宽增益积的指标。

GBW对电源采样电路有哪些影响?

仍以差分放大电路为例。不考虑误差时,增益为R2/R1,某次应用中,你突然发现,放大100kHz信号,为何增益小于R2/R1?

这时你要问自己,设计电路时,考虑GBW了吗?

以某运放为例:

GBW=1MHz,AOL=100kHz=20dB(10倍)。

以闭环系统思路分析:

你的期望是: 100kHz信号能完整放大10倍(理论上R2/R1=10)

实际情况是: 增益G=5,因为开环增益不够的缘故。

结论2

GBW越大,一般某频率处,开环增益越大,理论增益和实际增益差距越小。

2

压摆率

SR: Slew rate

什么是SR?

运放输出电压的转换速率。

通常单位为V/us

SR怎样考量?

如果,某信号需要快速保护,摆率会影响这个信号的延迟。

结论3

快速运放摆率大,适合做快速保护。

03

精度

1

输入失调电压Vos

Offset voltage

什么是输入失调电压Vos?

简单解释:为了使输出电压为零,在输入端施加的差分电压。

为什么会有输入失调电压Vos?

运放输入级,BJT/CMOS组成的差分放大电路,理论上完全对称。

然而,受工艺所限,不匹配的输入级,导致了输入失调电压。

Vos对电源的影响?

以差分放大电路为例:

理论增益为:

考虑失调电压后增益为:

多大影响,一算便知~

结论4

输入失调电压会影响精密度,对于精确度较高的应用,选取失调电压小的运放。

2

输入偏置电流

Bias current

什么是输入偏置电流Ibias?

运放输入端P/N输入电流之和。

为什么存在输入偏置电流Ibias?

运放输入是差分放大电路,那想让它工作,得给人静态工作点吧。

输入偏置电流,便由输入级直流工作点引入。

Ibias对电源采样调理电路的影响?

仍以差分放大电路分析:

考虑偏置电流,放大倍数为:

因此,理论上,只要电阻参数完全相等,输入偏置电流对差分放大电路,没有任何影响。

但其他运放典型应用呢?以反相比例放大电路(R*=0)为例:

考虑偏置电流,放大倍数为:

结论5

输入偏置电流可以通过差分、添加补偿电阻去除。

04

抗扰度

1

共模抑制比

CMRR: Common mode rejection ratio

什么是共模抑制比CMRR?

差分信号放大倍数/共模信号放大倍数

也许一般人不重视这个参数,但是,当你的调理电路,被开关噪声,干扰的一塌糊涂,你就懂这个痛了。

结论6

越大的CMRR,对抑制开关噪声(共模干扰),越有效果。

2

电源抑制比

PSRR: Power supply rejection ration

什么是电源抑制比PSRR?

电源信号/对应的输出电压。

也许还有人,也不重视这个参数,但是当你发现,输出叠加辅助电源的开关次信号,你就懂了。

在下当年调电路时,发现运放输出,总是叠加一个很小的纹波,和辅电开关频率一致,我陷入了沉思…

结论7

PSRR越大,辅电对运放输出影响越小。

全部0条评论

快来发表一下你的评论吧 !