昨天群友在群里问了一个关于运算放大器轨到轨输出的问题,对此我写一下我对此的理解,以及结合仿真,梳理给各位同好。

理论

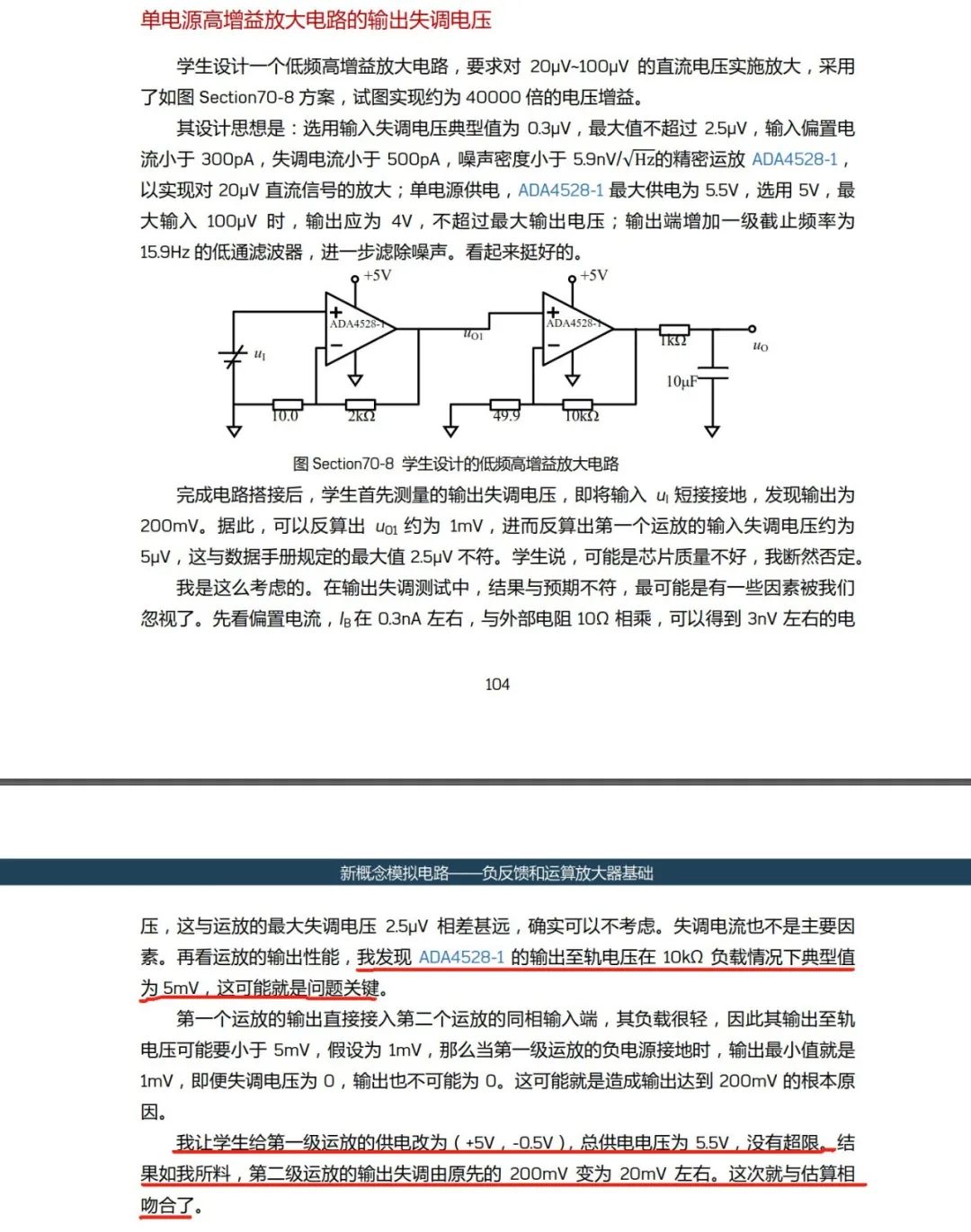

问题的起因是杨建国老师的新概念模拟电路里的一个关于小信号放大的案例,大概就是输出的电压和预想偏差了很多,大家可以先看一下下面的节选。

群友的疑问:为什么运放的V-由GND(0V)改为-0.5V就输出正常了?

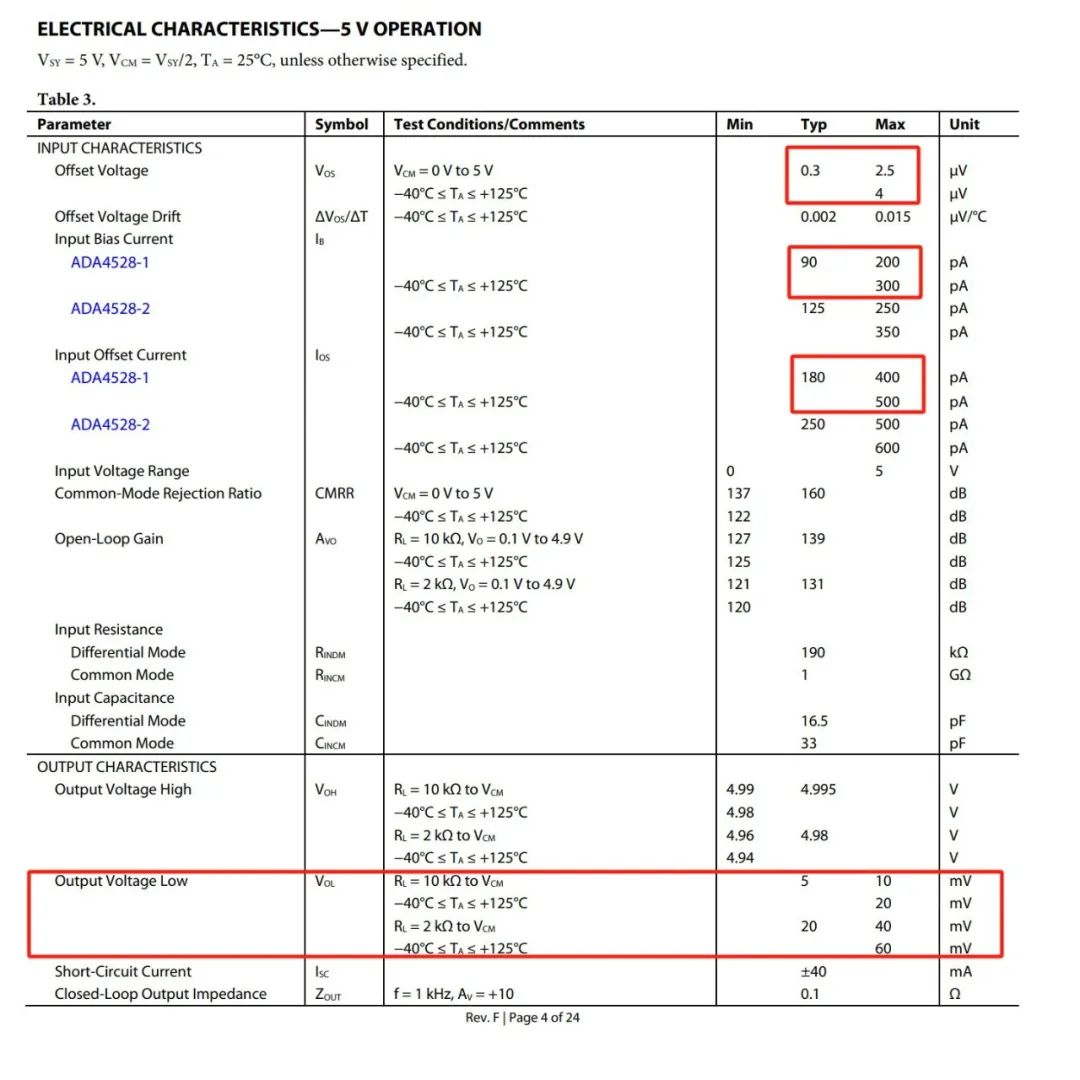

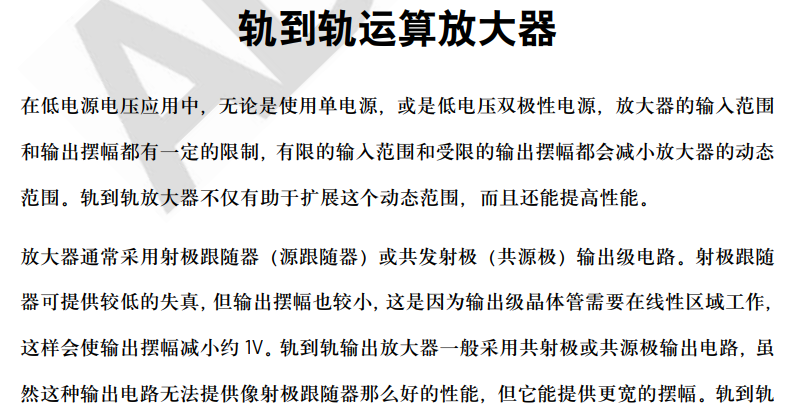

回答:这个和运算放大器的轨到轨输出有关系(比如0 ~ 5V供电,那么输出几乎等于0~5V范围就算是轨到轨),虽然有的运算放大器说是轨到轨输出,但是实际上,由于其内部结构原因,并不能完全轨到轨;就像杨老师举的例子一样,这个实际上第一级的运放是没有输出到0V的(如果暂且不考虑失调电压电流等参数是要输出0V)。就如手册里写的,

在Rl = 10KΩ to

Vcm的时候,0-5V供电的这个运放的输出最小电压为5mV(典型值)。这个不能完全轨到轨输出也就导致了第二级运算放大器放大了这个最小输出电压,从而导致了偏差。

群友问:如果仍然是0V-5V供电,如果在同相输入端或者反相输入端叠加一个人为的偏置,能否抵消掉这个?能不能输出到0V?

回答:不能,因为这个轨到轨输出的最小或最大电压是由运算放大器内部的结构,以及运算放大器的负载电流,并且和供电电压直接相关的。无论在同相输入端或者反相输入端增加人为的偏置补偿均不能抵消掉。就像杨老师书里写的例子一样,如果想要让他输出0V(不考虑失调电压等参数),那么只能加负压才能让他输出0V。

这一点可以理解为类似PMOS和NMOS的DS之间总会因为Rdson的存在而有一些压降一样,而且这个压降会随着流过DS的电流的增加而增加(I*Rdson)。

对此在ADI的设计文档里也找到了对轨到轨输出的相关描述,大家可以参照阅读一下:

仿真验证

那么我们就也仿真一下,去深入理解一下这个杨老师书里的问题吧。

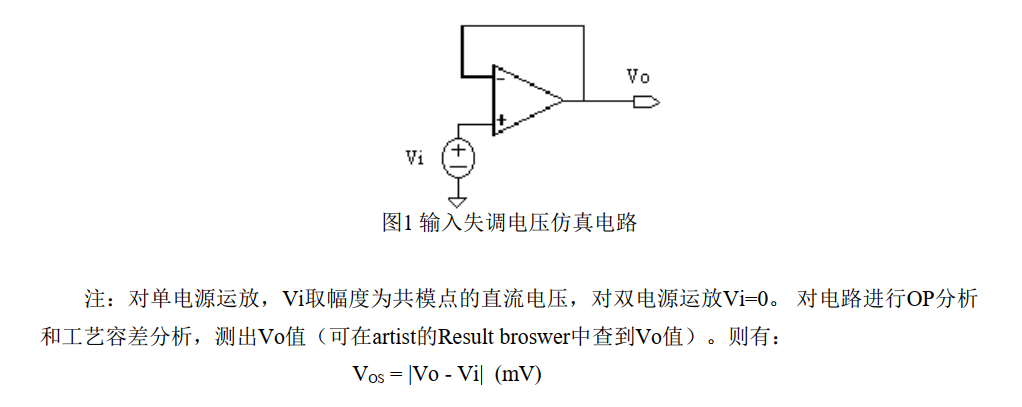

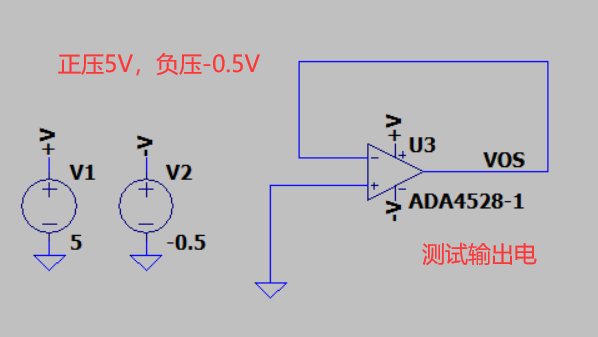

首先,我们在仿真里测试一下ADA4528的输入失调电压Vos,就按照上图文档,我们使用双电源供电。测试出来的Vos大致为465nV,在手册写的0.3~2.5uV范围内。

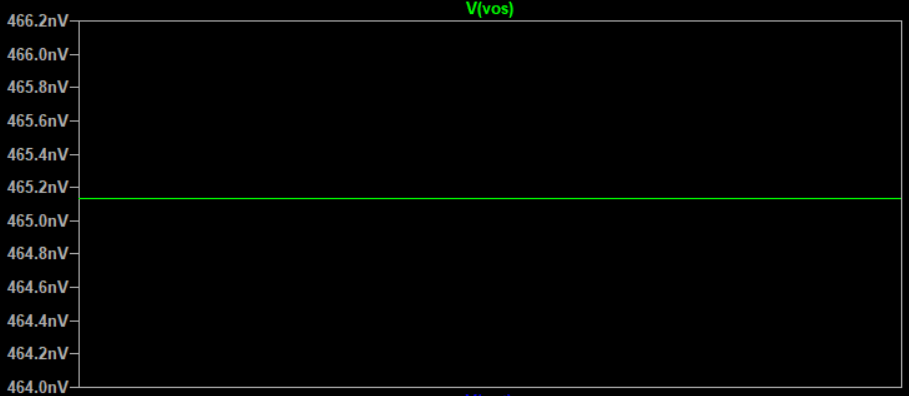

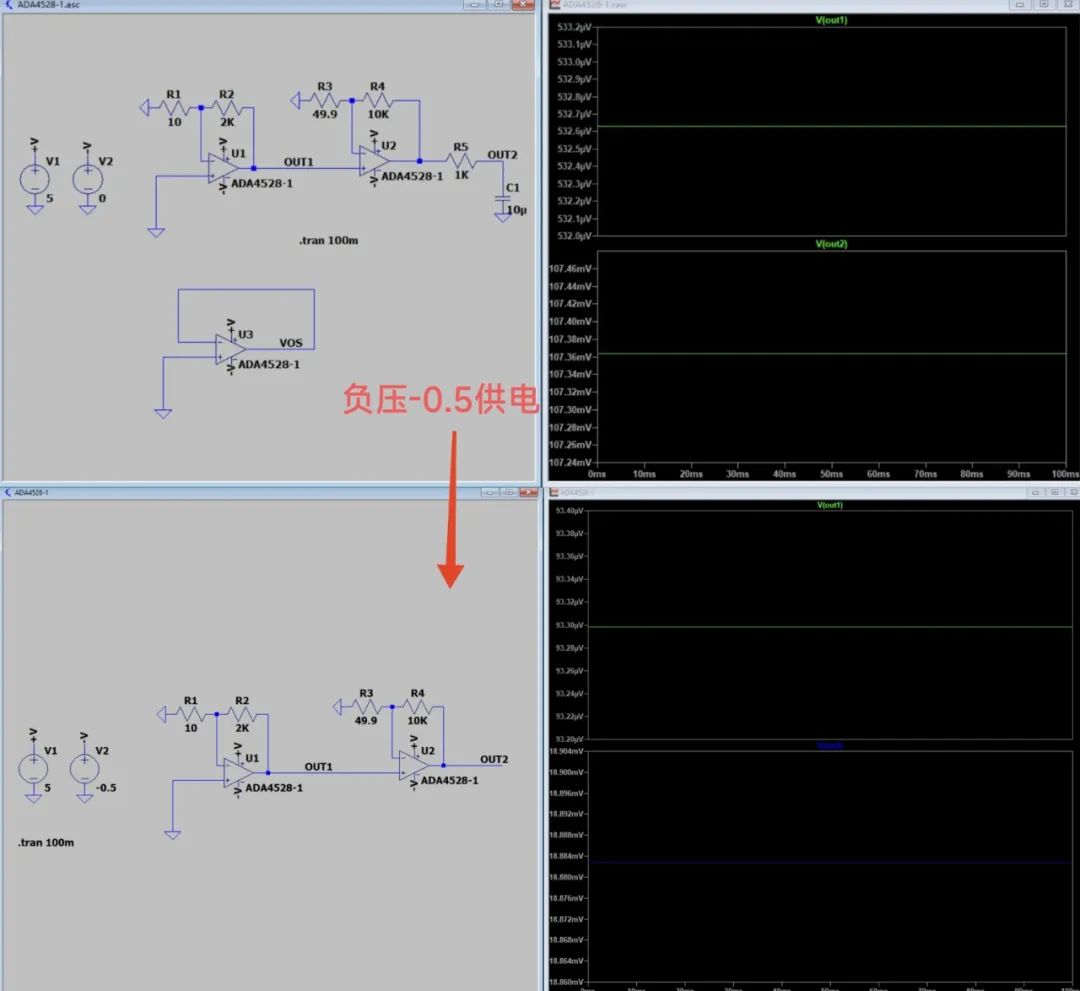

然后我们搭出来杨老师的书里的电路,首先用0V-5V供电,第一级输出电压为532uV(与200Vos偏差很远),第二级再放大后(放大倍数约为200)的电压为107mV左右(200532uV)

然后我们把0V改为-0.5V,神奇的事情发生了,真如书里所说一样,发生了变化。第一级输出电压变为了93uV左右,第二级输出电压为19mV左右。这第一级的输出基本就符合200*Vos了:

200*0.465(Vos)=93uV

最后说两句

在工程应用的时候,一定要注意这个轨到轨输出的问题,尤其是小信号放大,必要时加负压,仔细看规格书,特别是应用一些非轨到轨的运放(例如LM358之类的),更要小心小心再小心。

全部0条评论

快来发表一下你的评论吧 !