FF_DRE是一个具有异步设置(SET)和重置(RST)输入的边缘触发的D触发器(D Flip-Flop)

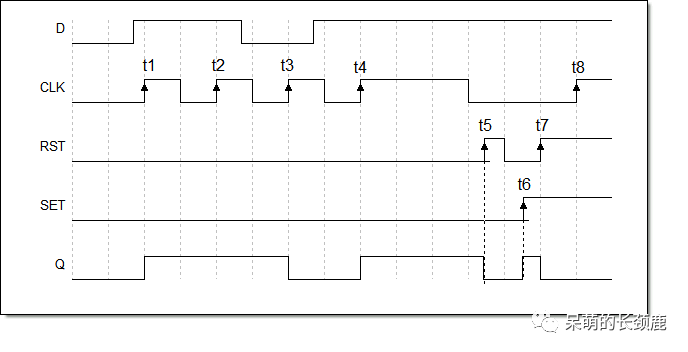

在任意时刻,当SET或RST为TRUE时会忽略CLK信号而设置或重置Q信号,RST比SET具有优先权,即RST和SET同为TRUE时,Q被重置为0。

时间图如下:

其中: CLK:时钟, RST:重置, SET: 设置 , D:输入 , Q:输出

源代码如下:

FUNCTION_BLOCK "FF_DRE"

TITLE = 'FF_DRE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

SET : Bool;

D : Bool;

CLK : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST OR #SET THEN

#Q := NOT #RST;

ELSIF #CLK AND NOT #edge THEN

#Q := #D;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

全部0条评论

快来发表一下你的评论吧 !