可编程逻辑

可编程AES加解密IP

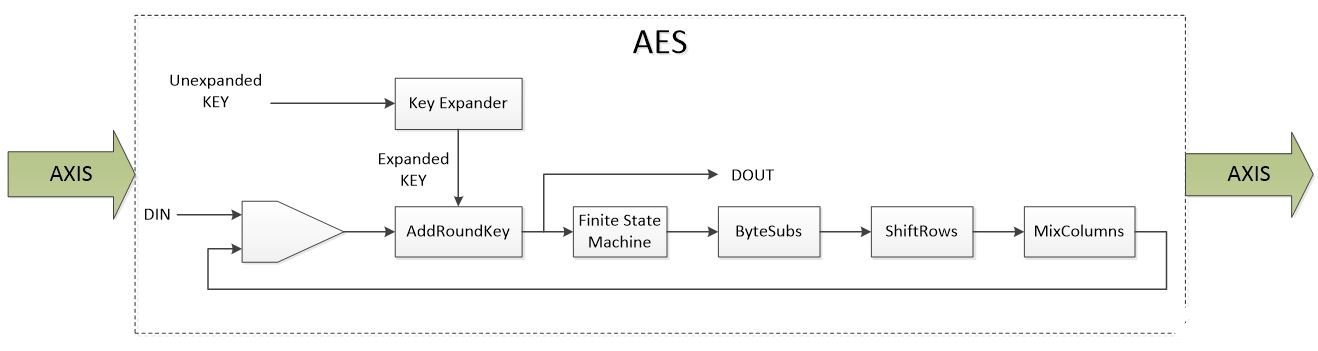

可编程AES加解密IP提供了加解密算法功能,兼容美国国家标准与技术研究院(NIST)发布的高级加密标准(AES):FIPS PUB 197。结合FIPS 197分组加密算法,可编程AES加解密IP具备5种加密模式:ECB,CBC,CFB,OFB,CTR,全部支持加密和解密功能,兼容美国国家标准与技术研究院(NIST)发布的推荐分组加密操作模式:NIST Special Publication 800-38A。可编程AES加解密IP内建密钥扩展功能,使用初始密钥产生扩展密钥,用于加解密过程。可编程AES加解密IP处理128-bit分组数据,并且支持可编程的密钥长度:128-bit,192-bit和256-bit。

内核特性:

1. 使用AES Rijndael分组加密算法进行加解密

2. 兼容联邦信息处理标准FIPS Publication 197

3. 兼容推荐分组加密操作模式:NIST Special Publication 800-38A

4. 用户可编程密钥长度:128-bit,192-bit和256-bit

5. 用户可编程加密模式:ECB,CBC,OFB,CFB和CTR

6. 内置密钥扩展

7. 128-bit高速数据通路;对于128/192/256-bit加密密钥,内核分别需要11/13/15个时钟周期来处理128-bit分组

8. 易于集成的同步,可综合Verilog设计

9. 通过完全验证的AES IP

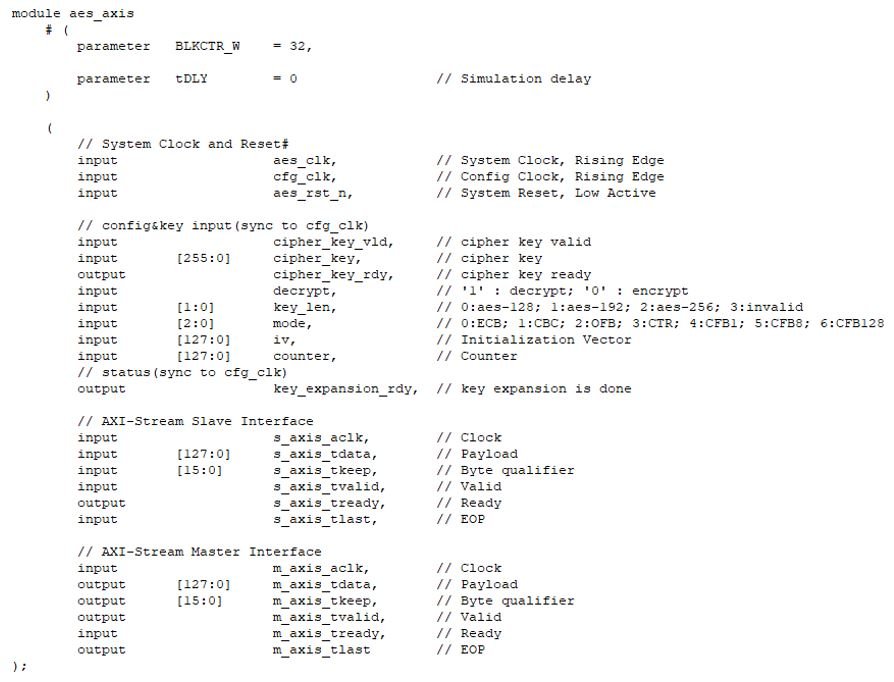

对外接口:

1. 标准的AXI4-Stream数据总线

2. 方便的AXI4-Stream类似的接口,用于配置密钥、模式和参数

性能指标:

1. 加解密吞吐率大于3Gbps@250MHz内核时钟

资源使用(XCKU115为例):

1. LUTs:5532,FFs:2535

审核编辑:黄飞

全部0条评论

快来发表一下你的评论吧 !