低压降线性稳压器(LDO)因其工作原理,虽然能以低成本提供高电源质量,但也会不可避免地产生损耗和发热问题。面对大压降、大电流,LDO将长时间处于较高的工作温度范围,可能影响其使用寿命和可靠性。因此,通过事先分析和评估LDO在特定工作环境下的温度,并采取一定的措施,可以有效地避免芯片在长时间的高温下发生热关断和老化。

芯片的结温主要取决于其功耗、散热条件和环境温度。因此,通过选择不同的封装版本来降低芯片的结与环境的热阻,是一种降低结温的有效解决方案。

1

芯片热阻介绍

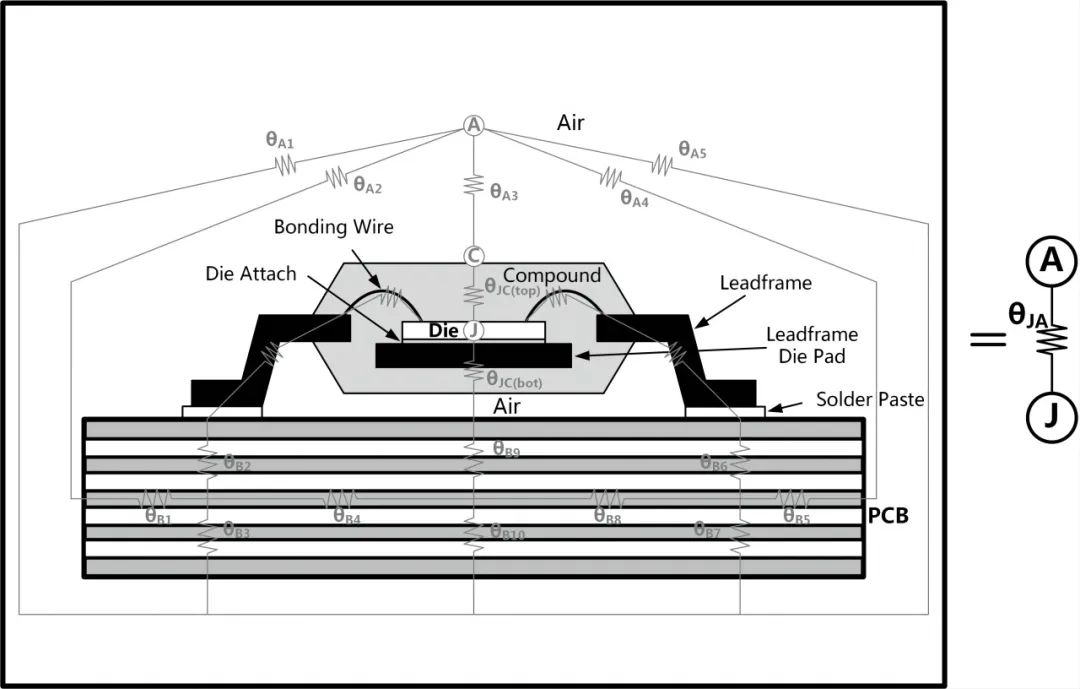

由于芯片结构复杂,通常通过仿真得到热阻的理论计算值。而在芯片实际工程应用中,工程师们将理论热阻与实际应用问题相结合,加以归类,得出一些具有明显物理意义的热阻。下图展示了芯片焊接在PCB上时的热阻网络。

图1 芯片热阻网络

图中,热量从结向上通过封装体传递到封装外壳的顶部,它们之间的热阻之和被称为θJC(top);热量从结向下,通过粘合剂、引线框架基岛传递到底部散热焊盘,其热阻之和被称为θJB;此外,通过图中所有材料和结构,从结到外部环境的所有方向的热量,所有路径的整体热阻被称为θJA。

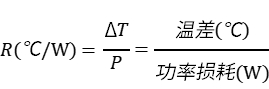

虽然这些热阻可以通过建模仿真获得,但由于存在制造误差及其他原因,可能不甚准确。因此,在工程实践中,通常通过芯片发热和温差,来计算热阻。热阻的定义如下:

(1-1)

这意味着不论是减少芯片的发热、改用散热性能更好的大型封装、增加散热器和风扇,还是改进PCB的散热设计,都可以减少芯片温升。

2

使用热阻矩阵进行热分析

2.1. 对θJA的误解

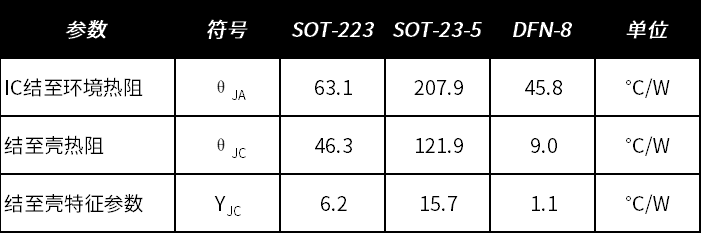

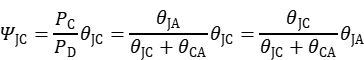

我们可以在芯片的数据手册(datasheet)中找到一个热阻信息矩阵,其中就包含了上述θJA和θJC(top)等参数。下表摘自NSR31系列LDO的数据手册。

表1 NSR31系列的热阻信息

需要注意的是,许多工程师会使用θJA、环境温度和芯片功耗,来计算结温,但这可能会产生较大的计算误差。

从上节图1的θJA定义可以看出,其值不仅由芯片本身决定,还很大程度上取决于具体使用的PCB。不同的应用PCB的散热面积、层数、铜厚、板厚、材料、器件布局等方面各不相同,因此,θJA的值在不同的应用PCB上会有很大差异。大多数工程师都很关注自己PCB上芯片的状态。因此,在热设计中不建议使用θJA,θJA的主要优势在于比较不同封装类型的热性能方面。

通常而言,几乎所有芯片数据手册中的θJA,都是使用行业标准板测量或仿真而得的示例值。这些行业标准平台被称为JEDEC High-K或JEDEC Low-K板。此外,这些JEDEC 板仅由安装在3"x3"板上的一个IC器件组成,与实际工程应用中的PCB有显著差异。

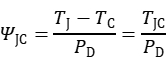

2.2. 理解ΨJC & θJC

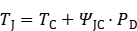

为了解决应用端的实际问题,表中还提供了热特性参数Ψ。这是联合电子器件工程委员会(JEDEC)在20世纪90年代定义的热指标。就评估现代封装器件结温而言,它是一个更为便利的指标。Ψ代表的是结与参考点之间的温差与芯片消耗的总功率的比值,它只是一个构造出的参数。虽然其公式和单位(°C/W)与Rθ非常相似,但Ψ实际上并不是一个“热阻”参数,其定义如下:

(2-1)

其中,ΨJC是结到壳的热特性参数,TJC是结到壳的温差,PD是芯片的总耗散功率。因此,求TJ时,首先要测量外壳温度TC,计算芯片的总耗散功率PD,再使用以下公式计算:

(2-2)

其中,ΨJC可以通过数据手册中的热阻信息矩阵获取。当芯片外部散热条件固定时,ΨJC与θJC成正比。与不同应用端差异很大的θJA相比,虽然ΨJC也受到PCB散热能力的影响,但我们可以近似地认为,在大多数应用中,该影响并不显著。具体原因如下。

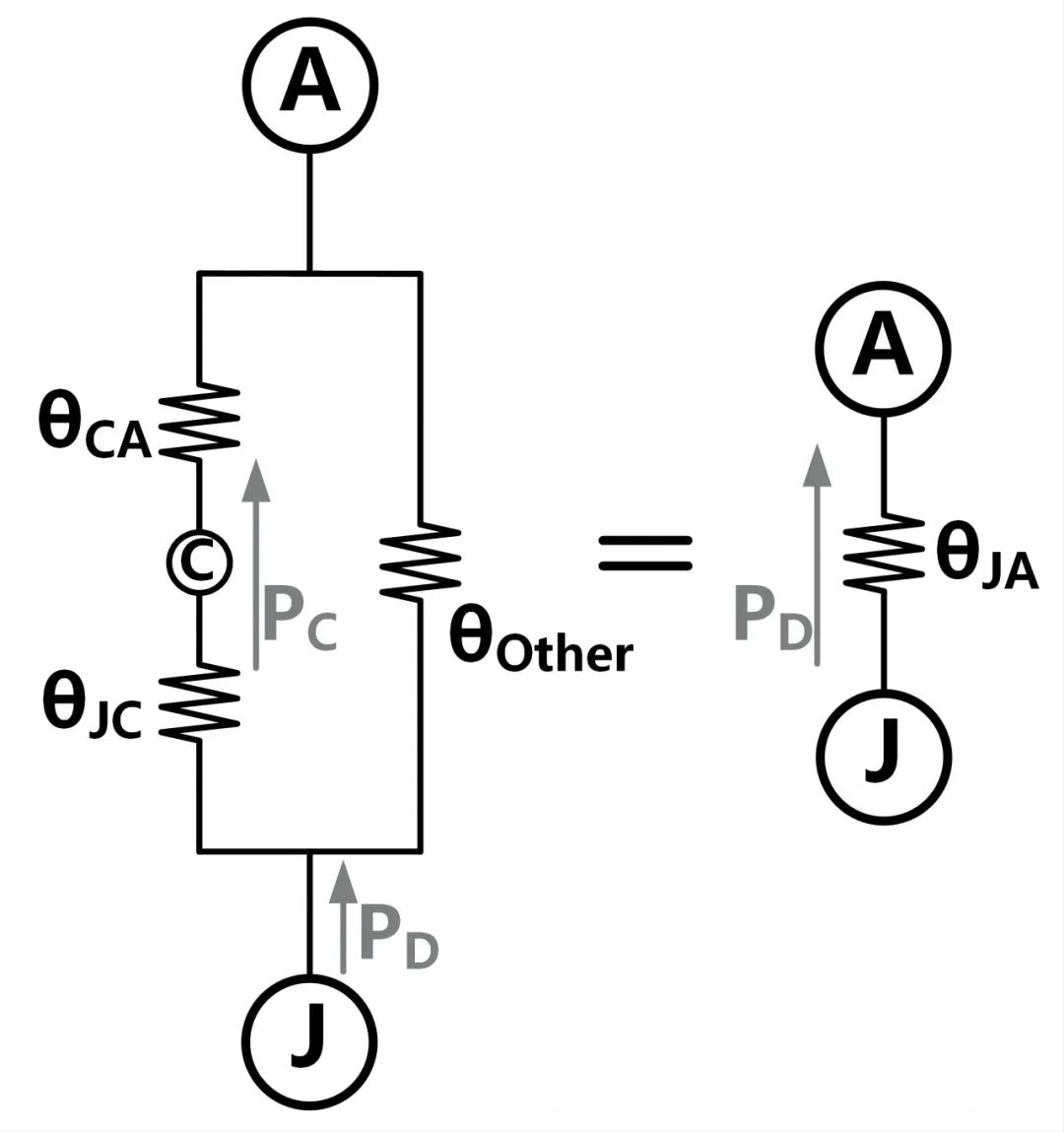

公式(2-2)可以进一步写为:

(2-3)

式中:PC是从结向上通过封装体传递到封装外壳顶部的热功率。由此可得:

(2-4)

即ΨJC与θJA成正比,其值为从结到壳顶部的热功率与芯片总耗散功率的比值。

图 2芯片热阻网络简图

如图2所示,根据热阻网络的“并联电阻分流公式”关系,功率比相当于热阻比的倒数:

(2-5)

式中:θCA为壳到环境的热阻。当没有在芯片表面安装散热器时,θCA远大于θJC。由此可得,ΨJC小于θJA,因此,在工程上的实际PCB中,使用ΨJC估算结温的误差,远小于使用θJA来估算的误差。

3

在EVM 板上进行LDO结温和热阻测试

由于集成电路外部被塑封料(mold compound)包裹,结没有暴露在外,因此我们无法通过热电偶或红外温度计,直接测量芯片内部结点的温度。对于许多大型封装集成电路,例如CPU或GPU,通常会集成一个热传感器,用于测量TJ。但对于小型封装集成电路,由于受到尺寸和成本的限制,大都没有这种TJ传感器的功能。因此,我们必须通过测试和热分析来估算TJ。

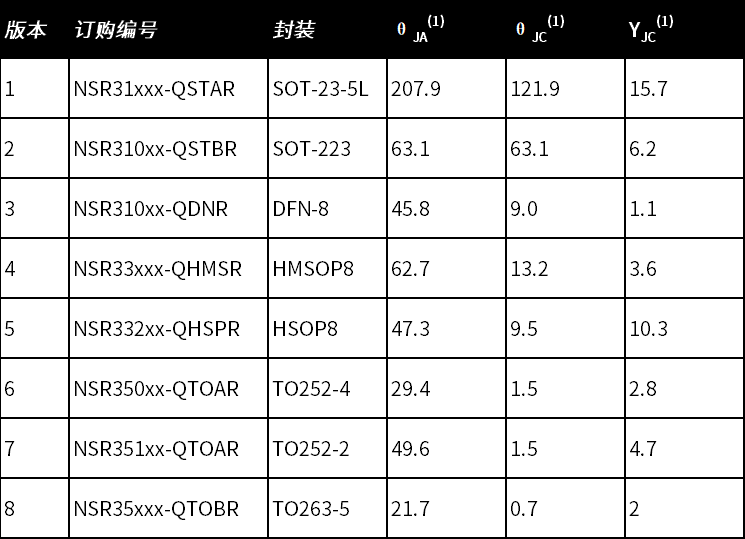

NSR31/33/35系列LDO有8种封装,具体信息如表2所示。采用不同封装的各类热阻已在芯片数据手册的热阻矩阵中标明。其信息概述如下。

表 2 NSR3x 系列的热阻信息

(1) 热数据基于:JEDEC标准高K型材、JESD 51-7、四层板。

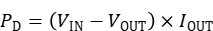

表2中所有参数均根据JEDEC标准获得。通过表θJA比较可知,SOT-23-5L封装的散热性能最差,TO263-5封装的散热性能最好。当需要获取LDO在特定应用电路板上的结温时,可以使用公式(2-2):

(3-1)

式中:VIN代表LDO输入电压,VOUT代表LDO输出电压,IOUT代表LDO输出电流。

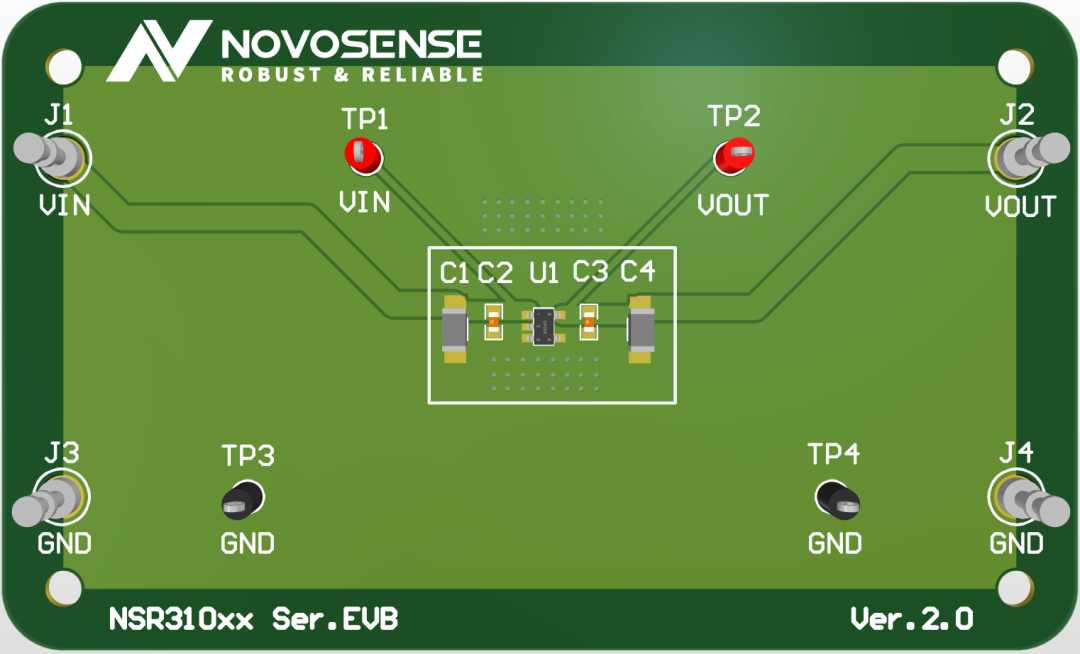

接下来以NSR31050-QSTAR为例,在EVM板上测量和计算其结温和实际热阻θ'JA,以供参考。具体来说,EVM板采用四层设计(88mm x 53mm),铜厚为1盎司,总散热面积约为4600平方毫米,如图3所示。

图3 NSR31050-QSTAR EVM板

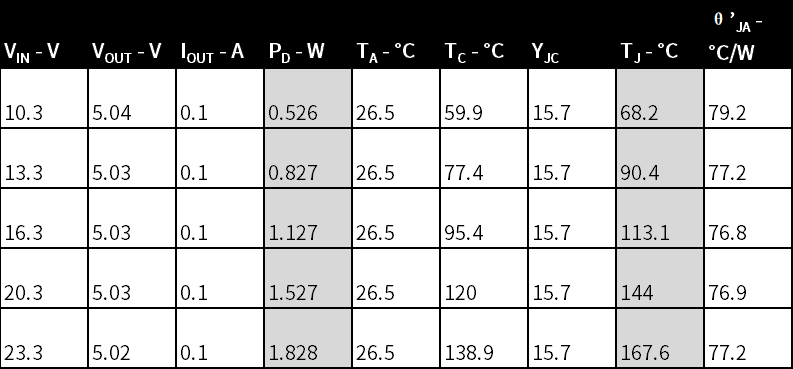

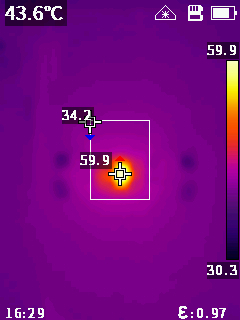

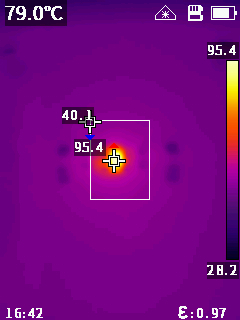

在室温通风恒定的情况下,通过给LDO施加一定的电压和负载,可以将其功耗从0W增加到接近热关断。在不同功耗设置下,让芯片工作5分钟温度稳定后,使用手持式红外测温仪测量芯片顶壳的温度。利用环境温度、壳温、功耗和ΨJC的公式,来对EVM板上芯片的结温和热阻 θ'JA进行估算。结果如表3所示。

表 3 NSR3x系列的热信息

图4 部分壳温的红外测量结果

从表3可以看出,在此EVM板上,测得的结到环境的热阻θ'JA约为 77.5°C/W,远低于JEDEC 标准的207.9°C/W。

综上所述,在实际应用中,芯片存在多种热传导途径,热量亦通过多个通道传递。我们很难像估算总功耗一样,准确得到由特定途径传导的功耗。因此,热特性参数ΨJC更适合用于估算结温,利用热特性参数ΨJC,同时结合公式(3-1)来估算结温更为准确和严谨。

审核编辑:刘清

全部0条评论

快来发表一下你的评论吧 !