瑞萨RZ/T系列MPU

基于Arm的RZ/T系列MPU通过工业以太网通信提供高性能和高速实时控制,为自动化市场构建高性能系统。RZ/T MPU和RZ/N MPU均基于类似的硬件架构开发而成,并共享相同的软件环境,可实现可扩展产品开发。RZ/T系列MPU支持多种协议,例如EtherCAT、PROFINET、Ethernet/IP和下一代TSN。RZ/T MPU配备编码器接口,可支持各种编码器协议。

中断重入的需求

一些客户的应用程序原来是基于其它家私有核的平台,整个程序只使用1个中断,系统的任务全部在这一个中断里管理,比如系统里有125us周期的任务,也有62.5us周期的任务,但是62.5us的任务优先级比125us的任务高,而且125us的任务执行时间超过62.5us。

对于这个时序要求,如果移植到ARM的MCU平台,一般使用两个定时器中断,分别设置不同的优先级来实现,代码架构更简洁清晰。但是客户要求在不改变原有代码结构的前提下,移植到RZ/T2x系列芯片上,要求:使用62.5us的定时器中断,但是当执行到125us的任务时,如果此时又产生了新的定时器中断信号,需要能打断当前正在执行的中断函数。也就是说要求中断的重入。

而对于ARM内核,虽然可以实现中断嵌套的,但是只能是高优先级的中断可以打断低优先级的中断,不能打断同一优先级的中断处理函数,也不能打断自己的中断函数。那么怎么实现这一个需求呢?

中断重入的实现

实现的思路是:在62.5us的高优先级任务执行完后,运行125us的任务前,清除中断控制器的标志,欺骗CPU,当前不是在中断处理函数里,而是在普通的模式下。

下面是代码的实现:

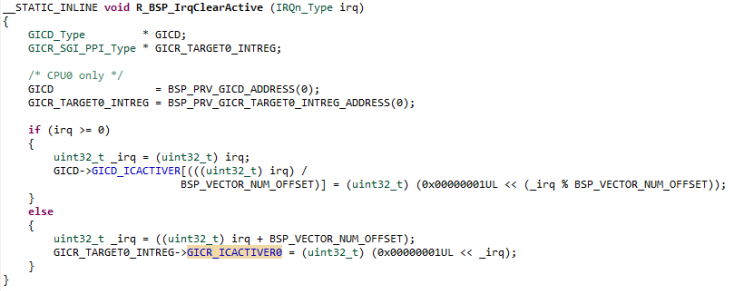

1在bsp_irq.h文件添加如下函数:

左右滑动查看完整内容

长按可保存查看大图

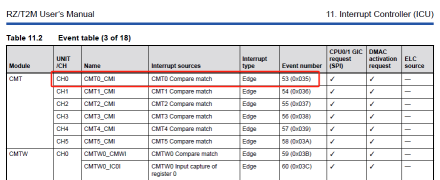

2假设中断使用的是CMT0的比较中断,首先查询手册Interrupt Controller章第3节里的Event Table,CMT0的中断号是53。

3在62.5us执行完后,在可以允许被打断的代码前面,加入如下的处理,清除当前的中断标志,并告诉中断控制器,当前的中断号对应的处理已经结束。这样有新中断信号产生,就可以打断后面的代码。

左右滑动查看完整内容

R_BSP_IrqClearActive(53); // 清除当前中断正在运行的状态 __asm volatile ( " mov r0, # 85 // 85 (=53 + 32) /* Write INTID to EOIR. */ “mcr p15, #0, r0, c12, c12, #1 ” // 当前INT ID写入EOIR寄存器, // 告诉CPU,当前中断处理结束 ):

全部0条评论

快来发表一下你的评论吧 !