应力记忆技术(Stress Memorization Technique, SMT),是一种利用覆盖层Si3N4单轴张应力提高90nm 及以下工艺制程中 NMOS速度的应变硅技术。淀积覆盖层Si3N4薄膜后,通过高温退火把应力传递给源漏和栅极,再通过它们把应力传递到沟道,同时应力会被它们记忆,然后通常酸槽去除应力覆盖层Si3N4薄膜,完成工艺制程后器件表面不会再有覆盖层Si3N4薄膜。

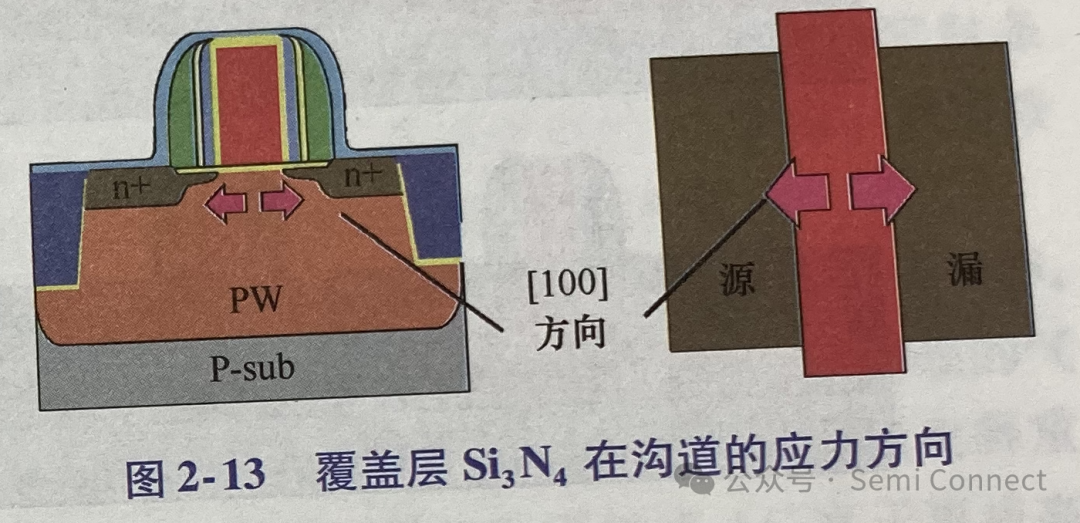

如图2-13所示,覆盖层 Si3N4会在沟道[100]方向产生单轴的张应力,得到的主能谷等能面的轴向都是垂直于沟道方向,沿沟道方向的电子电导有效质量和散射概率都会減小,覆盖层Si3N4可以有效地提高 NMOS的速度。

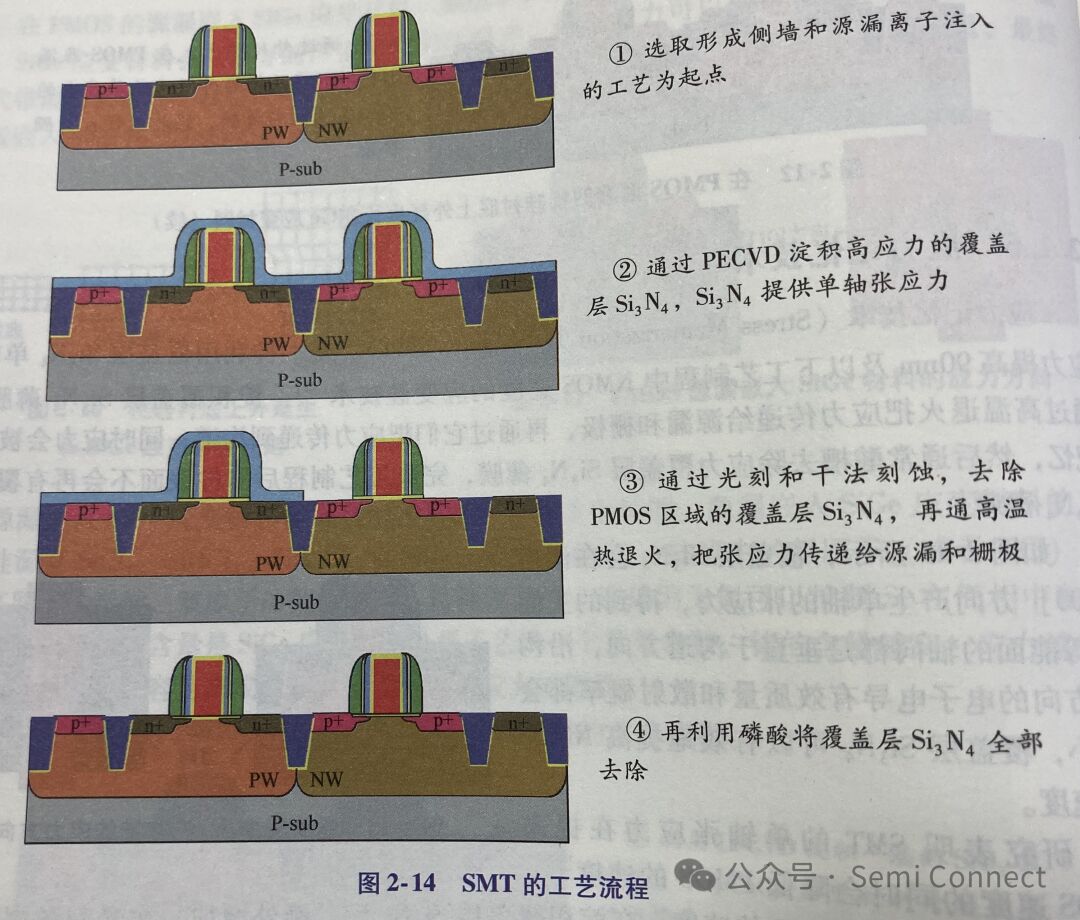

研究表明SMT 的单轴张应力在提高NMOS 速度的同时会降低 PMOS 的速度。为了避免SMT影响PMOS的速度,在淀积覆盖层Si3N4后,额外增加一次光刻和刻蚀去除PMOS 区域的覆盖层Si3N4,再进行高温退火。

SMT是在完成侧墙和源漏离子注入后,通过PECVD淀积一层高应力的覆盖层Si3N4,然后通过一次光刻和干法刻蚀的工艺去除PMOS 区域的覆盖层Si3N4,再通过高温退火过程。在SMT中,高温退火过程是关键,因为纳米级别的器件对热量的预算是非常敏感的,所以高温退火工艺必须采用工艺时间非常短,并且能精确控制工艺时间的快速热退火技术或者毫秒退火技术。高温退火后,再利用磷酸将 Si3N4全部去除。

制备Si3N4薄膜的气体是SiH4、NH3和N2。Si3N4薄膜中也会含有H原子,它主要以Si-H和N-H的形式存在。通过改变H原子的含量可以调节Si3N4薄膜的应力,H原子的含量越高 Si3N4薄膜的应力就越小,可以根据工艺的要求调节淀积Si3N4薄膜工艺的条件来改变Si3N4薄膜中H原子的含量,例如(SiH4+NH3)/N2比例越大,高频电源功率越大,反应温度越低,H原子的含量就越高,那么Si3N4薄膜的应力就越低。

图2-14所示为SMT的工艺流程。

全部0条评论

快来发表一下你的评论吧 !