滞回比较器(Hysteresis Comparator),也称为施密特触发器(Schmitt Trigger)或迟滞比较器,是一种具有特殊功能的比较器电路。与普通比较器不同,滞回比较器在输入信号接近阈值电压时,其输出状态的变化不是瞬间完成的,而是具有一定的滞后性。这种滞后性通过引入正反馈机制实现,可以有效抑制输入信号的噪声干扰,提高系统的稳定性和可靠性。

滞回比较器的阈值电压是指使输出电平发生跳变的输入电压值。由于滞回特性的存在,滞回比较器具有两个阈值电压:上升阈值电压(Vth1)和下降阈值电压(Vth2)。当输入电压从低电平向高电平变化时,达到上升阈值电压时输出由低变高;而当输入电压从高电平向低电平变化时,必须降至下降阈值电压以下,输出才会由高变低。这两个阈值电压的差值即为滞回宽度,它决定了比较器对输入信号噪声的抑制能力。

滞回比较器的阈值电压主要由以下几个设计参数决定:

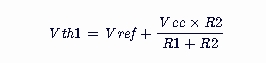

对于同向滞回比较器,其阈值电压的计算公式如下:

这个公式表示当输入电压从低电平向高电平变化时,达到这个电压值时输出会由低变高。

在完成电路设计后,通常需要进行电路仿真来验证比较器的性能是否满足设计要求。仿真过程中可以观察输入电压和输出电压的波形图,确认阈值电压的实际值与计算值是否一致。如果发现偏差较大,需要调整电路参数并重新进行仿真验证。

全部0条评论

快来发表一下你的评论吧 !