本文要点

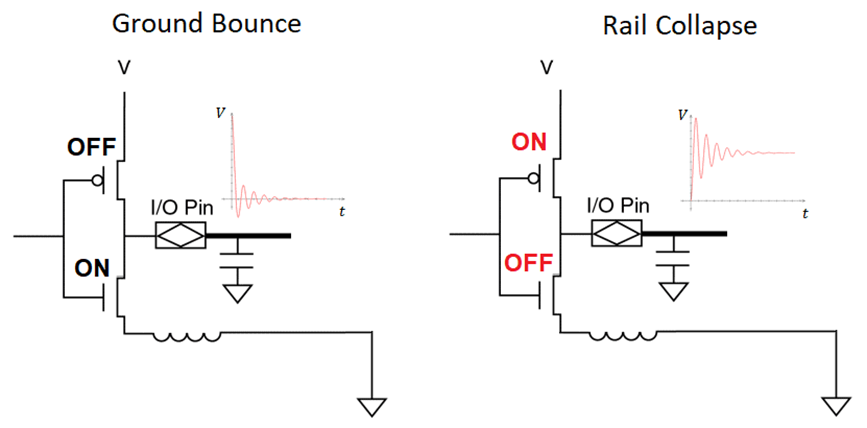

电源分配网络 (PDN) 中的瞬态电流会对电源轨产生两种影响:接地反弹和轨道塌陷。

轨道塌陷和接地反弹是两种瞬态效应,它们对电源完整性具有相同的影响,但产生的方式彼此不同。

通过使用场求解器,设计人员可以根据控制 PDN 瞬态电流的 Z 参数和寄生效应提取 PDN 阻抗。

每当电路或系统状态改变时,就会出现瞬态响应,此时系统会进入一种新的稳定状态。有时,系统中的瞬态响应非常快并且流畅,以至于无法察觉。在其他情况下,瞬态响应表现为信号电平出现大幅波动,这种过渡期间的信号是无法识别的。高速 PCB 设计的一个主要目标是防止不必要的瞬态行为对器件造成影响,以及完全消除瞬态行为。

虽然 PCB 中的直流 PDN 只应输出直流电,但当器件切换状态时,它也会表现出瞬态响应,而瞬态响应会影响连接到 PDN 的所有其他器件的功能。设计人员应了解 PDN 可能出现的瞬态电流变化,以便找到维持 PCB 电源稳定输出的方法。事实证明,设计人员可以通过一些简单的设计选择来确保稳定的电源传输。

PDN 瞬态电流的变化对于了解高速 PCB 的信号完整性非常重要。

1

两种类型的 PCB 瞬态电流

如今的 PCB 使用的是 CMOS 数字器件,当逻辑缓冲器切换状态时,可能会出现两种类型的瞬态电流行为。基本的 CMOS 反相器排列方式是使用两个 MOSFET 连接到一个输入端,单个 CMOS 反相器会根据从关断到接通或从接通到关断的切换情况,表现出两种类型的瞬态响应。具体如下:

1

接地反弹

这是电流进入 PDN 时最常见的瞬态电压效应。发生这种情况时,接地参考平面上会出现电压上升,而 PDN 上的正电压轨则保持不变。

2

轨道塌陷

这种现象被称为 PDN 纹波或电源轨纹波,不要将其与整流交流信号输出端的纹波混淆。当瞬态电流在 PDN 上传播时,PDN 的阻抗会在正电压轨上产生电压波动。

在这两种情况下,都会导致在正电压轨和负 (GND) 电压轨之间测量到的电压出现波动。只需测量设备中电源和接地平面之间的电压(例如使用示波器),就会发现连接到 PDN 的器件出现电压波动。在接地引线或电源引线处可能测量到的基本瞬态效应如下所示。

PDN 瞬态电流变化导致接地反弹和轨道塌陷。

当集成电路中的逻辑电路切换状态时,上述两种效应都取决于 PDN 瞬态电流的变化。在实际的集成电路中,会有许多逻辑电路同时切换,从而产生接地反弹和轨道塌陷的复杂组合。总体而言,这两种效应结合在一起会产生复杂波形,可以在电源轨上测量到。这两种效应的区别在于电流的流向和电流路径中存在的寄生元素。

2

轨道塌陷过程

当正电压供电轨上的瞬态电流进入 PDN 时,就会发生轨道塌陷。可以将 PDN 建模成一个 RLC 网络,与任何具有一定电抗的系统一样,它可以表现出类似于阻尼振荡的瞬态响应。这种效应的整个过程如下:

CMOS 反相器接通并向下游逻辑电路或负载器件供电。

在开关过程中,该器件会使尖峰电流输入电源轨。

电流尖峰是一个宽带信号,与整个 PDN 中的寄生效应发生相互作用。

电流尖峰通过 PDN 阻抗转化为电压尖峰,然后以阻尼振荡的形式放缓。

在步骤 4 中我们可以发现,较高的 PDN 阻抗会导致电源总线上的电压波动过大。此时的解决方案是尽可能降低 PDN 阻抗。为此,需要巧妙地选择去耦电容,并放置相邻的电源/接地平面,以确保较高的平面间电容。

3

接地反弹过程

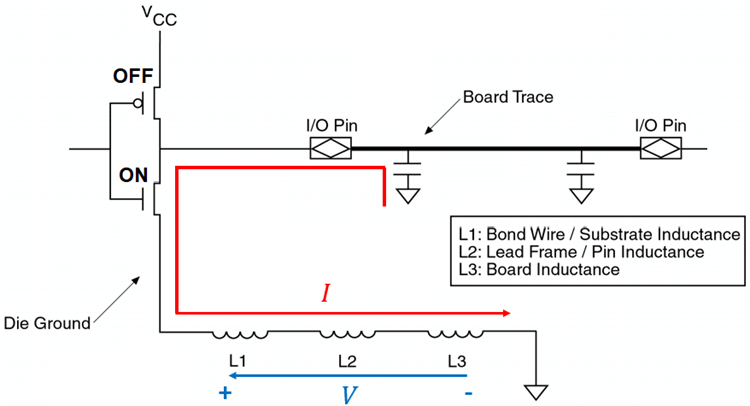

当 CMOS 反相器关断,走线/参考平面电容放电时,就会发生接地反弹。与电流流经 PDN 正极的情况一样,流经集成电路接地端口的电流也会出现各种寄生效应,这些寄生效应也会产生无功阻抗。接地反弹产生电压尖峰的过程如下:

CMOS 反相器的低电压端接通,存储在走线/参考平面电容中的电流放电。

该电流流经集成电路的接地平面,进入集成电路芯片上的连接线。电流从连接线流过集成电路封装上的引脚,再通过一个过孔回到接地平面。

沿 PDN 出现的电压尖峰是由于流向接地的电流路径上的总电感产生了反向电磁场。

然后,该电压尖峰作为阻尼振荡降至零。

通过 CMOS 反相器的 PDN 瞬态电流路径。

此时,接地反弹主要是由接地引线中的电感造成的。当集成电路反复开关时,多个接地反弹尖峰结合在一起,产生能在电源轨上测量到的复杂强迫振荡(见下图)。

由于传输到 CMOS 反相器的驱动信号的上升时间非常快,因而可以测量到电源轨响应(蓝色走线)。

为了减少接地反弹,通常的解决方案是在正负电压轨之间安装一个并联电容器,以减小流动电流的阻抗。该电容是旁路电容;它可降低由接地引线和 CMOS 反相器低电压端的电容所形成的等效 LC 网络的阻抗。此外还可以遵循其他的 PCB layout 设计指南来减少接地反弹。

4

使用场求解器对电压纹波和

瞬态电流进行建模

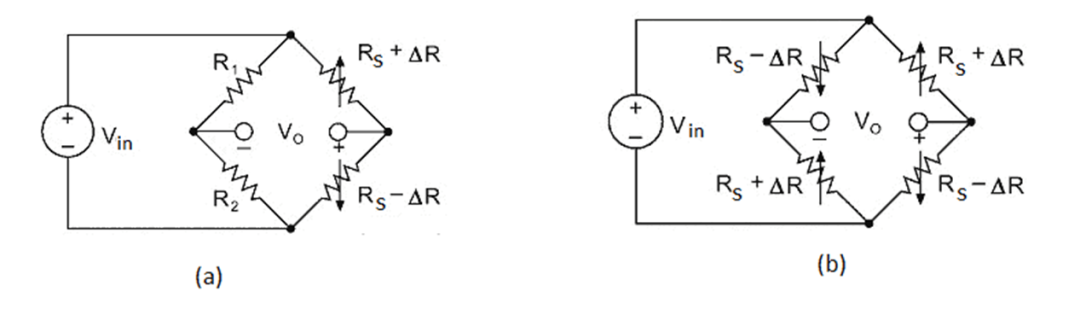

在上述两种情况下,有一点需要注意,PDN 实际上是一个多端口网络。电源轨上的电压不仅会影响开关器件的直流电源,它还会导致 PDN 上所有器件的直流电源产生一些波动。在仿真中,不同端口的阻抗之间的这种关系通过 Z 参数或阻抗参数进行量化。该参数矩阵定义了 PDN 中某个端口的电压波动与 PDN 中所有端口的电流之间的对应关系。

利用高级 PCB 设计工具中的 3D 电磁场求解器,可以提取这些网络参数。如果需要快速提取 Z 参数,最好使用与您的 layout 工具集成的仿真套件;这样无需在另外的仿真工具中重新为 PCB 创建新模型,即可轻松查看 PDN 的哪个部分具有高阻抗。

Cadence Allegro X 软件中集成了 Clarity 3D Solver 工具,这是一款 3D 电磁(EM)仿真软件工具,用于设计 PCB、IC 封装和 IC(SoIC)系统设计的关键互连。Clarity 3D Solver 采用领先的分布式多重运算技术,能够提供近乎无限制的求解容量和 10 倍的求解速度,从而高效解决更庞大、复杂的结构问题。它创建的高精度 S 参数模型,可用于高速信号完整性 (SI)、电源完整性 (PI)、高频射频/微波应用和电磁兼容性 (EMC) 分析,甚至在 112Gbps+ 的数据传输速度上,其仿真结果与实际测量也能高度吻合。更可以根据设计规模的大小,有效匹配可用的计算资源,实现真正的整体 3D 结构设计。

全部0条评论

快来发表一下你的评论吧 !