随着芯片集成度越来越高,随机存储器(random access memory,RAM)在片上系统(system on chip,SoC)中的占比也越来越高,因此RAM对SoC的面积及功耗的贡献也越来越大。相同容量的伪双口RAM(two ports RAM,TP RAM)与单口RAM (single port RAM,SP RAM)相比,前者的面积及功耗更大。降低SoC的面积及功耗可以节省成本,延长芯片寿命并进一步提升市场竞争力。而TP RAM作为RAM的一种常用类型,在SoC中的比重也很大。因此降低TP RAM的面积及功耗,是降低整个SoC面积及功耗的有效途径。

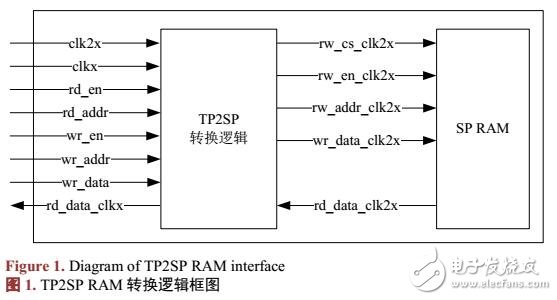

为了降低TP RAM的面积及功耗,提出一种TP RAM的优化设计方法。在TP RAM读写时钟相同的情况下,将TP RAM替换成SP RAM,并在SP RAM外围增加读写接口转换逻辑,优化后的RAM对外接口不变,并可实现原TP RAM的功能。该优化方法可使RAM面积减少24.5%,功耗降低45.16%。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !