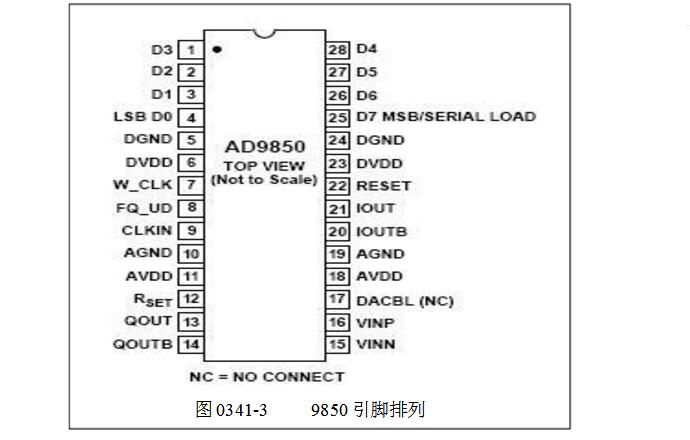

芯片引脚图

AD9850是AD公司生产的最高时钟为125MHz、采用先进的CMOS技术的直接频率合成器,主要由可编程DDS系统、高性能数模变换器(DAC)和高速比较器3部分构成,能实现全数字编程控制的频率合成。

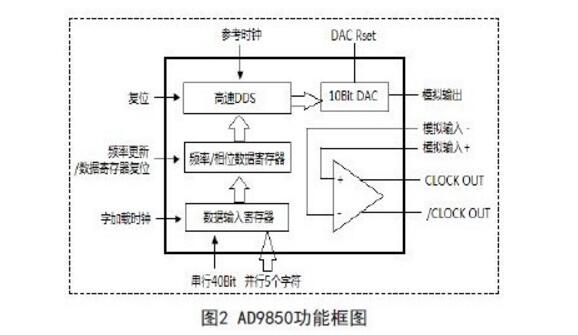

AD9850的芯片功能框图如图2所示。

AD9850芯片内包括高速DDS.10位DAC.频率/相位数据寄存器。数据输入寄存器。比较器等,在125MHz参考时钟下,AD9850经过高速的DDS核心芯片能产生一个32位频率调整控制字可使AD9850的输出频率达0.0291Hz;并能提供了5bits的相位控制位,它能使输出相位以180°.90°.45°.22.5°.11.25°或是它们任意组合的增量改变.AD9850的电路结构允许产生频率值是参考时钟的一半的输出,并且输出的频率能用数控方式以每秒产生23000000个新频率的速度变化.AD9850芯片内的比较器构成能接收经外部低通滤波后的DAC转换输出,可以产生一个低抖动的方波输出的装置,因此AD9850用作时钟发生器十分方便。频率/相位数据寄存器。数据输入寄存器在外部的频率更新时钟和字加载时钟的控制下进行频率控制字的输入和更新,使芯片输出所要求的频率和相位.

AD9850内含可编程DDS系统和高速比较器,可实现全数字编程控制的频率合成。

可编程DDS系统由相位累加器和正弦查表组成,其相位累加器由一个加法器和一个N位的相位寄存器组成,N一般为24~32;实质上是一个可变模的计数器,即DDS相位增量的个数在计数器收到每一个时钟脉冲时被存储起来,当计数器溢出时,它就回到初态并使用相位累加器输出到相邻值。频率控制字能设置计数器的模,它决定了相位增量的大小。相位增量在每个时钟到来时便在相位累加器中相加,相位增量越大,则累加器溢出的速度越快,产生的输出频率越高。

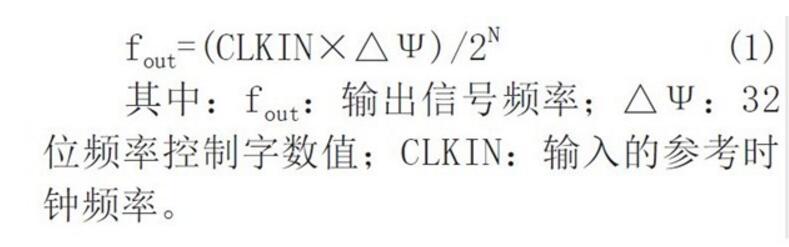

AD9850采用32位的相位累加器,AD9850利用改进的,独有的算法,把14bits已截断的相位累加器的输出转变成适当的余弦值,经片内高速的10bitDAC转换器,可得到模拟正弦波。这个独特的算法使用一个简化了的ROM表和DSP技术等功能,有助于缩小AD9850的体积和功耗。输入。输出。参考时钟和频率控制字的关系如下:

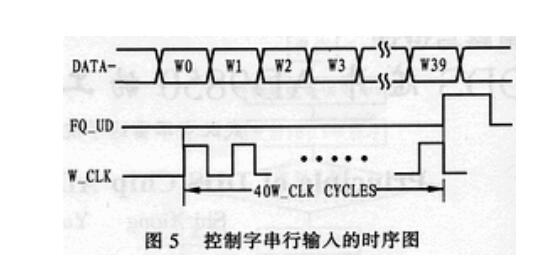

AD9850有40位控制字,32位用于频率控制,5位用于相位控制。1位用于电源休眠(Powerdown)控制,2位用于选择工作方式。这40位控制字可通过并行方式或串行方式输入到AD9850,图4是控制字并行输入的控制时序图,在并行装入方式中,通过8位总线A0…D7将可数据输入到寄存器,在重复5次之后再在FQ-UD上升沿把40位数据从输入寄存器装入到频率/相位数据寄存器(更新DDS输出频率和相位),同时把地址指针复位到第一个输入寄存器。接着在W-CLK的上升沿装入8位数据,并把指针指向下一个输入寄存器,连续5个W-CLK上升沿后,W-CLK的边沿就不再起作用,直到复位信号或FQ-UD上升沿把地址指针复位到第一个寄存器。在串行输入方式,W-CLK上升沿把25引脚的一位数据串行移入,当移动40位后,用一个FQ-UD脉冲即可更新输出频率和相位。图5是相应的控制字串行输入的控制时序图。

AD9850的复位(RESET)信号为高电平有效,且脉冲宽度不小于5个参考时钟周期。AD9850的参考时钟频率一般远高于单片机的时钟频率,因此AD9850的复位(RESET)端可与单片机的复位端直接相连。

值得一提的是:用于选择工作方式的两个控制位,无论并行还是串行最好都写成00,并行时的10、01和串行时的10、01、11都是工厂测试用的保留控制字,不慎使用可能导致难以预料的后果。

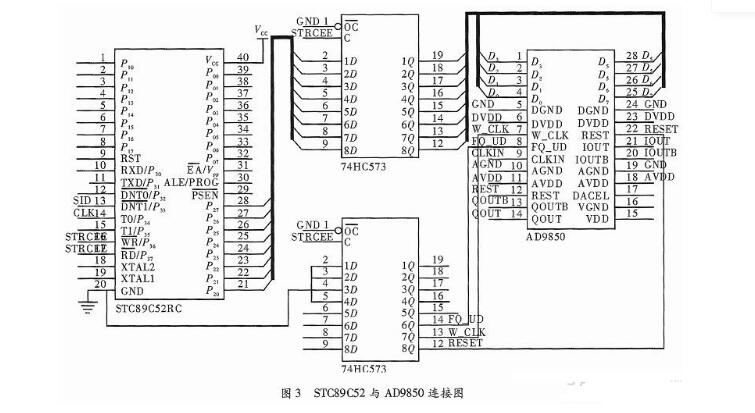

AD9850的40位频率/相位控制字可通过并行或串行两种方式送入器件。选用并行传输方式,充分发挥芯片AD9850的高速性能。在并行方式下连续输入 5次数据,每次输入8位(1 Byte),将40位频率/相位控制字送入器件。系统中,单片机通过数据锁存器和控制锁存器来实现对AD9850模块的控制,数据锁存器打开时,控制锁存器关闭,此时传输数据;控制锁存器打开时,数据锁存器关闭,此时根据AD9850的时序对W_CLK、FQ_UD、RESET执行相应的操作。单片机 89C52控制AD9850工作连线图,如图3所示。

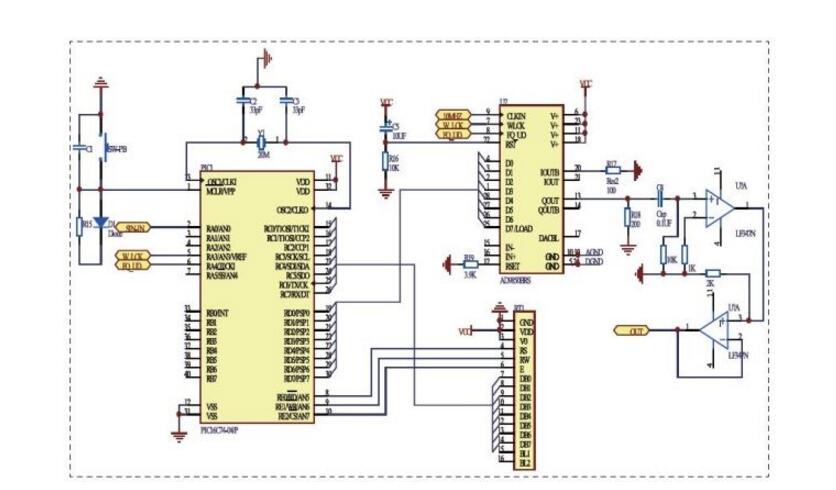

总线方式并行接口占用的单片机资源较少,而且本设计中信号发生器只是作为单片机控制模块的外围扩展模块之一,因此AD9850工作在控制字并行输入方式。此时,AD9850仅作为一扩展芯片只占用一个地址。其原理图如图4所示。

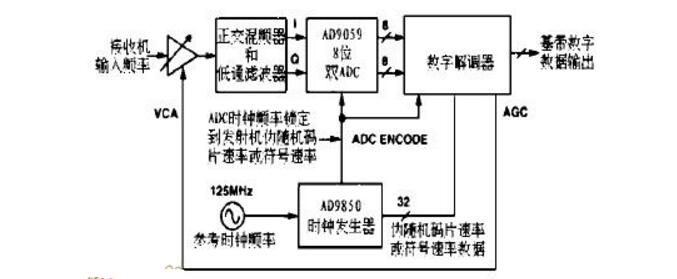

AD9850 时钟发生器在扩频接收器中的应用

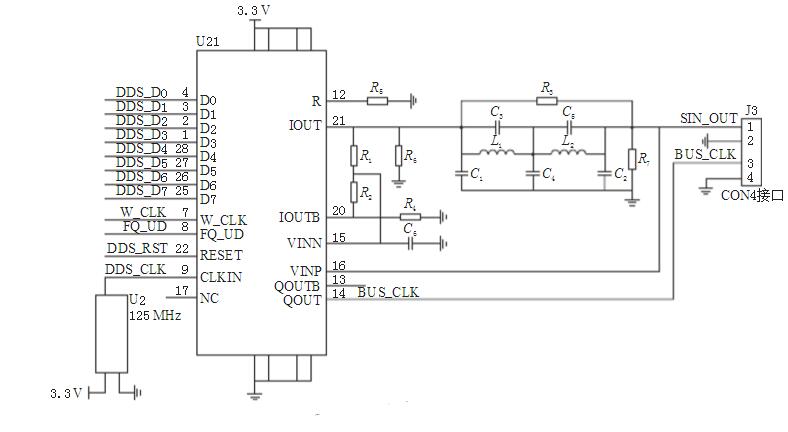

AD9850是美国AD公司生产的高集成度的DDS合成芯片。它采用32位相位累加器,截断成14位,输入正弦查询表,查询表输出截断成10位,输入到DAC。DAC输出两个互补的模拟电流,接到滤波器上。但是AD9850直接产生的信号幅度只有2V左右,而且是单极性的。而测试的时候需要的是双极性的正弦信号,因此DDS输出的信号还要经过隔直和放大。AD9850输出的信号经过RC高通滤波器,将直流分量滤除,输出交流信号,再经放大器放大,电压跟随,输出幅度适当、带载能力较强的信号源。电路如图所示。

全部0条评论

快来发表一下你的评论吧 !